(Gesture Recognition Interface Device)

Pamela Garcia

Evanis Cruz

Martin Rodriguez

Landon Splitter

## **Table of Contents**

|                                               |    |

|-----------------------------------------------|----|

| 1.0 Executive Summary                         | 1  |

| 2.0 Project Description                       | 1  |

| 2.1. Motivation and Goals                     | 1  |

| 2.2. Objectives                               | 2  |

| 2.3. Project Requirements and Specifications  | 3  |

| 3.0 Project Research                          | 3  |

| 3.1. Image Processing                         | 3  |

| 3.1.1. Overview                               | 3  |

| 3.1.2. Object Tracking                        | 3  |

| 3.1.3. Image Processing System                | 4  |

| 3.1.4. Image Acquisition                      | 5  |

| 3.1.4.1. Frame Generation                     | 5  |

| 3.1.4.2. Image Recognition Algorithm          | 5  |

| 3.1.5. Object Tracking Algorithm              | 7  |

| 3.1.6. Wii IR Camera System                   | 8  |

| 3.2. LEDs                                     | 9  |

| 3.2.1. Wavelength                             | 9  |

| 3.2.2. Viewing Angle                          | 10 |

| 3.3. Camera                                   | 11 |

| 3.3.1. CMOS vs. CCD                           | 11 |

| 3.3.2. Resolution                             | 12 |

| 3.3.3. Frame Rate                             | 12 |

| 3.3.4. Spectral response                      | 13 |

| 3.3.5. Visible Light Filter                   | 14 |

| 3.4. FPGA vs. DSP                             | 16 |

| 3.4.1. Overview                               | 16 |

| 3.4.2. Performance                            | 16 |

| 3.4.3. Cost                                   | 17 |

| 3.4.4. Development Software                   | 17 |

| 3.4.5. Power Consumption                      | 18 |

| 3.4.6. Form Factor and Size                   | 18 |

| 3.4.7. Conclusion                             | 18 |

| 3.5. FPGA Development Software                | 19 |

| 3.5.1. HDL Overview                           | 19 |

| 3.5.2. VHDL                                   | 19 |

| 3.5.3. Verilog                                | 20 |

| 3.5.4. HDL code generators                    | 20 |

| 3.5.4.1. Simulink: HDL coder and HDL Verifier | 20 |

| 3.5.4.2. Labview FPGA Module                  | 22 |

| 3.6. FPGA Chip                                | 23 |

| 3.6.1. Overview                               | 23 |

| 3.6.2. Architecture of a Chip                 | 24 |

| 3.6.3. Xilinx Chip                            | 27 |

| 3.6.4. Altera Chip                            | 29 |

| 3.6.5. Conclusion                             | 30 |

| 3.7. FPGA Power Supply                        | 30 |

| 3.7.1. Overview                               | 30 |

|                                                  |    |

|--------------------------------------------------|----|

| 3.7.2. Output Voltage Requirements               | 30 |

| 3.8. Microcontrollers                            | 32 |

| 3.8.1. Overview                                  | 32 |

| 3.8.2. Limitations                               | 32 |

| 3.8.3. Advantages                                | 33 |

| 3.8.4. The MSP430G2553                           | 35 |

| 3.8.4.1. Development Software                    | 37 |

| 3.8.4.2. Device Features                         | 37 |

| 3.8.5. Arduino Uno                               | 37 |

| 3.9. Power Supply                                | 37 |

| 3.9.1. Overview                                  | 37 |

| 3.9.2. Power Options                             | 39 |

| 3.9.3. Linear regulator                          | 42 |

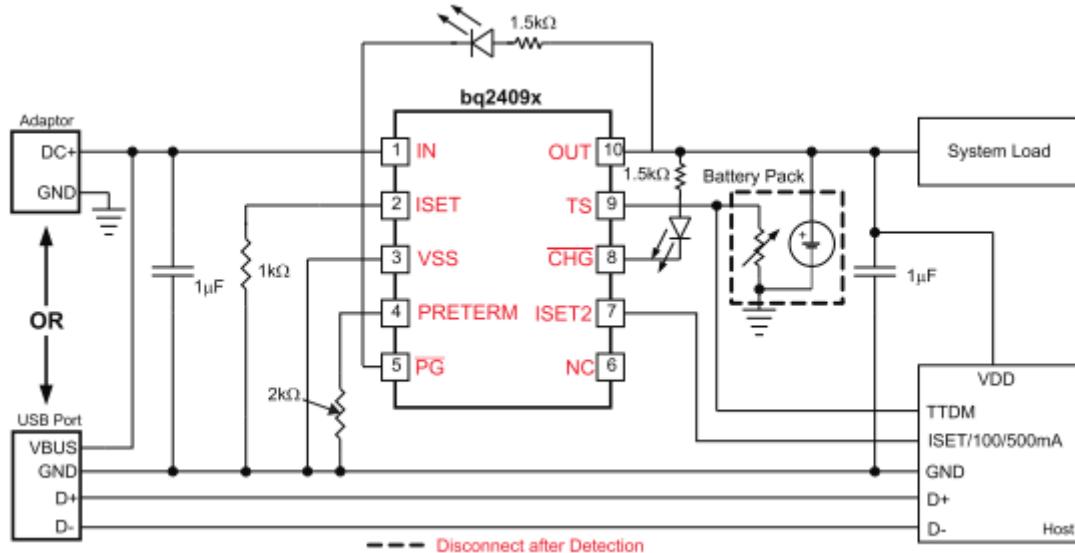

| 3.9.4. Recharge Circuitry                        | 43 |

| 3.9.5. Battery Charger                           | 45 |

| 3.9.6. Buck-Boost DC/DC Converter                | 45 |

| 3.9.7. Charge Pump DC/DC Converter               | 46 |

| 3.10. Bluetooth Module                           | 46 |

| 3.10.1. Overview                                 | 46 |

| 3.10.2. Bluetooth Modules                        | 47 |

| 3.10.3. RS232TTL Transceiver Module              | 47 |

| 3.10.3.1. Board Schematics                       | 48 |

| 3.11. PCB                                        | 49 |

| 3.11.1. Express PCB                              | 50 |

| 3.11.2. PCB4Less                                 | 50 |

| 3.11.3. PCB Express                              | 50 |

| 3.11.4. Ultimate PCB                             | 51 |

| 3.11.5. Imagineering Inc.                        | 51 |

| 3.11.6. 4PCB.com                                 | 51 |

| 3.12. Host Computer                              | 52 |

| 3.12.1. Drivers                                  | 52 |

| 3.12.2. Integration                              | 52 |

| 3.13. Gesture Recognition Data Acquisition       | 53 |

| 3.13.1. Overview                                 | 53 |

| 3.13.2. Accelerometers                           | 54 |

| 3.13.2.1. MMA8452Q Accelerometer                 | 56 |

| 3.13.3. Gyroscopes                               | 57 |

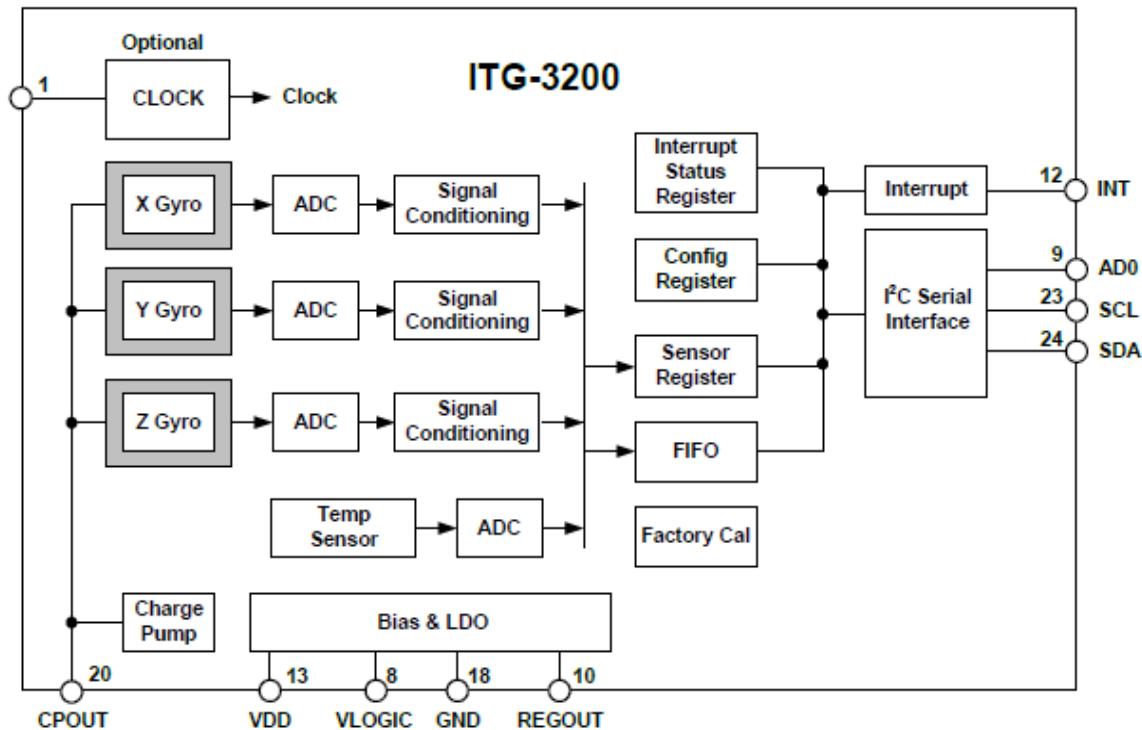

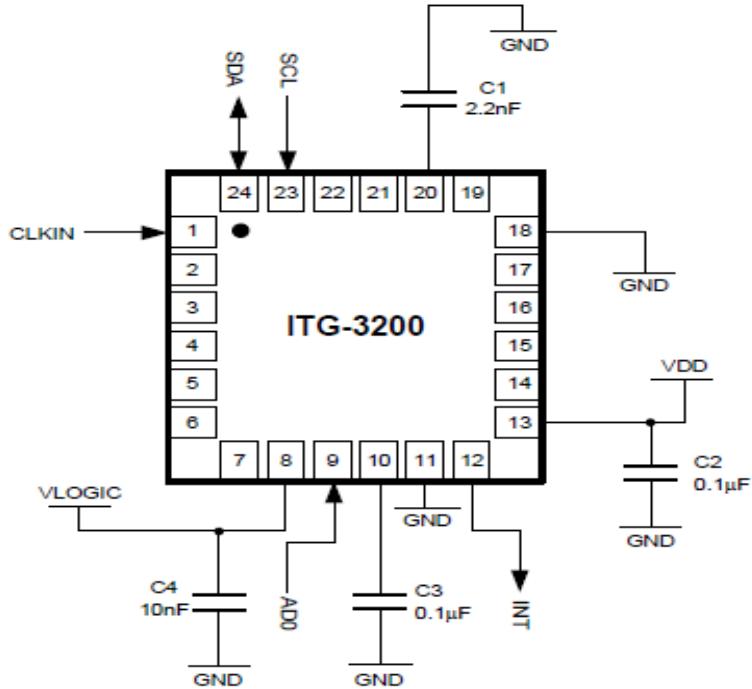

| 3.13.3.1. ITG-3200 Digital Gyroscope             | 58 |

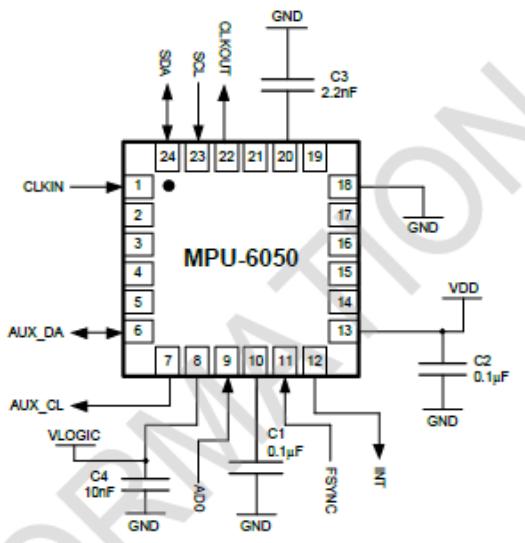

| 3.13.3.2. MPU 6050                               | 60 |

| 3.14. Communication Protocols                    | 61 |

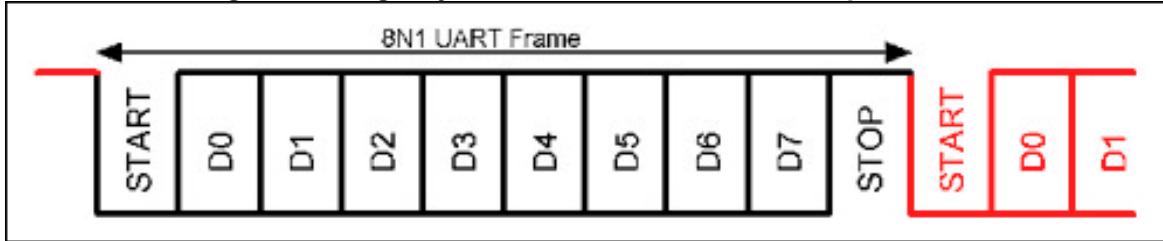

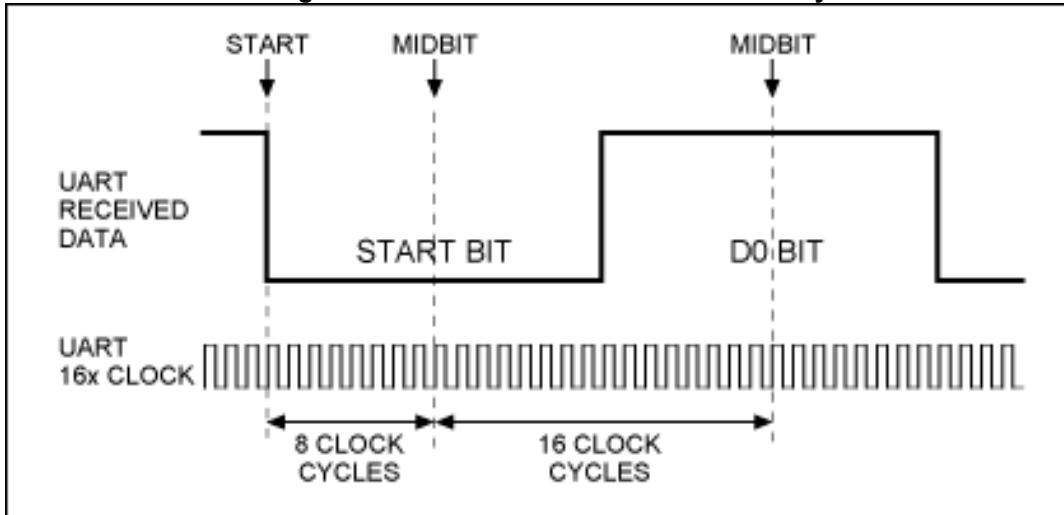

| 3.14.1. The UART protocol                        | 61 |

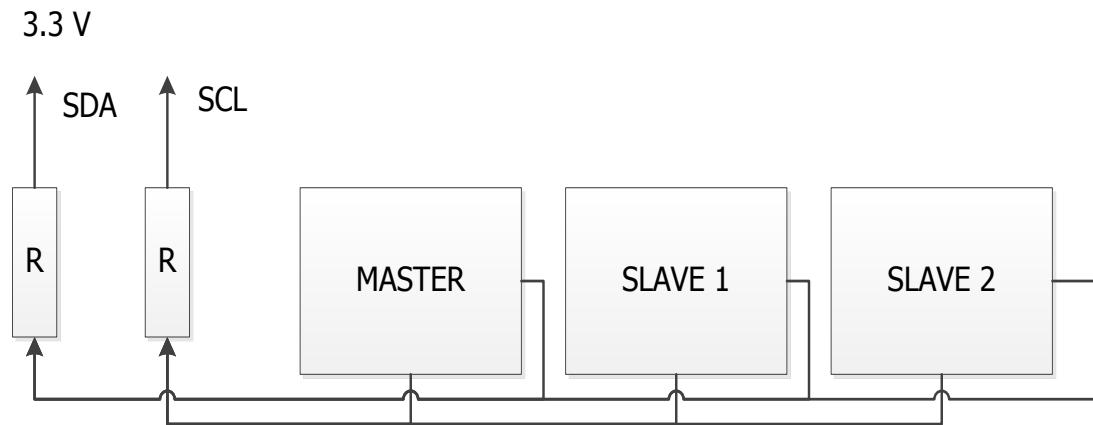

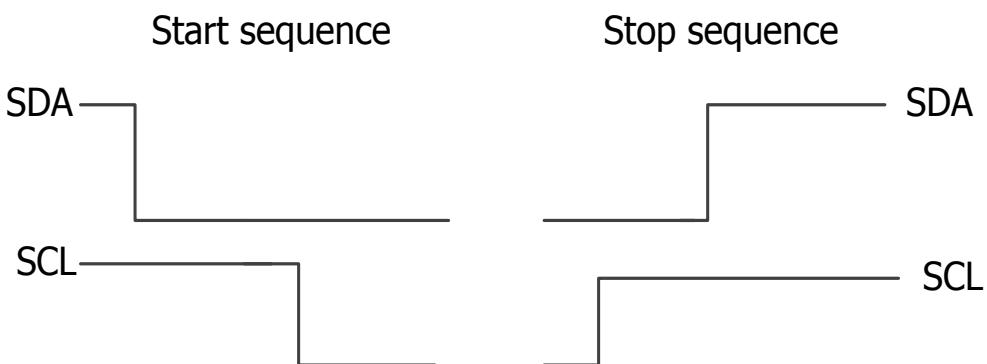

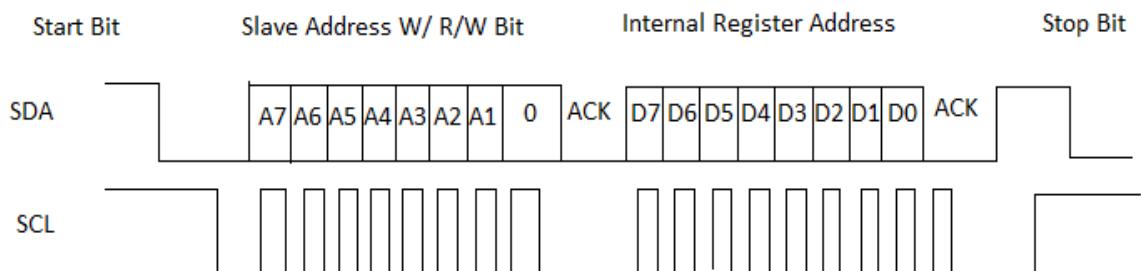

| 3.14.2. The I <sup>2</sup> C Protocol            | 63 |

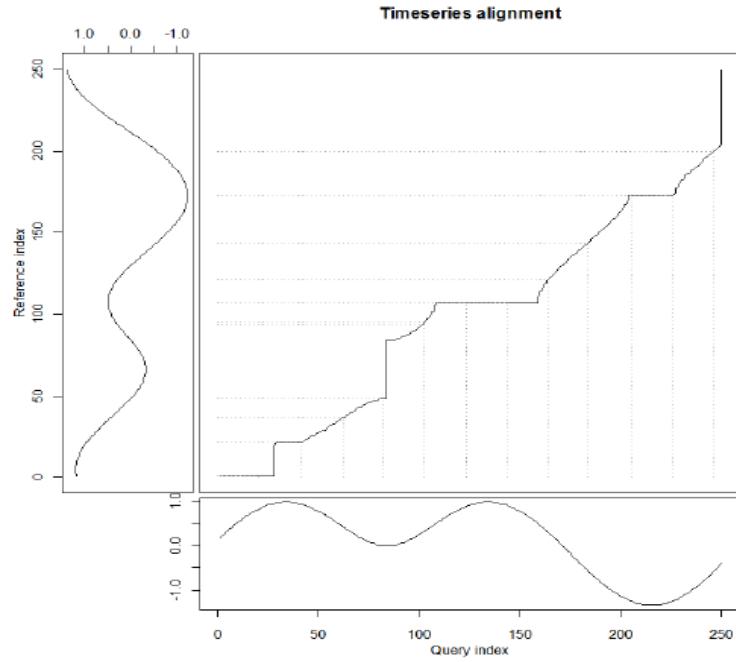

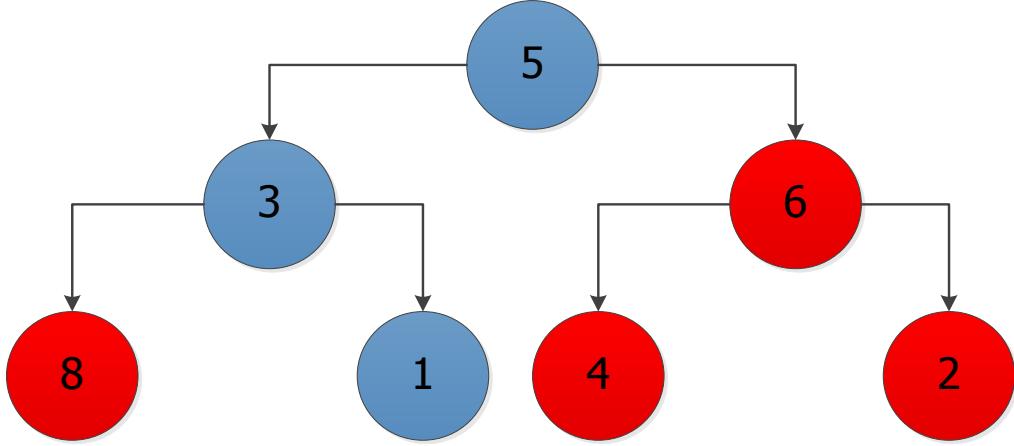

| 3.15. Gesture Recognition Algorithm              | 65 |

| 3.15.1. Dynamic Time Warping                     | 66 |

| 3.15.2. The Greedy Algorithm                     | 68 |

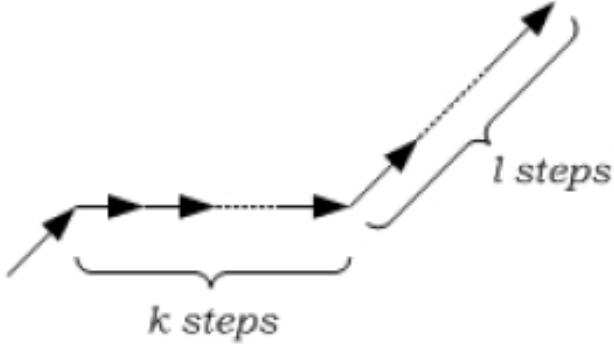

| 3.15.3. DTW Optimization                         | 69 |

| 3.15.4. Step Function (Slope Constraints)        | 69 |

| 3.15.5. Weighting                                | 70 |

| 3.15.6. Global Path Constraints                  | 70 |

| 4.0 Project Hardware and Software Design Details | 71 |

|                                             |     |

|---------------------------------------------|-----|

| 4.1. Camera                                 | 71  |

| 4.1.1. Extracting the camera module         | 71  |

| 4.2. Microcontroller                        | 72  |

| 4.2.1. Program Overview                     | 72  |

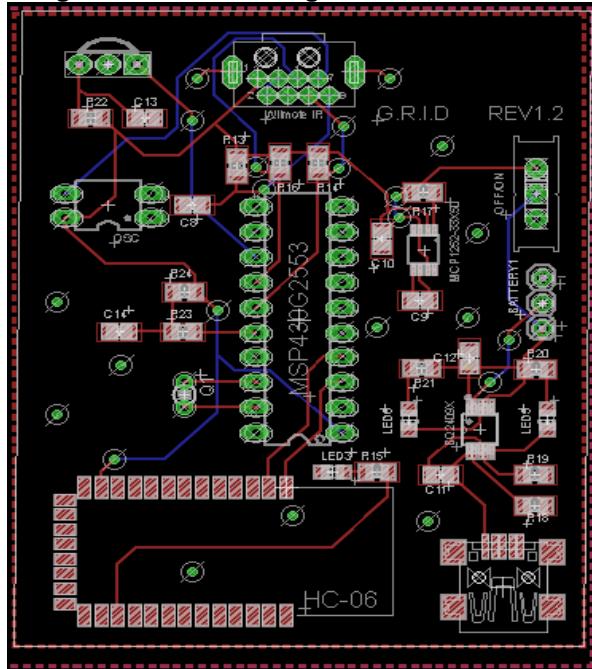

| 4.2.2. Power Supply Design                  | 73  |

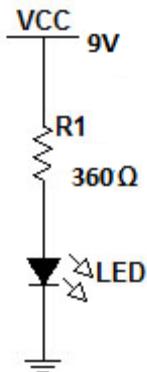

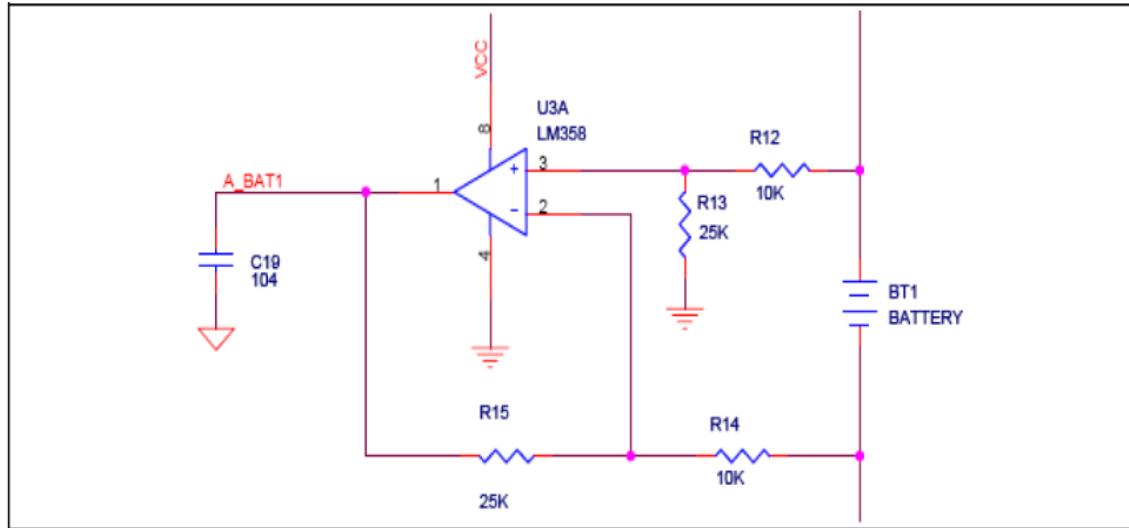

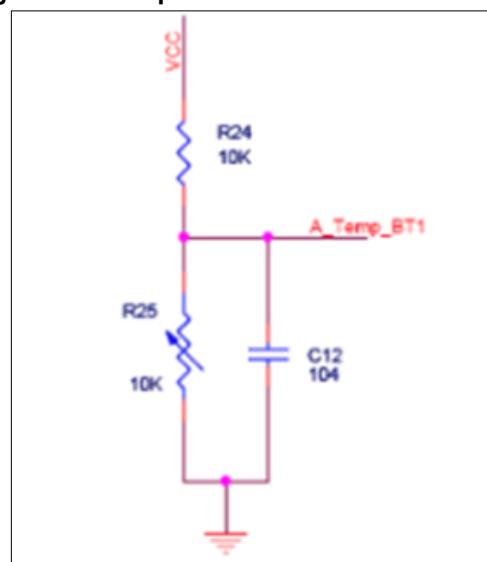

| 4.2.2.1. LED Indicator                      | 75  |

| 4.3. Microprocessor                         | 75  |

| 4.3.1. Design Tools                         | 75  |

| 4.3.1.1. Development Board                  | 75  |

| 4.3.1.2. Development Language               | 76  |

| 4.3.2. MSP 430 Design                       | 76  |

| 4.3.2.1. Operation Procedure                | 76  |

| 4.3.2.2. Camera PCB                         | 76  |

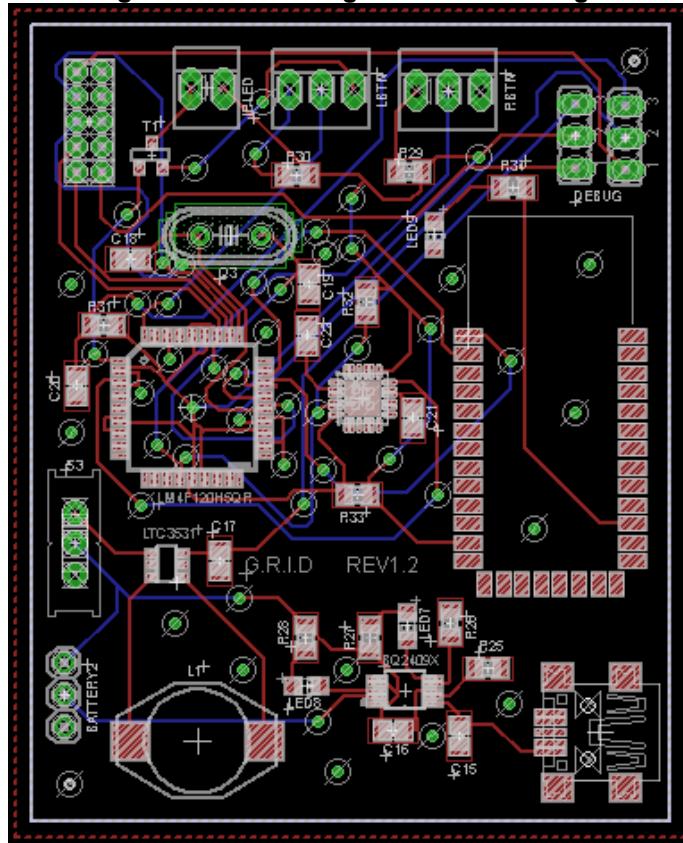

| 4.3.3. Stellaris Design                     | 78  |

| 4.3.3.1.1. Operation Procedure              | 78  |

| 4.3.3.1.2. Glove PCB                        | 78  |

| 4.4. Image Processing Algorithms            | 80  |

| 4.5. Aesthetics                             | 80  |

| 4.5.1. Glove and Mount                      | 80  |

| 4.6. Software                               | 82  |

| 4.6.1. Overview                             | 82  |

| 4.6.2. Functional Requirements              | 83  |

| 4.6.3. Non- Functional Requirements         | 85  |

| 4.7. Device Driver                          | 86  |

| 4.7.1. Overview                             | 86  |

| 4.8. Gesture Library                        | 89  |

| 4.8.1. Overview                             | 89  |

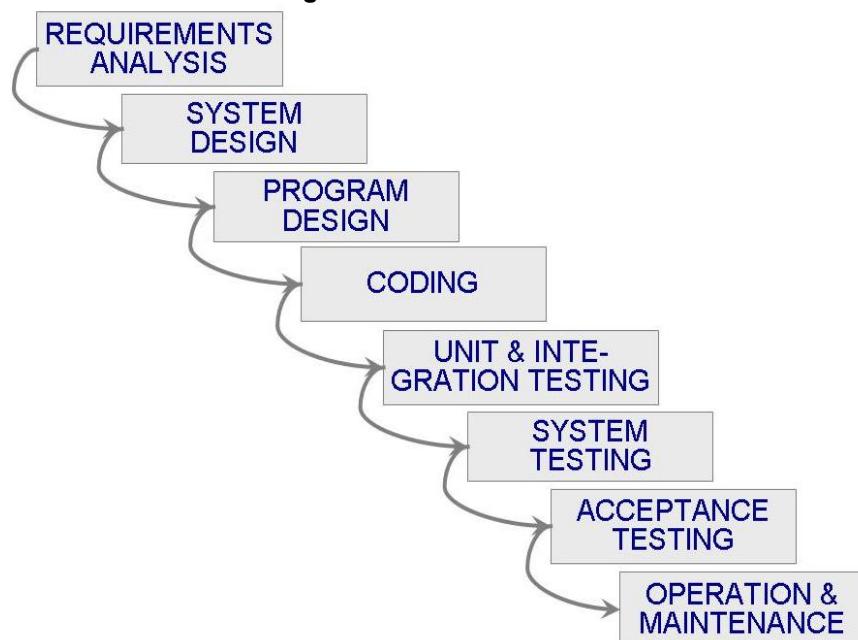

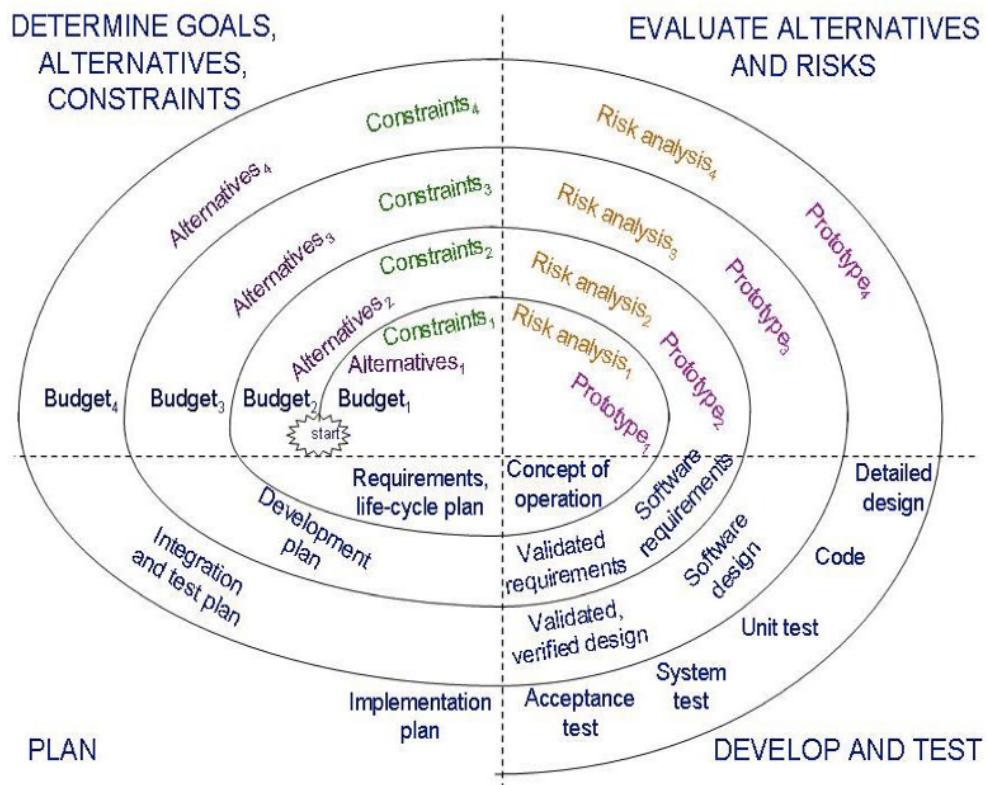

| 5.0 Design Summary of Hardware and Software | 95  |

| 6.0 Project Prototype Testing               | 95  |

| 6.1. Hardware Test Environment              | 95  |

| 6.1.1. Temperature                          | 95  |

| 6.1.2. ESD Safety                           | 96  |

| 6.1.3. Lighting                             | 96  |

| 6.2. Hardware Specific Testing              | 96  |

| 6.2.1. Camera                               | 96  |

| 6.2.2. LEDs                                 | 96  |

| 6.2.3. Visible Light Filter                 | 97  |

| 6.2.4. Microcontroller                      | 98  |

| 6.2.5. Power Circuit                        | 99  |

| 6.2.5.1. Battery Voltage                    | 99  |

| 6.2.5.2. Temperature                        | 99  |

| 6.2.6. Glove and Mount                      | 100 |

| 6.3. Software Testing Environment           | 101 |

| 6.4. Software Testing                       | 102 |

| 6.4.1. Image Recognition                    | 108 |

| 7.0 Administrative Content                  | 109 |

| 7.1. Budget and Finance                     | 109 |

|            |                                |     |

|------------|--------------------------------|-----|

| 7.2.       | Milestone Chart                | 111 |

| 7.3.       | Work Distribution              | 113 |

| 8.0        | Product Operation              | 114 |

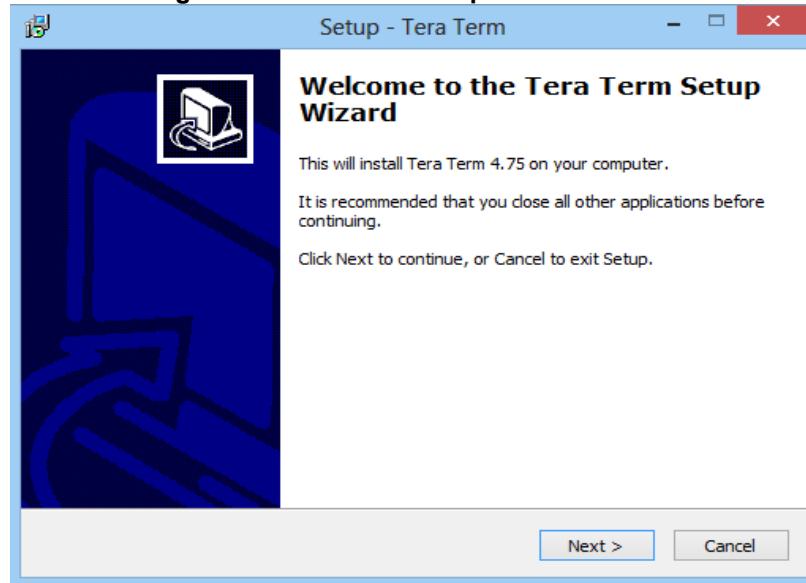

| 8.1.       | Prerequisites                  | 114 |

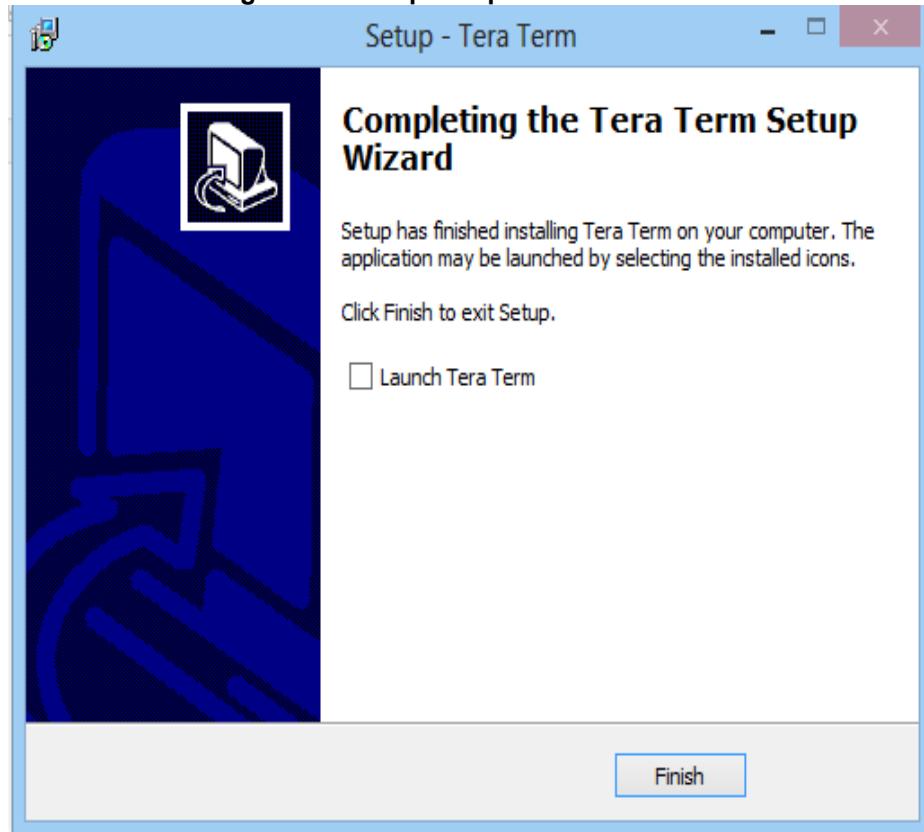

| 8.2.       | Installing a Terminal Program  | 114 |

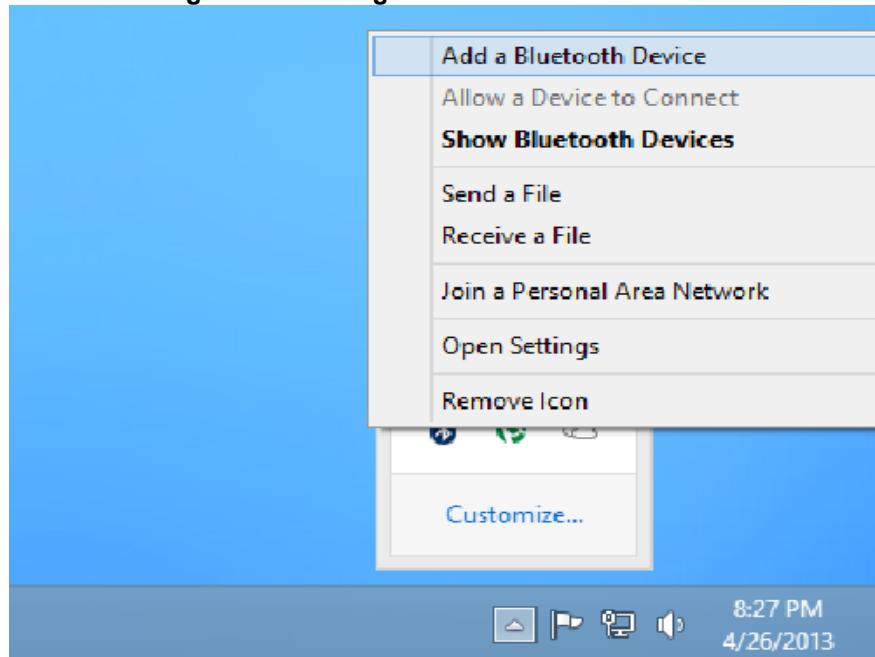

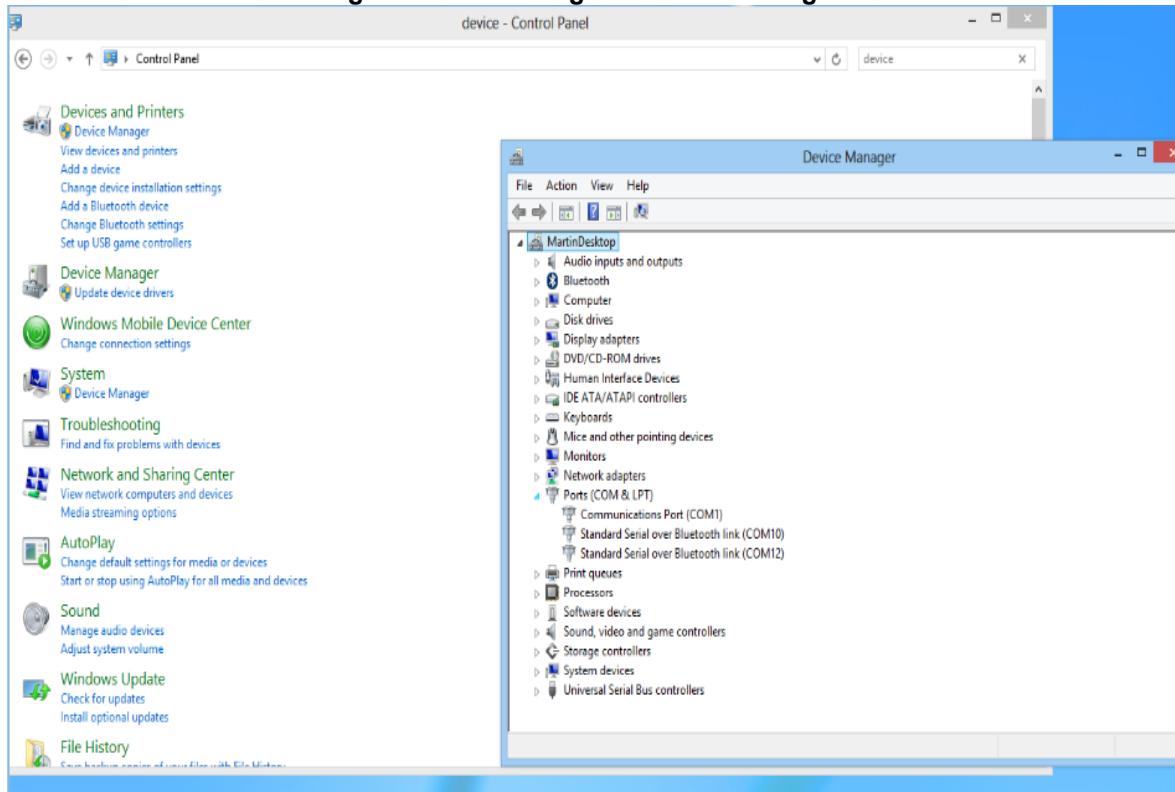

| 8.3.       | Connecting to the Glove/Camera | 115 |

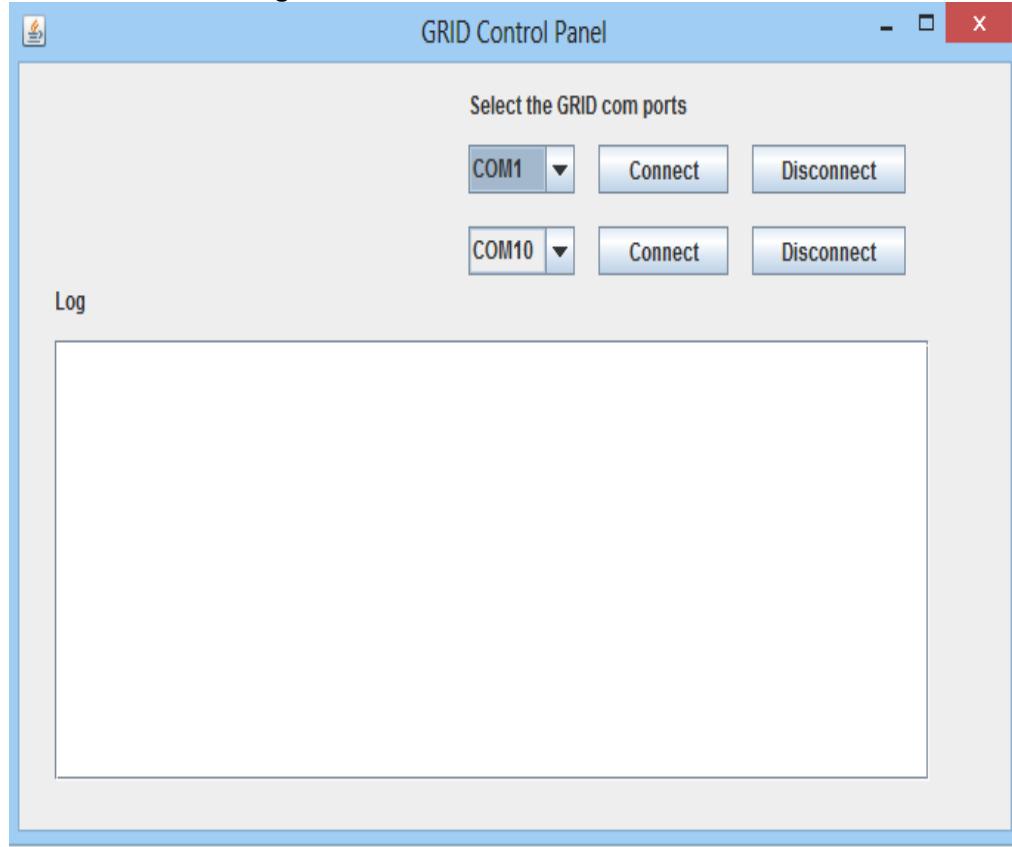

| 8.4.       | Running the Driver Program     | 118 |

| 8.5.       | Using the Gesture Library      | 119 |

| 8.6.       | Charging the Battery           | 120 |

| Appendices |                                | 121 |

|            | Appendix A – Permissions       | 121 |

|            | Appendix B - Works Cited       | 125 |

|            | Appendix C - Table of Tables   | 128 |

|            | Appendix D- Table of Figures   | 128 |

## 1.0 Executive Summary

In the past few decades' technology has made some great improvements in the use and operation of personal and commercial computing devices. In fact the growth in the realm of technology has been better than any other field. With these improvements much has changed in what and how much people are able to do on a personal PC. The only thing that has remained relatively the same over all these changes is the control device for these personal machines. For the most part the mouse has not changed too much from the way it has been in the past. It has improved in the fact that it is more sleek or easier to use, faster in the response or better fitting so the user does not hurt them with extended use. Although these improvements are great it still remains that, if you've seen one mouse, you've pretty much seen them all. Well GRID is here to change that.

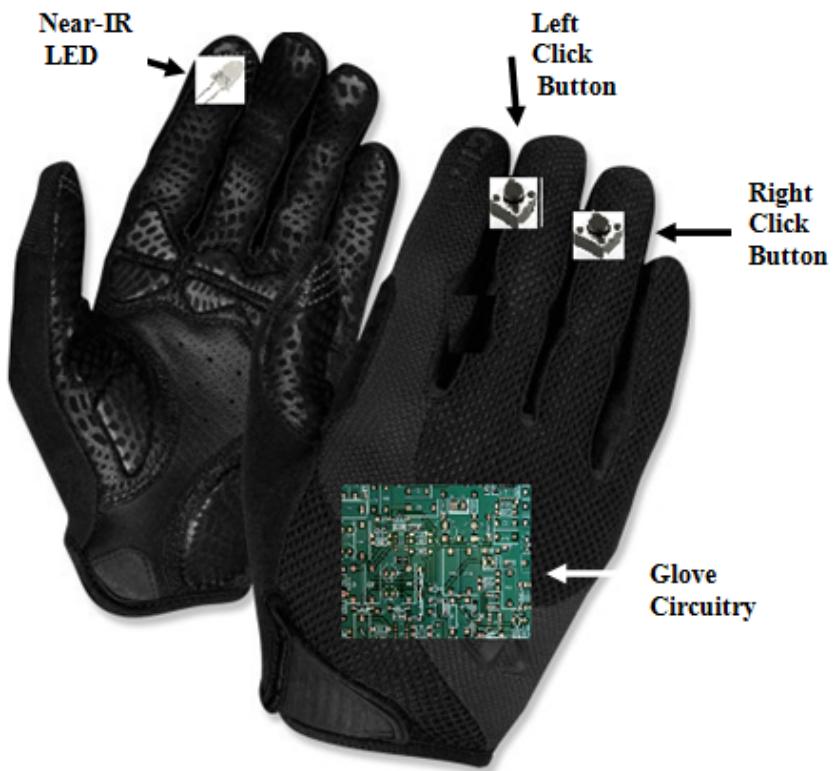

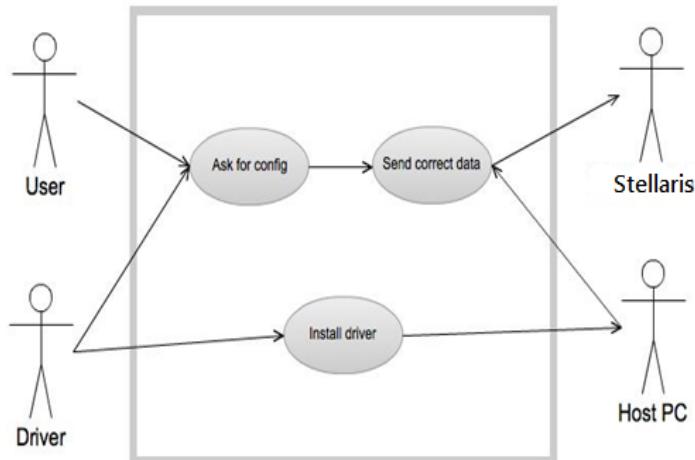

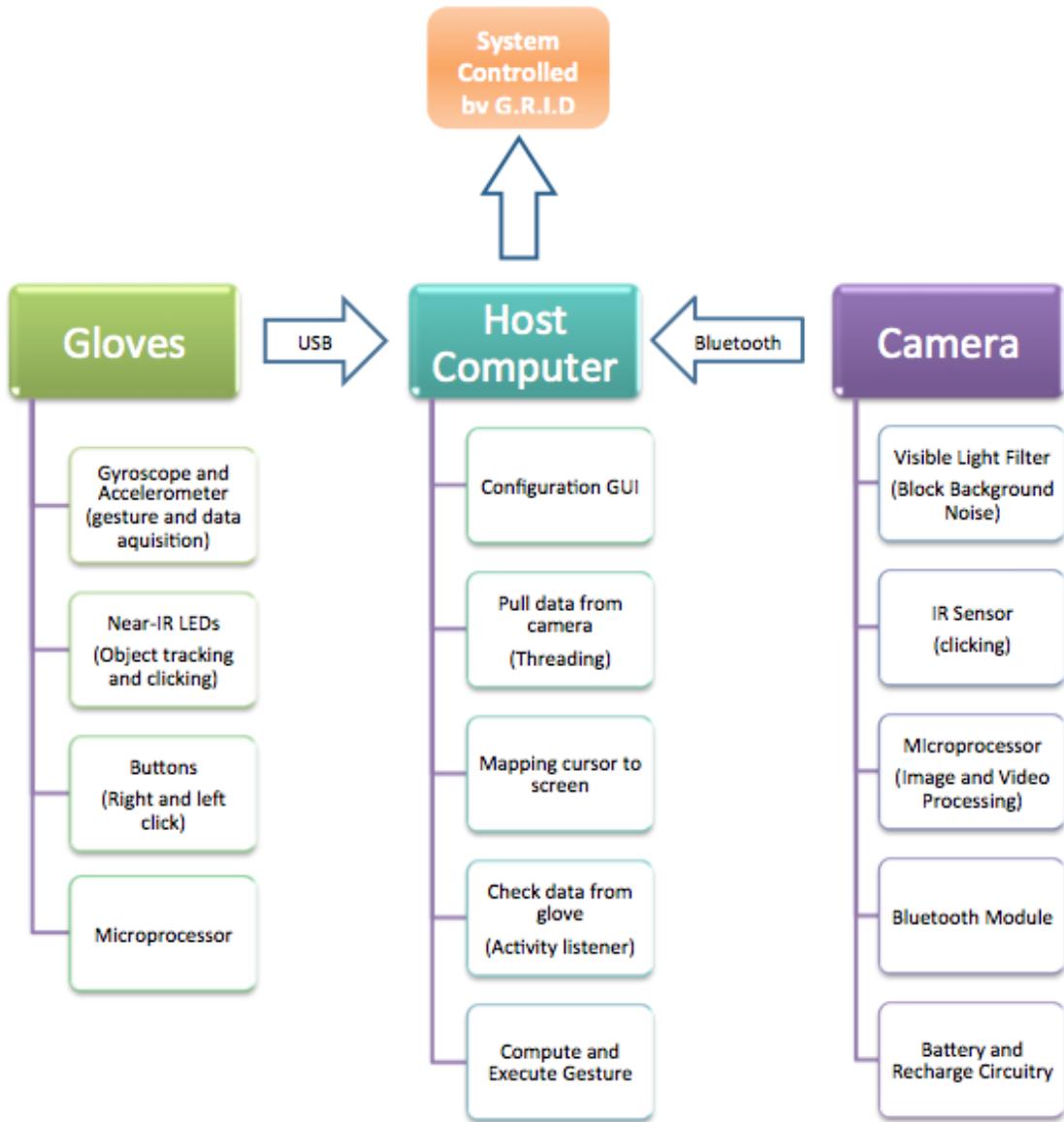

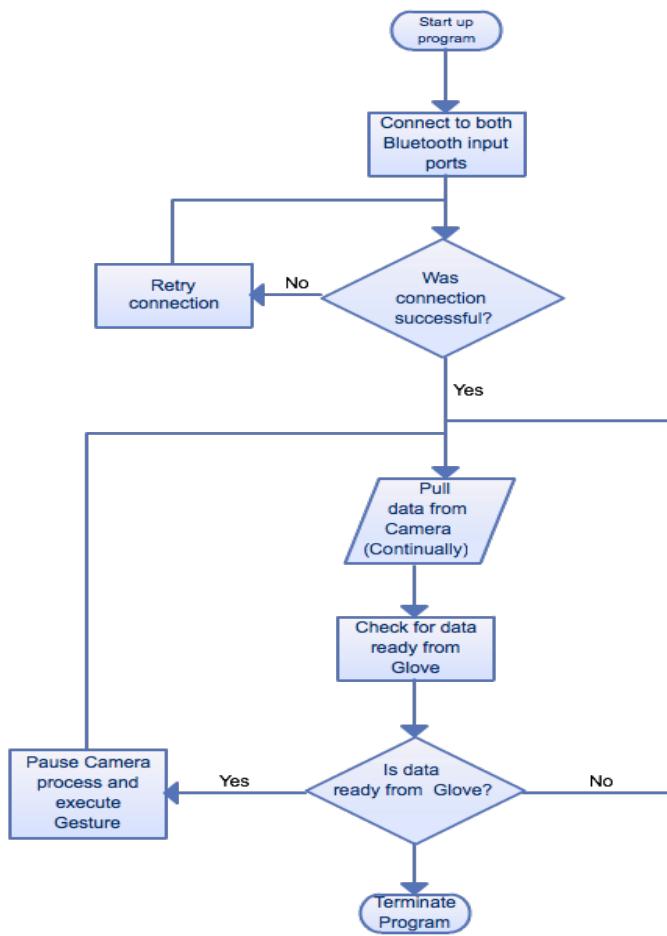

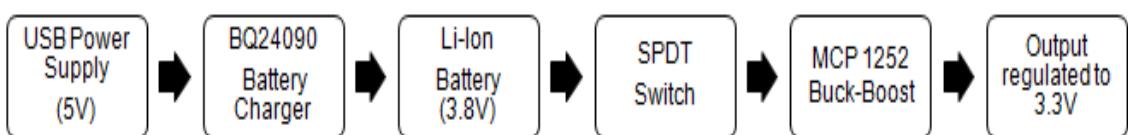

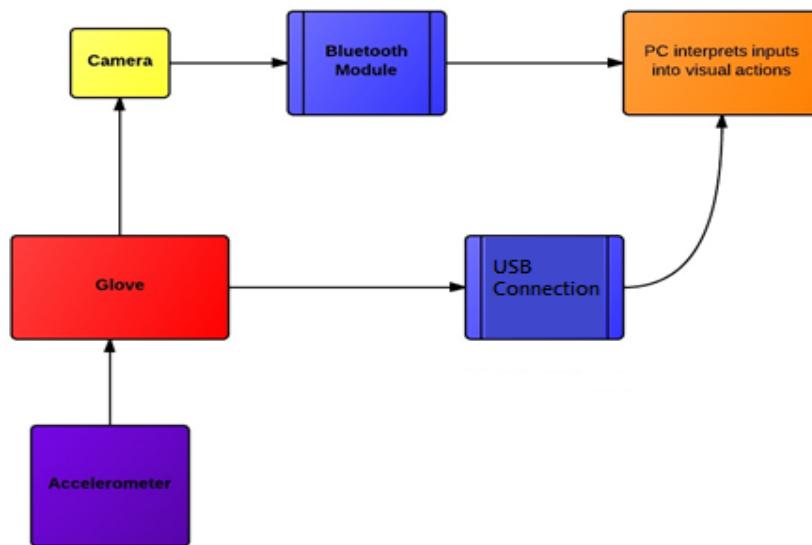

GRID is a Gesture Recognition Interface Device. GRID seeks to take the world of control devices to the next step using image tracking and gesture recognition to interface with the host computer. The device has been embedded within a glove that fits over the users hands and uses a camera module to track near-IR LEDs on the glove. It also has other instruments like an accelerometer and gyroscope which has been used to determine if the user has made a specific gesture, if so then it will send the commands via Bluetooth to the host computer where the command will be translated into action. Other features, which have been added, are a removable PCB design that will allow the user to use either hand as the main control device. This makes GRID usable for both right hand and left hand users.

The original desire of GRID was to design a well-fitted glove and light for the user so that there would be no issues with fatigue while using the device, which was achieved. It will function and carry out all the operations that a typical mouse would with the added features of a gesture design. What that means is there will be special "gestures" the user can do in multimedia programs to control the features of that program, as well as a few other special features for application specific actions.

GRID is the next step forward in consumer control devices, with its sleek design and universal user abilities as well as the application specific actions it will have the ability to run. As technology progresses so should the control devices.

## 2.0 Project Description

### 2.1. Motivation and Goals

The motivation behind GRID was to create an intuitive input system that would be easy and fun to use for computer applications that are not particularly keystroke-intensive, such as surfing the web and playing certain video games. Few commercial products, hobby projects, and past courses in particular inspired the group members. In particular, the group was inspired by Iron Man hand repusor gadget. In the Iron Man movie, Tony Stark lifts his arm, palm facing

toward his target. This replusor device releases a powerful blast of energy, blowing his opponents off their feet. The motivation of the group is not to blow opponents off their feet but find an easy, intuitive, and enjoyable way to using the computer. The project is not something that was worked on for a period of two semesters and then forget about it but we hope this project inspire better design and eventually real-world use.

After looking into the idea of implementing a wireless-wearable mouse the team learned that two students in MIT have work on a design very similar to the idea in mind. Glove Mouse from Tony Hyun Kim and Nevada Sanchez has designed wireless gloves. Their project consists of two sport gloves an LED on the back of the index finger, picked up by a webcam to act like a cursor, along with bottoms under the index and middle fingers activated by the thumb. The group decided to expand on this idea by adding a gesture library.

Another reason the group decided to implement this project was because the different image processing techniques that would need to be researched and implemented in which the group wanted to learn to master by the end of Senior Design 2. The team has taken many classes throughout their pursuing degrees in Electrical and Computer Engineering in which theories such as infrared, wireless technology, and programming has been taught. In which the group wishes to expand their knowledge in such theories. The group members will have a chance to learn from different aspects from this project. As a team it is expected to work collaboratively to meet the project requirements and achieve measurable and significant results.

## **2.2. Objectives**

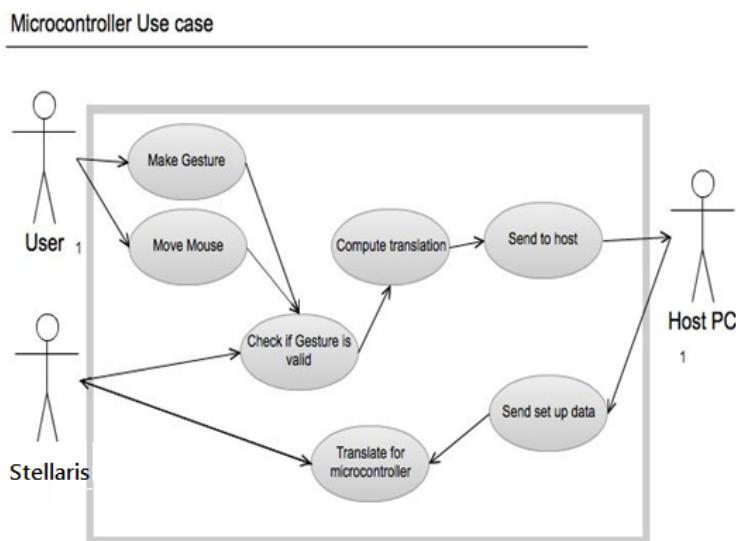

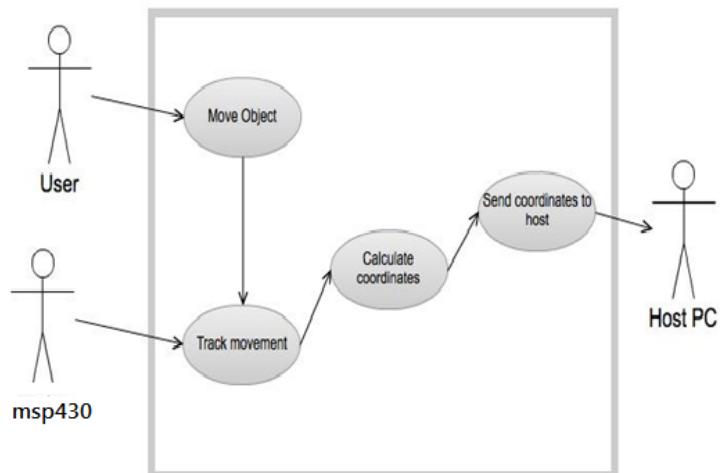

The main goal of GRID is to create a wireless gesture input system that enables a user to use a computer by performing intuitive hand and finger motions in the air. While wearing a glove controller on the right hand or left hand, the user can move the cursor by forming a pointing gesture and click by pressing onto the push buttons with thumb. Wearing the glove device on the users desired hand allows the user to perform gestures that will be interpreted for zooming in, zooming out, and refresh through a combination of tilting the hand and touching different portions of the fingers with the thumb and index fingers. The controllers communicate to the computer wirelessly.

The glove controllers that rely on various finger and thumb touch actions. We decided to improve upon this concept by incorporating accelerometers to detect the tilt of the hand as well, thus permitting wrist movements to control the computer with a combination of intuitive gesture actions.

The project's objectives to satisfy the goals should follow the following guidelines:

- High efficiency and low cost

- User Friendly

- Comfortable and lightweight glove

## **2.3. Project Requirement and Specifications**

To improve the user wireless, wearable mouse experience the quality of the gloves, operation range, and battery lifetime was considered. As explained earlier the glove will have a mounted near-IR LED in the index finger when picked up by the camera module to act as cursor or gesture recognition its accuracy is of 16-pixel clutter and optimum operation range up to 15 ft. from the computer, to allow the user mobility while still operating the computer. The real time image processing will be done using an IR camera interfaced with the microcontroller via Bluetooth controlling a servo in which response time/gesture recognition should be less than 1 second. The size of the circuitry was considered with this consideration the weight of the gloves are less than 3 lbs. each glove. The battery run time on the slide on circuitry is necessary efficiently to last 8 hours, to support constant user use during the hours of operation of the gloves while requiring no more than 2 hours of charging time. Below is summary for the project requirements and specifications:

- Accuracy: 16 pixel cluster

- Optimum Operation Range: up to 15 ft.

- Weight: Less than 3 pounds each glove

- Battery Lifetime: 8 hours of continuous use

- Recharge Time: Less than 2 hours

- Response time/gesture recognition – Less than 1 second

During the implementation of the GRID design we may have chosen to revise the project requirements and specifications, but overall this project requirements should remain true.

## **3.0 Project Research**

### **3.1. Image Processing**

#### **3.1.1. Overview**

Image processing spans from face detection on your digital camera to manufacturing robots; which make use of computer vision technologies. In this project it was considered an Image Processing algorithms for the purpose of object tracking and recognition to track the movement of the user's hands, which will allow user interaction. This will be implemented using an FPGA.

#### **3.1.2. Object Tracking**

The purpose of video tracking is to locate a moving object in time and space using a camera. An algorithm analyzes the video frames and outputs the movement of targets between the frames. Video tracking systems consists of two major components:

- Target representation and localization algorithm- this process is totally dependent on the algorithm.

- Filtering and Data Association algorithm- this process involves prior information about the object and scene and it deals with the objects dynamics.

The function of the tracking algorithm is to estimate the motion parameters that are achieved by analyzing individual frames. These parameters identify several factors such as location, speed of target, direction changes, time in motion, and information about shape and size of target. The information in this section was gathered from [1].

The video-tracking algorithm is responsible for analyzing the video data and producing x and y coordinates for each LED. The algorithm works by filtering the video for pixels with the appropriate shade (red) and light. The x and y position of the pixels that are passed are then averaged to find their center of mass. The output is then smoothed to suppress the effect of noise in the video. Finally, these coordinates are transformed to fit the screen. The video will take up 720 x 480 display. The details for image processing system will be explained in greater details in this paper. This system is broken down into two sections: Image Acquisition Algorithm and Object Tracking Algorithm.

### **3.1.3. Image Processing System**

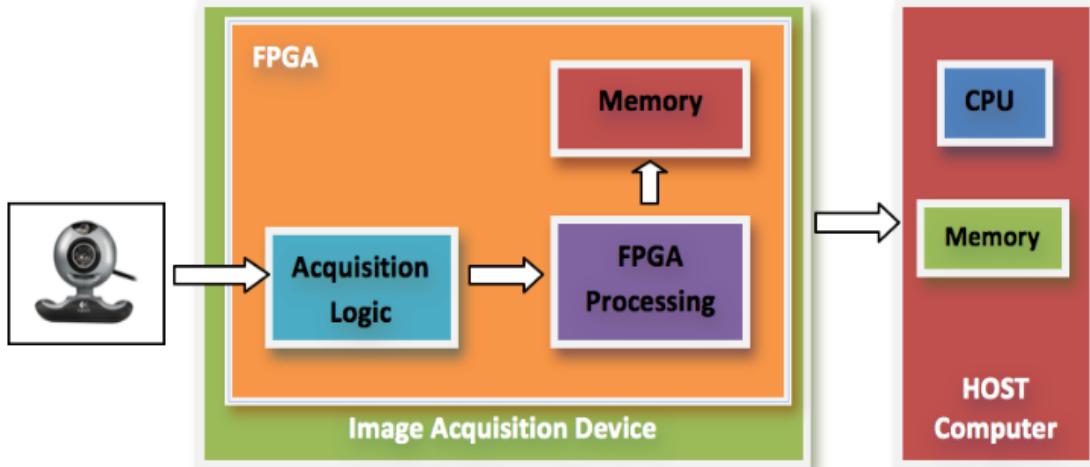

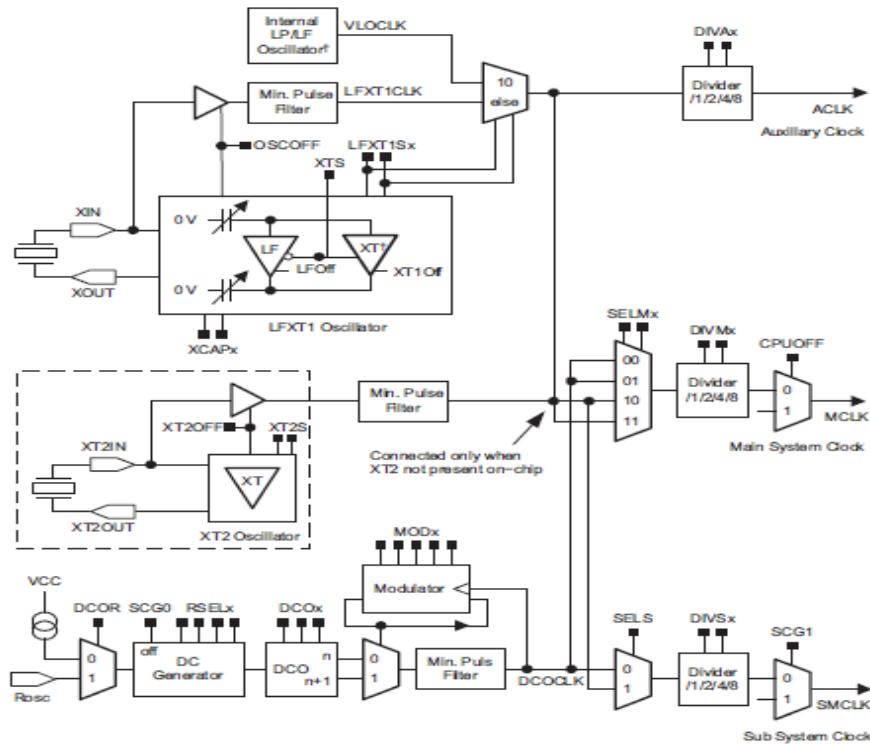

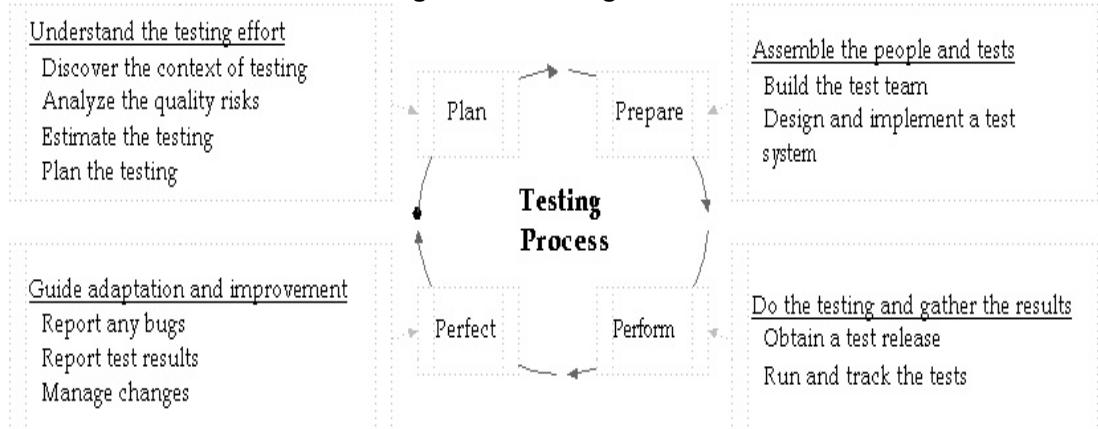

To begin, the frames are acquired individually from the camera and fed into the FPGA. Then, the individual frames will undertake a process of segmentation, thresholding and filtering. Once the frames are subjected to this process following this, the object will be tracked by making a comparison between the background frames and the new processed updated frame containing the new location of the target. This process can be taught as comparing two frames, the current frame to our newly processed frame. As a result, tracking a moving object using an FPGA implementation was found to be appropriate for the purpose of object tracking. Figure 1 shown below shows the block diagram of the FPGA pre-processing.

Figure 1: Block diagram of FPGA pre-processing

### 3.1.4. Image Acquisition

The video streaming is captured using a webcam, which produces stream of RGB pixels. The Philips webcam will be mounted on a stand with a fixed background that contains the object to be track for the purposes of this project the gloves will contain NIR LEDs in the thumb and index fingers on both hands, which is the object to be tracked. The webcam will continuously stream video through the FPGA. One important parameter to consider is the frame rate vs. spatial resolution of the camera. For the purposes of this project it only requires low resolution since the camera will acquire frames at high rate. The size of the video frame will be set to 640x480 pixels that is a common format used by non-megapixel network cameras.

At the output of the FPGA the video obtained will be read in the computer using Matlab. This software will process the video and convert it into image frames at a rate of 10 frames per second.

#### 3.1.4.1. Frame Generation

At the output of the FPGA the video is fed in the Matlab program. The program reads the file and converts it to frames. The frames are produced at the rate of 10 frames per second. Considering a 10 second video when converted to frames it will be a total of 100 frames produced in RGB format. These frames are then stored as individual files 11 files that is a total of 100 files. The files are then arranged in the order of their occurrence in the video. The first frame is selected as the Base – Background Frame. The remaining bitmap files are used for the process of Object Recognition and Tracking.

#### 3.1.4.2. Image Recognition Algorithm

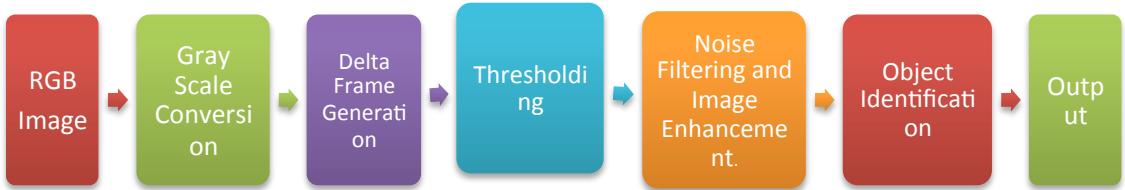

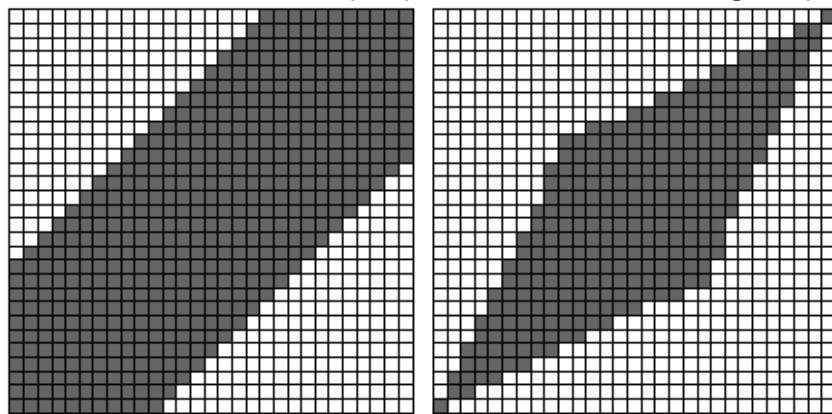

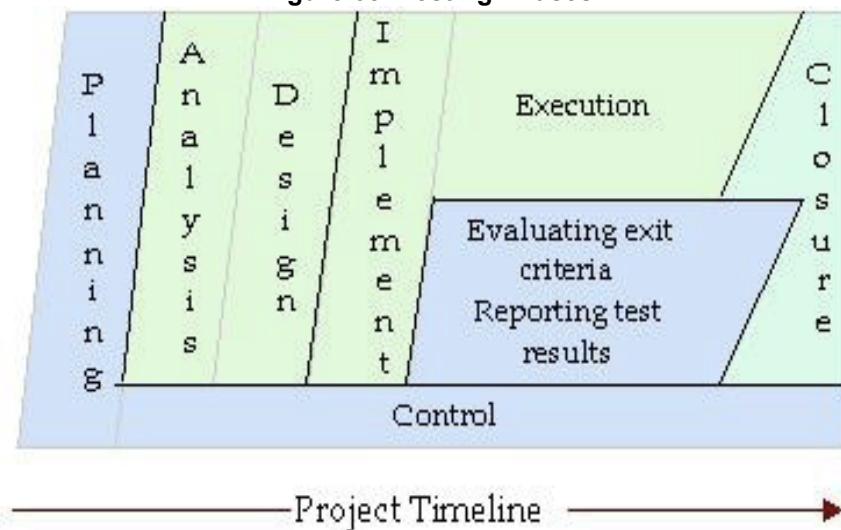

This algorithm incorporates various parts that are used for object recognition such as, Grayscale Conversion, Delta Frame Generation, Thresholding, Noise Filtering and Image Enhancement. Figure 2 shown below shows the Image Recognition Algorithm Flow that will be explained in greater detail in this section.

Figure 2: Image Recognition Algorithm Flow

- **Grayscale Conversion:**

At the output of the FPGA passes the data through Matlab, which will convert the video into frames. Once these frames have been generated and the background and object of interest has been selected, for our purposes the NIR LEDs, these RGB format frames will be converted to gray scale. Then, a pixel value will be obtained of these RGB to gray scale format frames through a weighted sum. If an object is purely red then it will have a low value for the weighted sum therefore will appear dark in the gray scale by subtracting the gray scale image from the red component of the original, then the object can be extracted. These RGB frames have standard pixels values of 640x480 pixels. All objects fewer than 300 pixels will be removed and this will allow us to separate the infrared objects from the background. The information in this section was gathered from [1].

- **Delta Frame Generation:**

After, the gray scale conversion has been accomplished then, the gray scale image from the original RGB image will be subtracted. This resultant frame is called the Delta Frame. This technique of image subtraction removes the background and brings the object of interest (NIR LEDs) into attention, giving information about its shape and size. Another advantage of using this technique is that it reduces the number of pixels that the system will have to process. The information in this section was gathered from [1].

- **Thresholding:**

A key component to vision applications is to be able to separate out the regions of the image which corresponds to the object of interest, from the regions that corresponds to the background. Thresholding provides a convenient way to perform this segmentation provided different colors or intensities in the foreground and background regions of the image.

The input to the thresholding operation will be the delta frame gray scale image. The output is a binary image representing the segmentation between the foreground and background regions of the image. The foreground, which corresponds to the object pixel, is given a value of “1”. The background, which corresponds to the black pixel, is given a value of “0”. Then, a comparison will

be made between the pixel intensity to the threshold value if the pixel intensity is higher than the threshold value, the pixel is set to white at the output. If the pixel intensity is less than the threshold value, the pixel is set to black at the output. The information in this section was gathered from [1].

- **Noise Filtering**

The medium filter will be used to reduce the noise in an image. There are two types of filter to consider when preserving the details of the image: medium filter and mean filter. For the purposes of this project a medium filter will be used because it is useful in preserving the details in the image. The medium filter takes into consideration each pixel value in the image it also looks at the neighboring pixel values. Once, the pixel value and neighboring pixel values have been determined it replaces the pixel value with the medium of the neighboring pixel values. In summary, the medium filter allows high spatial frequency details to pass and at the same time is very efficient at removing noise on images. The information in this section was gathered from [1].

To conclude, this image recognition algorithm helps detect the object and gives us information about its shape and size. Then, this information will be used about the object of interest to then track the object. The object-tracking algorithm is going to be considered in section 3.1.5.

### **3.1.5. Object Tracking Algorithm**

This algorithm incorporates various parts that are used for object tracking such as, frame rate, determining object position, and relative tracking.

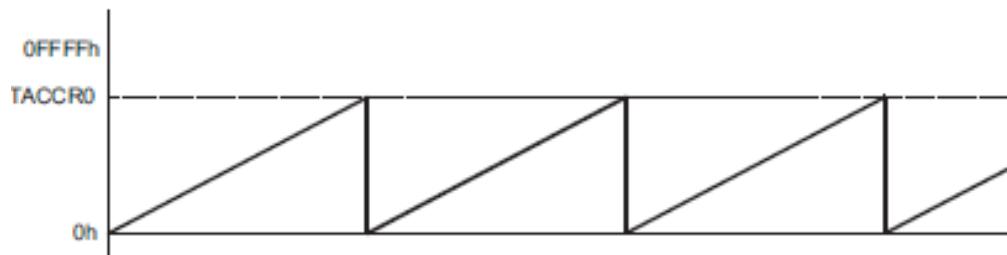

- **Frame Rate:**

Using the image recognition algorithm, which provides information about the object shape and size, then it will be tracked by selecting the frames acquired from the video. A video stream will be sent via Matlab at the rate of 1 frame per second. This means the video will continue to be streaming until 100 frames are produced, which are equivalent to 10 seconds of video. The rate that has been chosen completely depends on gathering the complete motion of the object. A frame rate of 1 frame per second will be considered for the purposes of this project. A frame rate of 4 frames per second might also be considered to reduce complications.

- **Finding Centroid of Object:**

As to finding the center of gravity, which is, used for the purposes of tracking the target, as it is a geometric property of any object, this is used in many applications. The center of gravity is taking the average location of the weight of an object. Using this method can help describe the motion of the object through space in terms of the translation of the point of the object from one place to another.

Generally speaking, trying to find the center of mass for the purposes of this

project the gloves can be a bit challenging because the mass may not be uniformly distributed throughout the object. To simplify this problem it is assumed that the object is composed of uniform material. The image will undertake the process of the image-processing algorithm explained earlier to acquire a noise free enhanced image. An operator then scans the entire length of the image frame for the first white pixel. This is a clear indication of the 2D position of the object within that time frame. This is iterative process and it repeated over all the frames. The information in this section was gathered from [1].

- **Relative Tracking:**

Using the update location of target in which it was considered the ideal frame rate (1 frame per second) explained earlier and a fixed background, then the frame will be subjected to a procedure for object recognition. This includes a noise free enhance image which will only contain the object. This tracking procedure will analyze each frame in search for the first white pixel, which represents the object. This point is then plotted on a new image as the first position of the object. Successive frames are gathered, subtracted from the background, filtered, enhanced and then the points are computed. This process will continue over and over in which the updated locations of the pixel points are collected to provide the approximate path taken by the object. This repetitive procedure that acquires the frames and plots the individual points in a new image is known as, object path. The information in this section was gathered from [1].

In conclusion, the object-tracking algorithm plots the objects path. This algorithm is very important to tracking the gloves position onto the screen.

### **3.1.6. Wii IR Camera System**

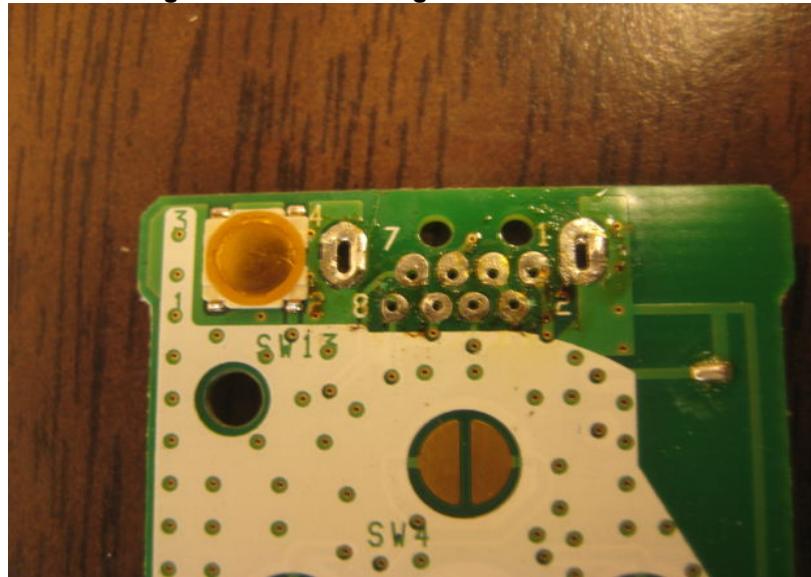

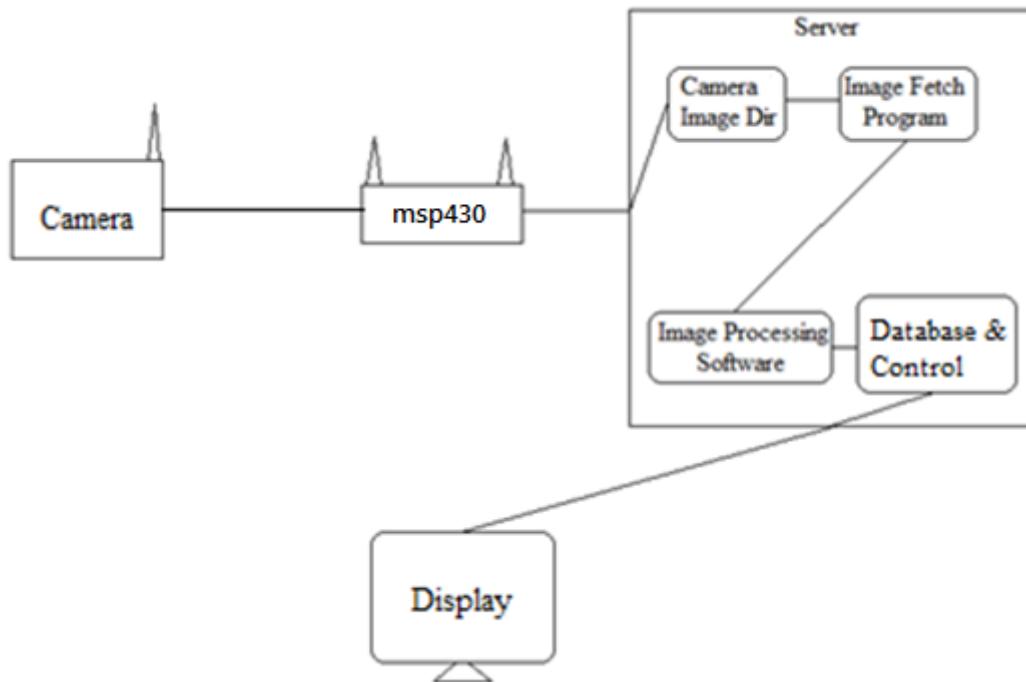

Initially, the group proposed using an FPGA for the purposes of object tracking. Due to time constraints the group look for other possibilities to track the IR-LED on the index finger. The group used the PixArt IR camera sensor, which, is commonly found in the Wii remote.

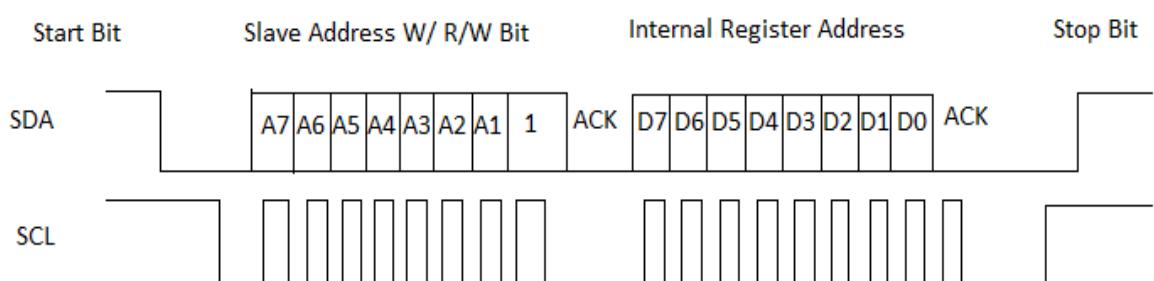

The PixArt IR camera sensor is capable of tracking up to four IR spots. Its image processing provides location data at 1024x768 resolution. The PixArt IR camera was physically extracted from the Wii remote due to the budget restrictions of the group. The IR camera is interfaced with the microcontroller via Bluetooth controlling a servo. The IR camera has an integrated processor, which output the X and Y positions and size of the near IR LEDs that it detects. The details for the near IR LEDs will be explained later in this paper. This is very beneficial for tracking the position of the cursor.

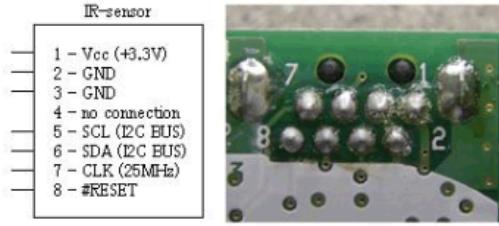

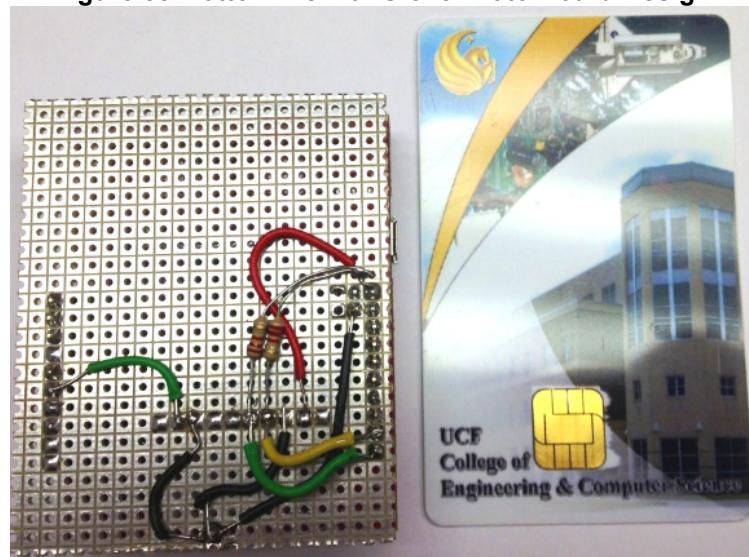

We needed a circuit to interface the IR camera to the MSP430. The parts that are needed for this circuit are two capacitors, a 25 MHz crystal, and a 1 Meg Ohm resistor. Below is the IR camera pin assignment:

Figure 3: IR Camera Pins

## 3.2. LEDs

### 3.2.1. Wavelength

Wavelength refers to the spatial period of a wave, in other words the distance over which the wave repeats itself [17]. Our eyes are only sensitive to the visible light spectrum, which goes from about 400nm to 700nm. Infrared radiation has a longer wavelength than visible red light and therefore the unaided eye cannot see it. It is important to have a basic understanding of wavelength before studying which LEDs were adequate for this project.

LEDs come in a variety of wavelengths and based on the role that this device will play in the project a decision can be made on which LED family will better suit the purpose of this project. The purpose of the LEDs on this project is to make the index finger stand out from the background noise for better object tracking. The group looked further into the infrared family of LEDs since any LEDs within the visible wavelengths will have too much interference with the background. In order to use these LEDs we a set of filters was needed, which will be explained in more detail in sections 3.3.5. Even within the infrared family, the LEDs come in a variety of wavelengths: near-infrared, short-wavelength infrared, mid-wavelength infrared, long-wavelength infrared and far-infrared. Characteristics of these infrared groups will be explained in table 1.

Table 1: Infrared LED Information

| Name                             | Wavelength (μm) | Photon Energy (meV) | Applications                                  |

|----------------------------------|-----------------|---------------------|-----------------------------------------------|

| <b>Near-Infrared (NIR)</b>       | 0.75 - 1.4      | 0.9 - 1.7           | Fiber optic telecommunications & night vision |

| <b>Short-wavelength Infrared</b> | 1.4 - 3         | 0.4 - 0.9           | Long-distance Telecommunications              |

| <b>Mid-wavelength Infrared</b>   | 3 - 8           | 150 - 400           | Guided missile technology                     |

| <b>Long Wavelength Infrared</b>  | 8 - 15          | 80 - 150            | Thermal Imaging                               |

| <b>Far-Infrared (FIR)</b>        | 15 - 1000       | 1.2 - 80            | Spectroscopy                                  |

In conclusion the LEDs played an important role in this project. They will make the index finger stand out from the residual background noise after the visible

light/IR filter is installed. After looking at the information provided on the table above, the group came to a conclusion that the near-infrared LEDs best suits the purpose of our project since they are often used for night vision which is the closest application to the one used in this project. The data to create table 1 was compiled from [16].

### 3.2.2. Viewing Angle

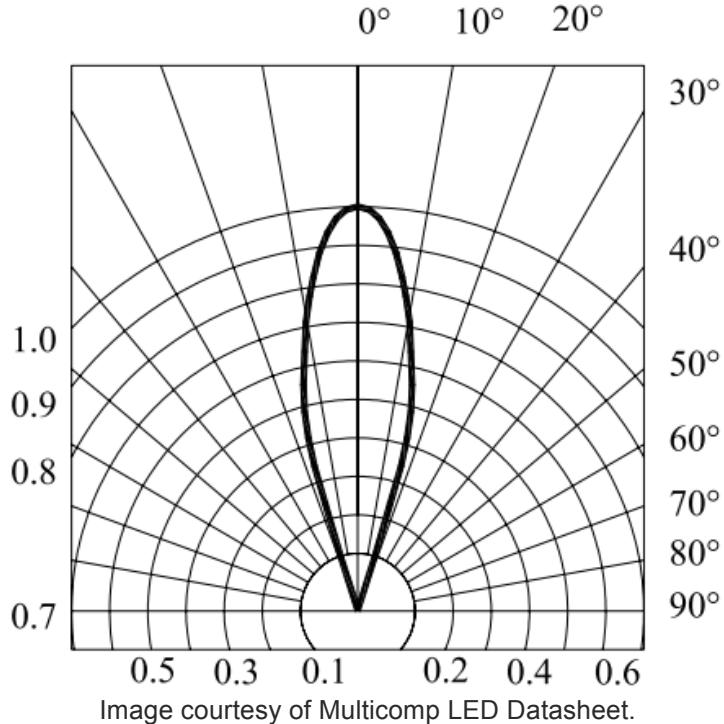

Another factor that the group took into account when using LEDs is the viewing angle or degree. The viewing angle or degree refers to the spreading of the light emitted by the LED. For example a wide angle means that the light emitted by the LED will not travel far because it will instead spread out over a large area. A good example of this is a flashlight, these devices usually have a wide viewing angle. An LED with a small angle will have less dispersion of light and more energy in the spot. A good example of a narrow viewing angle device would be a laser. This information can be found in the LEDs data sheets and as expected it will influence in the price of the LEDs. Figure 4 below shows the spatial distribution of LEDs.

Figure 4: LED Viewing Angle- Degree

Image courtesy of Multicomp LED Datasheet.

It is evident by looking at the figure above that the viewing angle will affect the spot size of the LED. For this project we needed LEDs that have a bright spot, so each LED can be distinguished from one another. An advantage of using a visible light filter is that it will make the viewing angle of the LED less critical; it will do this by blocking the background noise. Moreover it is important to choose a narrow enough angle for the camera to recognize each LED separately as this is critical for the gesture recognition portion of this project.

### 3.3. Camera

#### 3.3.1. CCD vs. CMOS

There are two major types of cameras: CCD (charge couple device) and CMOS (complementary metal oxide semiconductor). In order to chose the camera that was going to be use for this project we needed to consider the specifications of the device. Both of these cameras use a photo diode sensor, which converts light into electric charge and processes it into electronic signals. Below in Table 2 we included a summary of the features to consider when choosing a camera that best suits the purpose of our project:

Table 2: Feature and Performance Comparison between CCD and CMOS cameras

| Feature              | CCD                      | CMOS                |

|----------------------|--------------------------|---------------------|

| Cost                 | Low                      | High                |

| Fill Factor          | High                     | Moderate            |

| Signal out of chip   | Voltage (analog)         | Bits (digital)      |

| Signal out of camera | Bits (digital)           | Bits (digital)      |

| System Noise         | Low                      | Moderate            |

| Speed                | Moderate- High           | Higher              |

| Biasing and clocking | Multiple, higher voltage | Single, low voltage |

| Responsivity         | Moderate                 | Slightly better     |

The content of this table is from Teledyne Dalsa [32].

Now that we have consider the feature and performance between a CCD and CMOS cameras we will go into the specifications of the camera that will achieve the purpose of this project. Later in this paper we will go into the implementation of a small camera system capable of streaming live video images from an image sensor (CCD or CMOS) to a PC through the FPGA. Below we will consider 2 types of cameras:

- HP HD-3110 5.7 Megapixel Webcam,

- Sensor: CMOS

- USB 2.0 Interface

- Resolution: 352 x 288, 424 x 240, 432 x 240, 640 x 360, 640 x 480, 800 x 448, 800 x 600, 960 x 544, 960 x 720, and 1280 x 720

- Transmission Frame Rate: 30frame/sec

- Dimensions (L x W x H): 2.93 x 2.76 x 2.58" / 7.44 x 7.01 x 6.55 cm

- Unit Weight: 0.22 lb / 0.1 kg

- USB Digital PC Web Camera with Microphone CMOS VGA sensor features:

- Sensor: CMOS

- Frame Rate: 30 FPS

- Lens: High definition 3P(1.3M/2.0MP); 5P(5.0 MP)

- Pixels: 5.0-megapixel

- Resolution: 320 x 240, 680 x 480, 600 x 800, 1280 x 1024

- Interface: USB 2.0

- Transmission Frame Rate: up to 30frame/sec

- Video Format: 24-bit true color

- Supported operating system: Support Win98/2000/XP/Vista/Win7/Mac system (XP, Vista and Win7 support plug and play)

- Focus range: 3cm to infinity focus range

- CMOS Chip Type: High-resolution Color CMOS image sensor

- Unit weight: 66.3g

It was also considered using an image sensor for getting the data (image frames) ready for calculation in the FPGA. The reason we considered using an image sensor is that using the USB on the FPGA can be least practical thing to do. When using a webcam we needed to make sure to have an open-source driver for the webcam. Webcams use proprietary, undocumented, protocols and compression in which we didn't want to waste our time doing reverse engineering to the webcam.

It was also considered using an image sensor for getting the data (image frames) ready for calculation in the FPGA. The reason for considering using an image sensor is that using the USB on the FPGA can be least practical thing to do. When using a webcam it is important to make sure to have an open-source driver for the webcam. Webcams use proprietary, undocumented, protocols and compression in which time can be wasted trying to do reverse engineering to the webcam.

It was also considered using a VGA camera because is the most basic camera compared to the megapixel camera, which has more pixels, meaning more colors and details. The image sensor we considered is the Agilent ADCS-2021:

- CMOS Image Sensor

- VGA Resolution – 640x480

- Frame Rate – 15 frames per second

In addition, the data bus can be configured as 8 to 10 bits wide. All of its functionality is controlled via internal registers, which are accessed via an I<sup>2</sup>C bus. The contents of this section was gathered from [33] and [34].

### 3.3.2. Resolution

Resolution is how pixels are stored in computer memory, they may be thought of as mathematical points. Once image is displayed, the space between the points needs to be filled in. The number of spots that can be resolved on the display depends on the quality of the system. For our purposes we didn't require a camera with high resolution (640x480). We considered various resolutions for the purpose of this project and mapping its centroid to the location of the screen.

### 3.3.3. Frame Rate

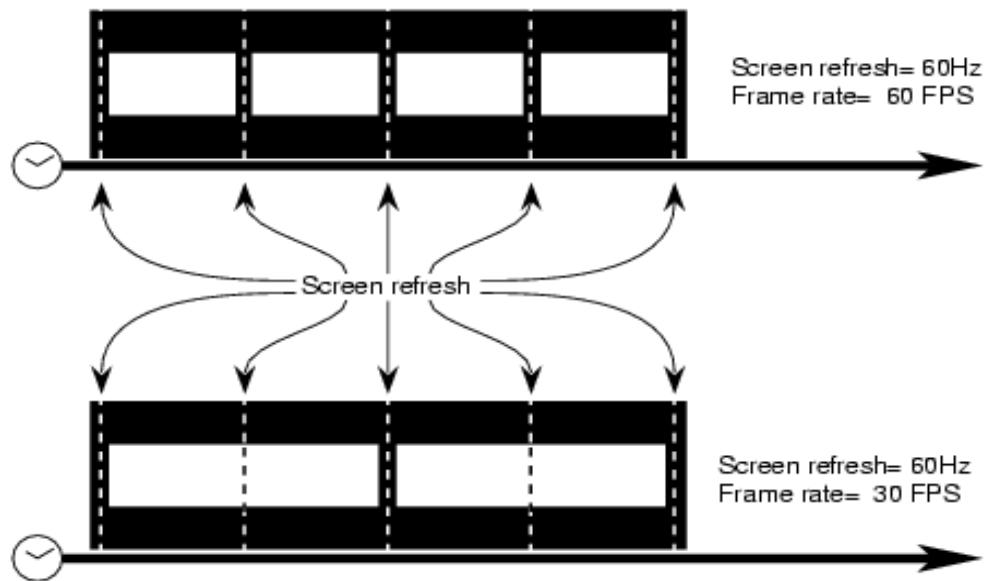

The frame rate of a camera is the number of pictures it can take and how quickly it can transfer those to the computer's screen. The frame rate is constrained by three factors: the rate at which the screen is refreshed, specified frame rate and the time required to calculate and draw the scene [11]. Frame rate is measured in frames per second. For this project we needed to stream video from the webcam and to do so we had to consider a camera with a decent frame rate, 15 fps is the absolute bare minimum. Most cameras that have been considered within the budget of this project stream at 30 fps, that means it can take 30 pictures every second and then transfer them to the computer screen or in our projects case the FPGA, which is a good rate.

Figure 5: Frame Rate

Image courtesy of Silicon Graphics International Corp. Permission:4

Above in figure 5 we see the same film taken at different speeds. The one on the top is taken at 60 frames per second and it is evident that a new image is there every time the screen refreshes. In the film underneath although the screen refreshes as frequently there is no new image every time the screen refreshes. This can cause a blur effect on the video.

### 3.3.4. Spectral Response

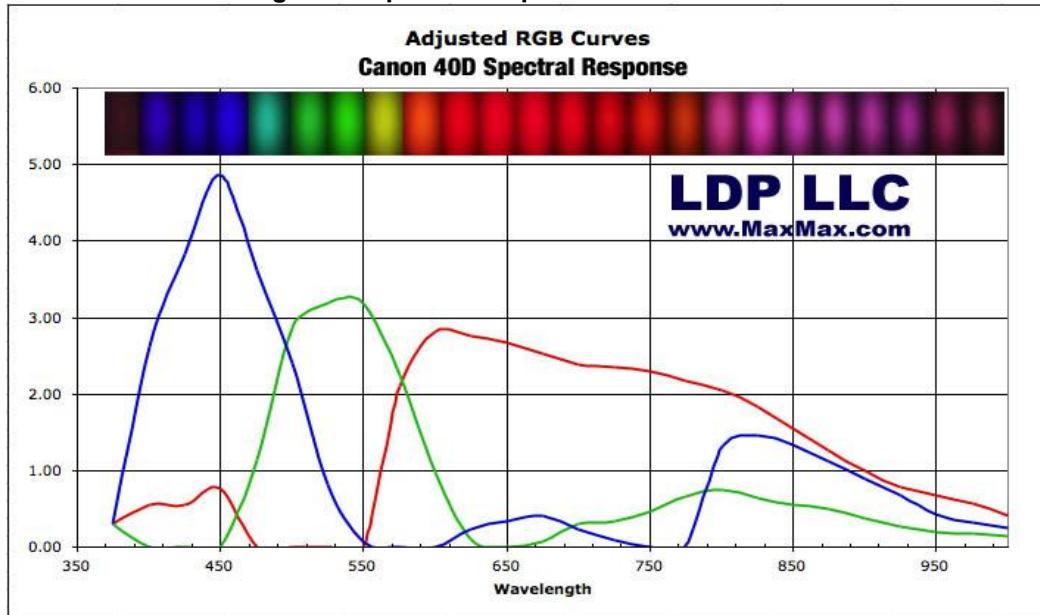

Spectral response or spectral sensitivity refers to the efficiency of light detection in a camera as a function of the wavelength of the signal. This information is hard to find since most companies do not specify this on lower end products like the webcam that was planned to be used in this project. For educational purposes a figure of the spectral response of a high-end camera, Cannon 40D is attached below:

Figure 6: Spectral response for a Canon 40D

Image courtesy of LDP LLC. Permission:8

At the top of figure 6 there is the visible spectrum colors in order of lowest to highest wavelength and the wavelength values in nanometers are listed in the horizontal lower axis of the graph. It is evident how this camera peaks at about 450nm which is the wavelength for the color blue. This means that this particular camera is most sensitive to blue colors. We can also see peaks at 550nm and 625nm which are green and red respectively. The other peaks or "leakage" is due to imperfections in the color filter. This is important to know because the goal of this project is to have a camera that is most sensitive to near-infrared wavelengths so the camera can pick up easier the gestures performed by the glove.

### 3.3.5. Visible Light Filter

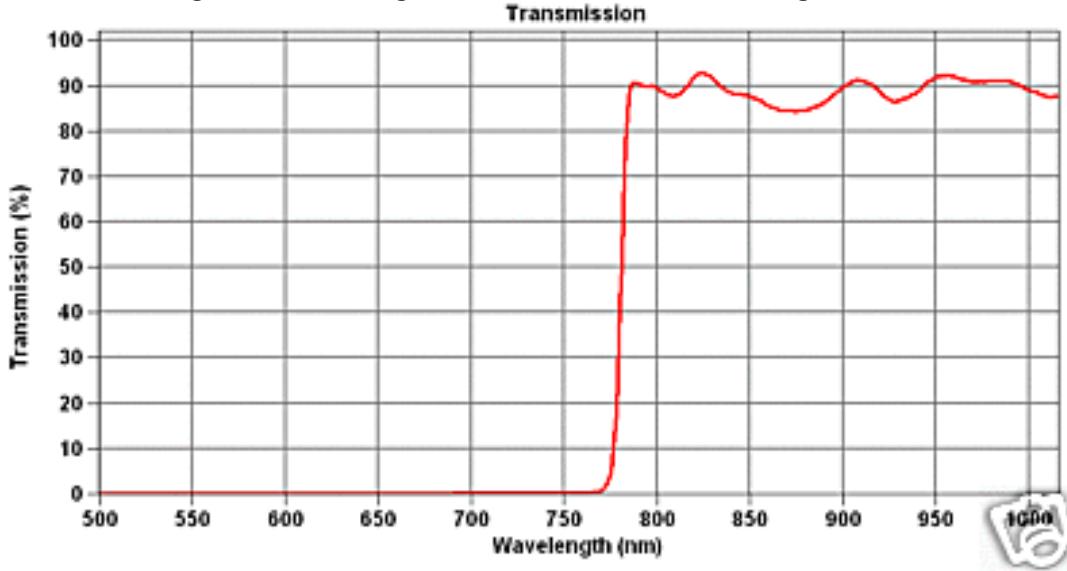

In this part of the project it is required that the camera blocks out visible light and will detect near-infrared wavelengths ( $0.75\mu\text{m}$ - $1.4\mu\text{m}$ ). Below there is a figure of the transmission of a visible light filter. Ideally it will transmit about ninety percent of the wavelengths past the 750 nm, which is the highest end of the visible spectrum.

**Figure 7: Wavelength Transmission of a Visible Light Filter**

Image courtesy of Sypherus Labs. Permission:7

As a result of doing research the group found out that infrared cameras are more expensive than regular webcams. The group also found out that camera sensors are naturally very sensitive to the near-infrared wavelengths [13] and for this reason they come with a built-in IR filter. The modification that had to be performed to the camera to work in the desired wavelengths was to add a visible light filter to block out the visible light wavelengths and to remove the IR filter to allow the near-infrared wavelengths to come through the sensor. The IR filter could be a separate filter or a coating in a lens depending on the camera used. The visible light filter can be engineered by using the magnetic disk of a floppy disk or film.

**Figure 8: Infrared LEDs seen with the IR filter removed and the visible light filter**

Image courtesy of Sypherus Labs. Permission:7

As mentioned before the goal of this filter is to block out background noise from the object of interest, which are the near-infrared LEDs for better object tracking. The figure above was obtained from an experiment [14] where the IR filter was a coating and was sanded down and a piece of the magnetic disk of a floppy disk

was placed as the visible light filter. Although this experiment was used for different purposes the images capture the idea of what was needed to be performed in this project. The image above reflects the modified camera looking at three near-infrared LEDs. It is evident that this type of filter works in this experiment because the LEDs are much brighter than anything in the background which will make it easier to track the figures of interest.

## 3.4. FPGA vs. DSP Processor

### 3.4.1. Overview

Digital signal processing is usually implemented on two types of hardware devices: Digital Signal Processors (DSP Processors) and Field Programmable Gate Arrays (FPGAs). DSP processors are a specialized form of reprogrammable microprocessor, while FPGAs are semiconductor devices that are based around a matrix of configurable logic blocks connected via programmable interconnects that could be programmed depending on the application requirements [25]. For the purposes of this project the group studied and compared different parameters such as performance, power consumption, form factor and size, and cost which influenced the decision to use one device over the other one.

A DSP Processors can be continuously reprogrammed according to the requirements of different tasks, some related with the actual signal processing part and others related with the control or communication protocol. In a DSP processor there are “threats” which is when tasks share all the different resources like core registers, internal and external memory, direct memory access and I/O peripherals. These shared resources often interact in unpredicted or bizarre ways that may cause unexpected delays resulting in system failures in real-time applications where DSP processors are usually used.

FPGAs have flexible and reconfigurable hardware architecture. They allow a large amount of parallel processing and pipelining of dataflow. Latest FPGAs support high clock speeds, provide plenty of processing power, and large on-chip RAM. Pipelining in FPGAs is efficient and effective; this is possible due to the high I/O capability that allows FPGAs to access multiple RAM banks simultaneously. FPGAs use multiple memory banks for partitioning and pipelining of algorithms providing significant advantages in performance over the DSP processors such reducing performance bottleneck. The information on this overview was gathered from [19] and [25].

### 3.4.2. Performance

In this project cost and performance are two very important aspects that the group considered when choosing the image-processing device. The group wanted a device that was able to process the image within the budget goals. High speed and high performance are very important for the development and implementation of sophisticated DSP based electronic systems like the one that

was used in this project. The first thing to take into account in the development of a DSP application is the sampling rate of the system that was to be designed. DSP processor is more suitable for low sampling rate DSP applications, otherwise if sampling rate of the system under consideration is higher than a few MHz then FPGA is the better as a hardware platform for implementation of the DSP application. An advantage of DSP processors over FPGAs is that they can handle conditional operations better. If there is no conditional operation in the DSP application to be developed then FPGA is a better choice. For the purpose of our project we worked with conditional operations but we are more interested in working at high clock speeds and using the parallel processing functions that the FPGA offers. Also if the system uses floating points then the DSP processor will be a better option. Both FPGAs and DSP processor provide libraries for common DSP functions like FIR filter design and FFTs but more complex functions are not usually available, if any of these libraries was to be used then this would be a parameter to consider. In our project we didn't use the built in libraries. The information from this section was gathered from [22].

### 3.4.3. Cost

The cost of FPGAs and DSP processors are directly related to performance. In table 3 below we can see the difference in cost of DSP processors and FPGAs based on the MMAC performance. MMAC stands for “Millions of Multiply-Accumulate Operations per second. For the purposes of this project we were expected to stay within the medium MMAC performance range.

Table 3: Cost-Performance Relationship

| MMAC Performance Range | Device Cost Range | Minimum cents per MMAC for DSP Processors | Minimum cents per MMAC for FPGAs |

|------------------------|-------------------|-------------------------------------------|----------------------------------|

| Low (>300MMAC )        | < \$10            | 1.8                                       | -----                            |

| Medium (300-1000 MMAC) | \$10 - \$30       | 1.6                                       | 1.4                              |

|                        | \$30 - \$100      | 3                                         | 2.8                              |

| High (>1000 MMAC)      | \$100 - \$300     | 5.8                                       | 2.9                              |

|                        | > \$300           | -----                                     | 4.2-20                           |

### 3.4.4. Development Software

It is said that programming FPGAs is difficult, as this requires familiarity and expertise in a hardware oriented languages such as Verilog or VHDL [18]. In this project we wanted to explore other options to program FPGAs like Simulink HDL code generator or even the Labview FPGA module. The DSP processor can take a standard C program and run it. This C code supports a high level of branching and decision-making. It seems like it all depends on the skill and expertise of the programmer. Our group members do not have experience working or

programming FPGA but we felt like this is an important part of engineering that we wanted to explore further.

### **3.4.5. Power Consumption**

When developing a DSP applications power consumption and dissipation are also important parameters to be considered, especially for portable DSP based electronics applications. In our project we would have the FPGA circuit connected to the computer but it will have its own power supply, which was most likely to be a rechargeable battery. Systems using DSP processors must drive heavily loaded buses that are used to connect the DSP chips to the memory chips. The extra clock cycles needed to fetch the instructions and the operands from off-chip memory on these buses add more to the total power requirements needed to execute an algorithm. The power consumption of a chip is directly proportional to its clock frequency and due to the ability of an FPGA to split an incoming data stream and process it as several parallel data streams at lower clock rates also becomes an important part of the total power usage. In summary FPGAs are capable of providing much higher throughput than DSP processors due to their highly flexible architecture. This information was gathered from [21].

### **3.4.6. Form Factor and Size**

DSP processors and FPGAs are about the same physical size, the main difference is what is inside the chip. Another advantage of FPGAs over DSP processors is that they are In-System Programmable (ISP), which means they can also be reconfigured on the board during system operation. This means the FPGA can be reconfigured on-the-fly to switch or toggle from one function to another. This capability adds functionality and processing power to a minimum-chip DSP system controlled with an internal or an external controller. A DSP is optimized for use of external memory, so a large data set can be used in the processing. FPGAs have a limited amount of internal storage so need to operate on smaller data sets. Nevertheless FPGA modules with external memory can be used to eliminate this restriction. Since the code for our project was not written when this research was performed we weren't certain if would take advantage of this ISP capability but it was an option to consider when choosing one device over the other. The information from this section was gathered from [21].

### **3.4.7. Conclusion**

In conclusion lower sampling rates and increased complexity suit the DSP approach; higher sampling rates, especially combined with strict, repetitive tasks, suit the FPGA. The decision of choosing one device over the other depends a lot on the designer and the tasks that the devices would be performed on the DSP system. For the purposes of our project we consider using an FPGA. While comparing these two devices we learned that FPGAs have a lot of features that could be useful to the video processing part of the G.R.I.D. design.

## 3.5. FPGA Development Software

### 3.5.1. HDL Overview

In this project is important to have an understanding of what HDL is since an FPGA will be used to process the image. HDL is an acronym for Hardware description language and is an efficient computer design tool for the modern design and synthesis of digital systems. As technology advances, designs grow larger and larger every day. This language provides circuit designers the needed logic descriptions to be analyzed at high level, in other words HDL helps the designers with the verification before fabrication of actual hardware.

This language is based on text expressions of the spatial/ temporal structure and the behavior of electronic systems. The notion of time is a unique attribute that makes this language so useful over other soft programming languages. HDL provides different types or styles of descriptions for the same circuit functionality and these include: structural, behavioral, switch-level, data-flow, mixed type/style or mixed language. The two main hardware description languages are Verilog and VHDL. In the sections 3.5.2 and 3.5.3 below we will cover some of major differences between the two languages. The information in this and the following sections of VHDL and Verilog was gathered from [25] and [26].

### 3.5.2. VHDL

VHDL stands for Very high speed Integrated circuit hardware description language. VHDL is considered to be better at the system level where multiple entity/architecture pairs lead to flexibility and ease in writing code for complex systems. Below is a description of some important aspects that should be considered when choosing a hardware description language:

- **Data Types**- VHDL is a type-oriented language. These types are built in or the user can create and define them. The flexibility of users being able to create their own types is a powerful tool to write code effectively. The user created types also support flexible coding. It also supports multidimensional arrays. Another type it supports is the physical type, which is more synthesizable or targeted design code.

- **Ease of Learning**- Its is said that for beginners, VHDL may seem harder than Verilog due to the rigid type requirements. However advanced users may think these rigid type requirements are easier to handle.

- **Libraries and Packages**- Packages are used to target certain designs. They include procedures and functions and can be made available to any module that needs to use it. These are attached to the standard VHDL library. For example if a system to be modeled/designed includes arithmetic functions, a package can be used that includes those functions.

- **Operators**- An extensive set of operators is available in VHDL but it does not have predefined unary operators.

- **Procedures and Tasks**- In VHDL concurrent procedure calls are allowed. VHDL differs to Verilog in this sense because it allows a function to be written

inside the procedure's body. This feature makes it easier to describe a complex system.

### 3.5.3. Verilog

Verilog adopted its name from the logic simulator that originally used it. Verilog is considered to be better when describing a system at the gate or transistor level due to its use of predefined primitives at this level.

- **Data Types-** Compared to VHDL, Verilog data types are very simple and easy to use. All types are defined by the language, therefore there are no user defined types. It is said that beginners consider these simple data types as an advantage over VHDL. Moreover Verilog cannot handle objects with multidimensional array types.

- **Ease of Learning-** Verilog is considered to be easier to learn than VHDL. Users can just write the module without worrying about what library or packages should be attached. Also Verilog is thought to be easier for most people because many statements are similar to those in C language and most people are familiar with C language over hardware description languages.

- **Libraries and Packages:-** There is no concept of libraries or packages in Verilog.

- **Operators-** An extensive set of operators is also available in Verilog and unlike VHDL, Verilog does have pre-defined unary operators.

- **Procedures and Tasks-** In Verilog concurrent task calls are allowed. Functions, however, are not allowed to be written in the task's body.

### 3.5.4. HDL code generators

Using HDL could be tedious and required some time. To avoid this time there are graphical development software that facilitate the design and coding in HDL. Below in sections 3.5.4.1 and 3.5.4.2 the two leaders in the HDL coding industry will be explored further.

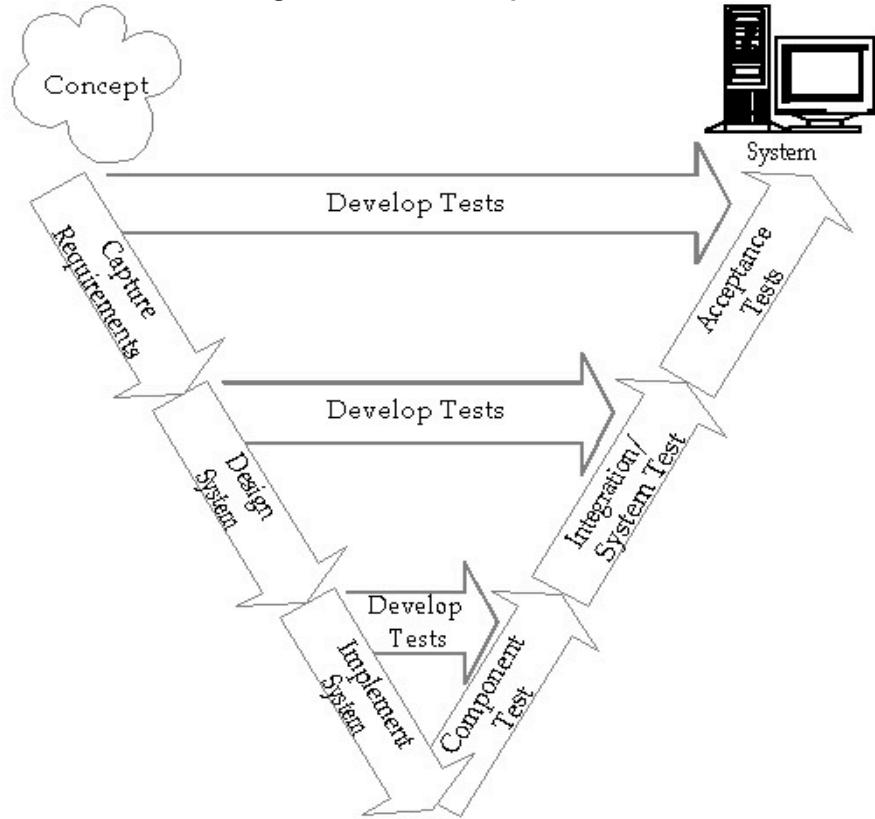

#### 3.5.4.1. Simulink: HDL Coder and HDL Verifier

Discovering this tool was a very good advantage for this project. Simulink is very powerful graphical development software developed by MathWorks. It is used for modeling, simulating and analyzing multi-domain dynamic electronic systems. Its graphical block diagramming tool and a customizable set of block libraries make it easier to use for people that are not experts in programming but do understand electronic circuits. One of the reasons why our group benefited from using this software is because it offers tight integration with the rest of the MATLAB environment and can either drive MATLAB or be scripted from it. In the specific case of this project we would use it with a specific set of add-ons: the HDL Coder and HDL Verifier.

HDL coder is a tool that generates portable, synthesizable Verilog and HDL code from MATLAB functions, Simulink models and state-flow charts. This generated

HDL code can be used for FPGA programming. The generated HDL code can be used for FPGA programming. This code generator is compatible with Xilinx and Altera FPGAs. It gives you the flexibility to control HDL architecture and implementation, highlight critical paths and generate estimates hardware resource utilization. It also provides traceability that will connect the various parts of the Verilog or VHDL code with the Simulink model. Creating HDL code with this software can be done in a few steps. First the designer has to model the target design using a combination of MATLAB code, Simulink blocks and Stateflow charts. Then optimize these models to meet speed design objectives, generate the HDL code using the HDL Workflow Advisor for MATLAB and Simulink and finally verify the generated code with HDL Verifier. The information from this section was gathered from [23] and [24]. Below we will break this process into sections and explain further how Simulink performs each task:

#### **Code Generation:**

When generating HDL or Verilog code from MATLAB the HDL Workflow advisor will convert the MATLAB code from floating-point to fixed-point and generate the HDL code desired. This tool lets the designer model an algorithm at high level using the MATLAB structure while providing options for generating HDL code that is optimized for hardware implementation. Another advantage of this is that most already written libraries in MATLAB can be used. If the code is being generated from Simulink the HDL Workflow Advisor will generate the HDL code from Simulink and Stateflow. In Simulink there are libraries with more than 200 blocks that can be used to model an algorithm.

#### **Code Optimization:**

This can be achieved by using pipelining, streaming, and resource sharing. For example in Simulink one can implement multichannel designs and serialization techniques which are common to multimedia and DSP applications which pertain to this project.

#### **FPGA Design:**

HDL Workflow Advisor in HDL coder automates the workflow for implementing MATLAB algorithms and models into the two compatible FPGAs (Xilinx and Altera). Using HDL Workflow Advisor integrates all the steps of the FPGA design process:

- Verifying Simulink Model for HDL code generation compatibility

- Generating HDL code, an HDL test bench and co-simulation model

- Performing synthesis and timing analysis through integration with Xilinx ISE and Altera Quartus II

- Estimating resources used in the design

- Back annotating the Simulink model with critical path timing

#### **Verifying the HDL Code:**

HDL Coder works together with HDL Verifier generate two types of co-simulation models:

- HDL co-simulation model, for performing HDL co-simulation with Simulink and an HDL simulator

- FPGA-in-the-loop (FIL) co-simulation model, for verifying your design with Simulink and an FPGA board

#### **Tracing the HDL Code:**

HDL Coder documents the generated code in an HTML format that contains hyperlinked HDL code and a table of generated HDL files. These hyperlinks connect the generated code to the corresponding part of the MATLAB algorithm or Simulink block that created that part of the code. It also allows you to insert user comments and descriptions to improve code readability

#### **Key Features and Conclusion:**

After taking a deeper look at this software we think it would be great if it is used in this project. It is very user friendly and does not require prior experience in HDL programming. Below there is a summary of all the key features that are offered with this type of software:

- Target-independent, synthesizable VHDL and Verilog code

- Code generation support for MATLAB functions, System objects, and Simulink blocks

- Mealy and Moore finite-state machines and control logic implementations using Stateflow

- Workflow advisor for programming Xilinx and Altera application boards

- Resource sharing and retiming for area-speed tradeoffs

- Code-to-model and model-to-code traceability

- Legacy code integration

#### **3.5.4.2. Labview FPGA Module: DSP Design**

This program is very much like Simulink in the aspect that it is used with the to facilitate FPGA programming to inexperienced HDL programmers. Some of the advantages of using this module over traditional HDL language is that it allows the user to prototype real-time FPGA-based digital signal processing subsystems, effortlessly integrate complex FPGA based math and signal processing libraries, design signal processing blocks , import third-party IP blocks and finally investigate design trade-offs early in the design process.

LabVIEW DSP Design for the LabVIEW FPGA Module reduces the complexity of designing real-time DSP subsystems for high-speed field-programmable gate array (FPGA) applications such as RF and communications. By using a stream-based graphical abstraction, the designer can rapidly implement an algorithm, explore design trade-offs, and generate an optimized FPGA implementation. The designer can then integrate the resulting implementation as a modular part of a larger LabVIEW FPGA-based application. Below it is explained in more detail how this module performs some of its important functions. The information covered in this section was gathered from [27].

### **Quick Prototype Real-Time FPGA-Based DSP Subsystems:**

LabVIEW DSP Design offers an intuitive language that extends LabVIEW FPGA by providing a target-independent description of the DSP algorithm. Multi-rate DSP algorithms are described by combining high-level functional blocks that explicitly describe sample counts at the inputs and outputs of each block. LabVIEW DSP Design combines the sample counts of the inputs and outputs of each block with known cycle-level timing to determine optimal scheduling, memory, and FPGA resource utilization. You can compile the resulting algorithms into reusable blocks and integrate them into larger LabVIEW FPGA-based applications for execution on compatible NI reconfigurable I/O FPGA devices.

### **Design Trade-Offs:**

With LabVIEW DSP Design, the user can effectively understand and optimize these design aspects early in the design process. In addition to cycle-accurate simulation for algorithmic verification, this module helps the designer to achieve a detailed look at execution scheduling. Using the Scheduling view, you can analyze trade-offs between latency and resource utilization. By enabling pipelining and changing memory buffer sizes, you can profoundly impact how high-speed, multi-rate applications execute.

## **3.6. FPGA Chip**

### **3.6.1. Overview**

Modern programmable hardware allows users to send data to a programmable chip to tell the chip how to wire itself. Modern hardware compilers can take this high level description of an electronic circuit and translate it into configuring bit strings, which are used to configure a programmable chip (FPGA). Inside a chip there are a lot of programmable logic gates, which allow placing a whole electronic system on a single chip. This is the reason why electronics today are more sophisticated, powerful and cheaper than before. A disadvantage of this is that electronics become harder to design. Some sources say that "it's almost as easy to program hardware as to program software" but in order to program hardware well the designer needs to understand the principles of digital electronic design for example multiplexors, flip flops, buffers, and counters among others which could be challenging.

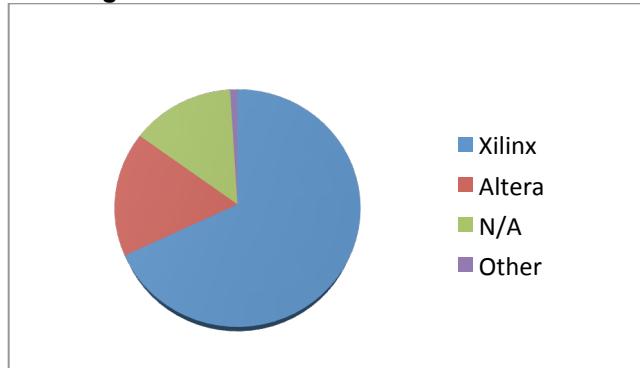

Figure 9: FPGA Preferred Vendors 2012

Image courtesy of Synopsys. Permission:6

The information in figure 9 above is obtained from *FPGA-based Pricing Methodology Manual (FPMM)* by *Synopsys, Inc.* By looking at the numbers on the graph is it evident that Xilinx is the leader in the FPGA market although it is said that Altera has more tools that will help the programmer especially if they are not seasoned in hardware description languages. In the next sections 3.6.2 and 3.6.3 we will discuss the major differences and from these we will come to a decision on which FPGA chip to use for our project.

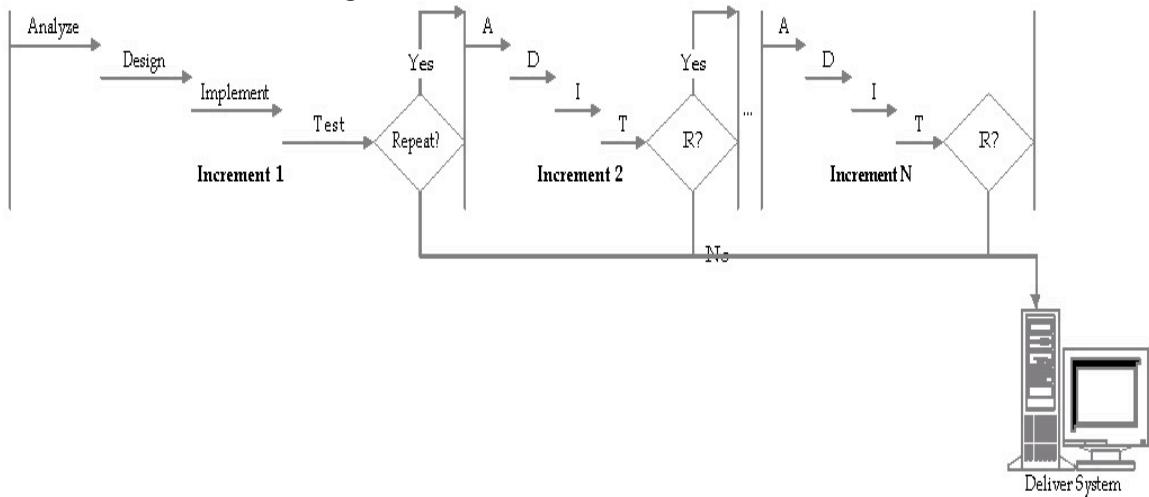

### 3.6.2. Architecture of the Chip

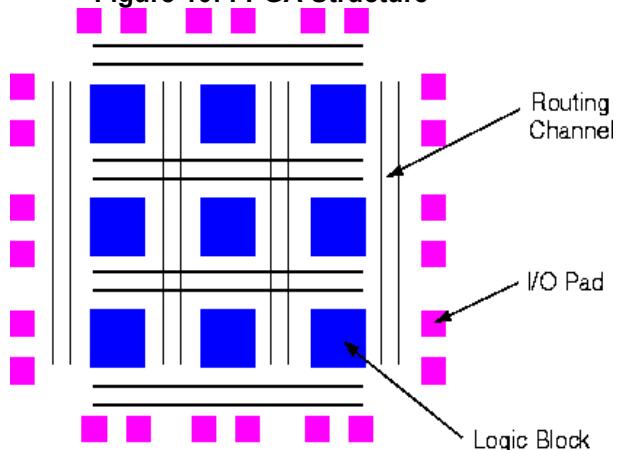

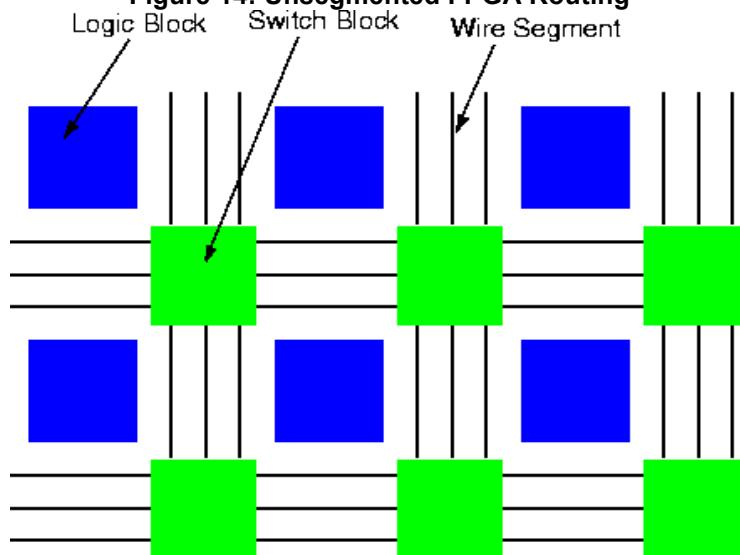

To understand a little more about the design of the FPGA the designer needs to understand the basic architecture of the chip. A set of figures and descriptions will be used for an easy understanding of such complex device. In section 3.4.1 is explained that FPGAs are semiconductor devices that are based around a matrix of configurable logic blocks connected via programmable interconnects that could be programmed depending on the application requirements. In figure 10 below a simple FPGA structure is shown. Two input/output pads fit into the height of one row or the width of one column. All the routing channels have the same width or number of wires.

Figure 10: FPGA Structure

Image courtesy of Dept. of Electrical Engineering at UT. Permission:5

Each circuit has to be mapped into the smallest square that can accommodate it. For example a circuit containing 8 logic blocks and 6 input/outputs pads could be mapped into an FPGA consisting of a 3x3 array of logic blocks like the one shown above. If more blocks or input/output pads are needed then a bigger configuration will be needed.

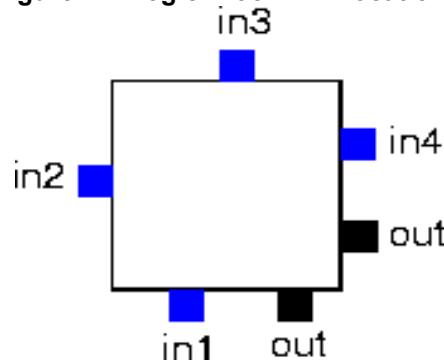

A logic block inside an FPGA usually consists of a few logical cells, these cells are often called ALM, LE, or Slice. A typical cell consists of a 4-input look-up table (LUT), a Full adder and a flip-flop, as shown below in figure 11. As seen in the figure the LUTs are split into two 3-input LUTs. In normal mode these are combined into a 4-input LUT through the first (left) mux. In arithmetic mode, the outputs are fed to the full adder. The selection of mode is then programmed or sent to the middle multiplexer. The output can be selected to be synchronous or asynchronous depending on the programming of the right most mux. In practice, entire or parts of the FA are put as functions into the LUTs in order to save space.

Figure 11: Logic Block Structure

Image courtesy of Dept. of Electrical Engineering at UT. Permission:5

In the figure above we can see the blue circles correspond to the inputs and the black circle corresponds to the output. Figures 12 and 13 are color coded so the reader can match up the location of the FPGA logic block pins and correlate both figures. In figure 12 below it is clear that each input is accessible from one side of the logic block, while the output pin can connect to routing wires in both the channel to the right and the channel below the logic block.

Figure 12: Logic Block Pin Locations

Image courtesy of Dept. of Electrical Engineering at UT. Permission:5

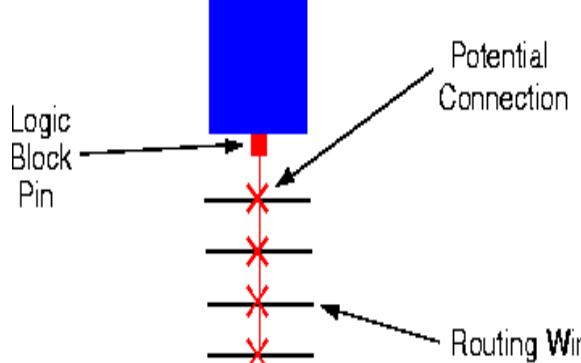

Each logic block input and output pins can connect to any one of the wiring segments in the channel bordering to it. In the same way, an input/output pad can connect to any one of the wiring segments in the channel adjoining to it. As seen in the picture below a channel can have multiple wires, also called channel width. For example, an input/output pad at the bottom of the chip can connect to any of the wires in the horizontal channel immediately below it as seen in figure 13.

**Figure 13: Logic Block Pin to Routing Channel Interconnect**

Image courtesy of Dept. of Electrical Engineering at UT. Permission:5

The red crosses in the figure above point at the possible connections that the input/output pad can have. There are various choices but it is important to know that only one wire segment may be connected to a logic block input pin.

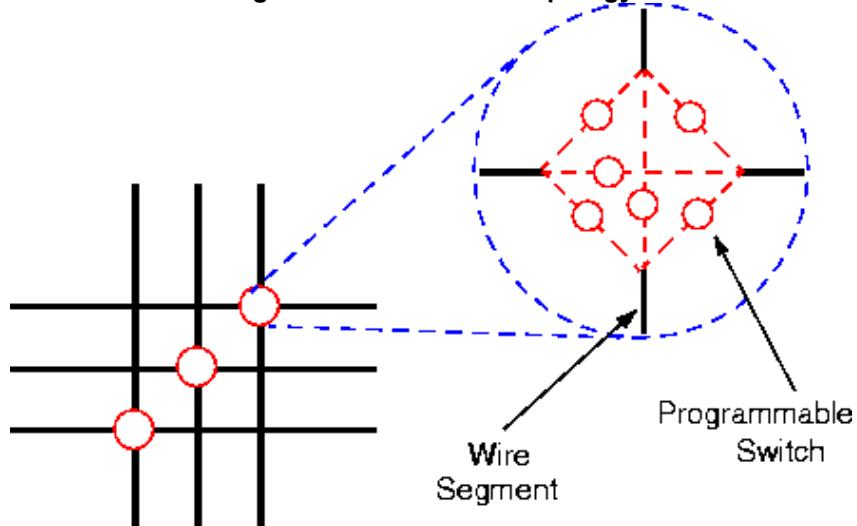

Moreover FPGAs are typically unsegmented, this means that each wiring segment passes through only one logic block before it reaches a switch box. By turning on some of the programmable switches within a switch box, longer or shorter paths can be constructed. Some FPGAs architectures use longer routing lines that pass through multiple logic blocks to provide high speed interconnects. In the figure 14 below it is clear where these switch boxes are located.

**Figure 14: Unsegmented FPGA Routing**

Image courtesy of Dept. of Electrical Engineering at UT. Permission:5

In every section where the vertical and horizontal channels intersect there is a switch box. Since in this particular figure we can see a width of 3 because a channel has 3 wires the switch box will have three programmable switches that allow it to connect to three other wires in adjoining channel segments. This configuration is often called planar or domain-based switch box topology. One more thing that need to be understood from this topology is that since each channel has multiple wires these wires correspond to the same wire number in the adjoining channel. For example wire 1 in the vertical channel will only connect to wire 1 in the horizontal channel, same applies for wires two and three. This may seem confusing but in figure 15 there is a zoomed in view of the channel connections and the switch box. The programmable switch would be set to best suit the desired application which for this project was digital signal processing.

Figure 15: Switch Box Topology

Image courtesy of Dept. of Electrical Engineering at UT. Permission:5

### 3.6.3. Xilinx Chip

Xilinx are the pioneers in FPGAs. They invented the first commercially viable FPGA in 1985 [28]. Since then they control over half of the FPGA market. Xilinx offers a variety of FPGA families that vary from low-end products to high-end devices. The different families of FPGAs provided by Xilinx are:

- **Spartan**- Provide optimal balance of low risk, low cost and low power for cost sensitive applications.

- **Artix & Kintex**- Provides performance and power balance for mid-range applications.

- **Virtex**- Provides high bandwidth and high performance for high end designs.

These families of FPGAs are listed in Table 4 below. The table discusses many features that are critical for the decision making on which FPGA to use.

**Table 4: Xilinx FPGAs Features**

| Features                                  | Artix-7                             | Kintex-7                            | Virtex-7                            | Spartan-6                    |

|-------------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|------------------------------|

| Logic Cells                               | 215,000                             | 480,000                             | 2,000,000                           | 150,000                      |

| BlockRAM                                  | 13Mb                                | 34Mb                                | 68Mb                                | 4.8Mb                        |

| DSP Slices                                | 740                                 | 1,920                               | 3,600                               | 180                          |

| DSP Performance (symmetric FIR)           | 930GMACs                            | 2,845GMACs                          | 5,335GMACs                          | 140GMACs                     |

| Transceiver Count                         | 16                                  | 32                                  | 96                                  | 8                            |

| Transceiver Speed                         | 6.6Gb/s                             | 12.5Gb/s                            | 28.05Gb/s                           | 3.2Gb/s                      |

| Total Transceiver Bandwidth (full duplex) | 211Gb/s                             | 800Gb/s                             | 2,784Gb/s                           | 50Gb/s                       |

| Memory Interface (DDR3)                   | 1,066Mb/s                           | 1,866Mb/s                           | 1,866Mb/s                           | 800Mb/s                      |

| PCI Express® Interface                    | x4 Gen2                             | x8 Gen2                             | x8 Gen3                             | x1 Gen1                      |

| Agile Mixed Signal (AMS)XADC              | Yes                                 | Yes                                 | Yes                                 |                              |

| Configuration AES                         | Yes                                 | Yes                                 | Yes                                 | Yes                          |

| I/O Pins                                  | 500                                 | 500                                 | 1,200                               | 576                          |

| I/O Voltage                               | 1.2V, 1.35V, 1.5V, 1.8V, 2.5V, 3.3V | 1.2V, 1.35V, 1.5V, 1.8V, 2.5V, 3.3V | 1.2V, 1.35V, 1.5V, 1.8V, 2.5V, 3.3V | 1.2V, 1.5V, 1.8V, 2.5V, 3.3V |

| EasyPath Cost Reduction Solution          | -                                   | Yes                                 | Yes                                 | -                            |

Image courtesy of Xilinx All-Programmable. Permission:9

The table above was obtained from the Xilinx website [28]. Some of the features the group will take into account to make a decision are: the amount of logic cells, RAM, DSP slices, Memory interface, and I/O pins. From the Xilinx families mentioned above the group would be leaning towards the Spartan-6 because it is a low cost design that will perform the video processing required in this project. Some of the benefits of the Spartan-6 low cost family of FPGAs are:

- Designed for low cost

- Low static and dynamic power

- Multi-voltage, multi-standards Select IO interface banks

- Low-cost PCI technology support compatible with the 33MHz, 32- and 64-bit specification

- Efficient DSP48A1 slices

- Integrated memory controller blocks

- Abundant logic resources with increased logic capacity

- Block RAM with a wide range of granularity

- Clock management Tile (CMT) for enhanced performance

- Simplified configuration- to support low-cost standards

- Enhancement security for design protection

- Faster embedded processing with enhanced, low cost MicroBlaze soft processor

- Industry-leading IP and reference designs

### 3.6.4. Altera Chip

Altera are the second leaders in the FPGA market. They control about thirty percent of the market. Altera also offers a variety of FPGA families for different purposes. The FPGA families that Altera offers are:

- **Cyclone**- Provides low cost and low power design.

- **Arria**- Provides optimal balance of performance, power and price for mid-range applications.

- **Stratix**- Provides high bandwidth for high end applications.

For this project, the low end Cyclone model will suffice. Below there is a table taken from the Altera website [29] that describes the advantages of using a Cyclone III from video and image processing applications like the ones used in this project.

**Table 5: Video and Image Processing Application Advantages of Cyclone III FPGAs**

| Feature                                                            | Advantage                                                                                                                                             |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| <a href="#"><b>Abundant Memory at Every Density</b></a>            | Up to 4 Mbits of on-chip memory architected for video frame buffering.                                                                                |

| <a href="#"><b>Digital Signal Processing (DSP) Multipliers</b></a> | Up to 288 embedded 18-bit x 18-bit multipliers at 260 MHz performance to process DSP-intensive video algorithms.                                      |

| <a href="#"><b>Video and Image Processing (VIP) Suite</b></a>      | A suite of nine pre-optimized video and image intellectual property (IP) cores, including deinterlacer, scaler, and filters to increase productivity. |

| <a href="#"><b>Nios® II Embedded Soft Processor</b></a>            | The world's most versatile embedded soft processor, ideal for implementing a low-cost microcontroller.                                                |

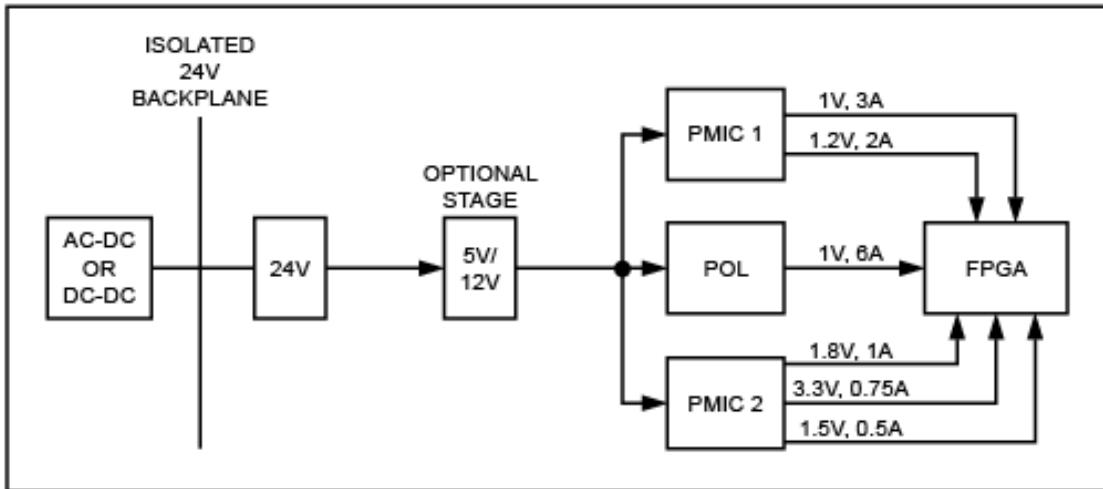

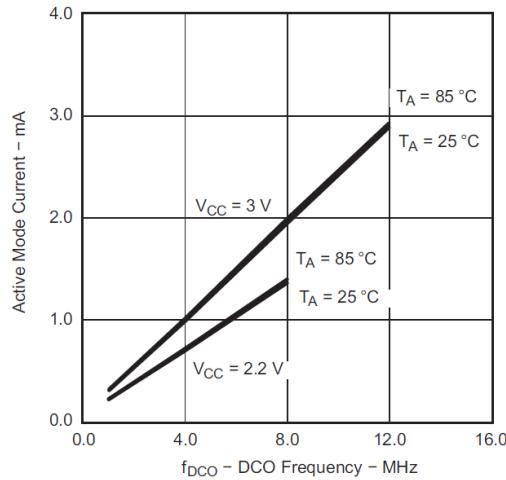

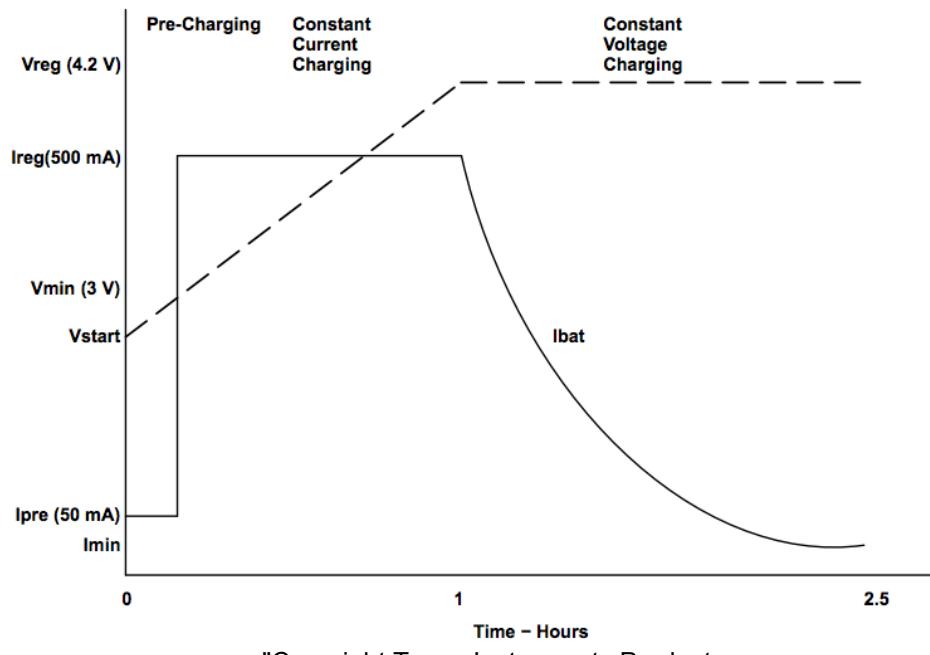

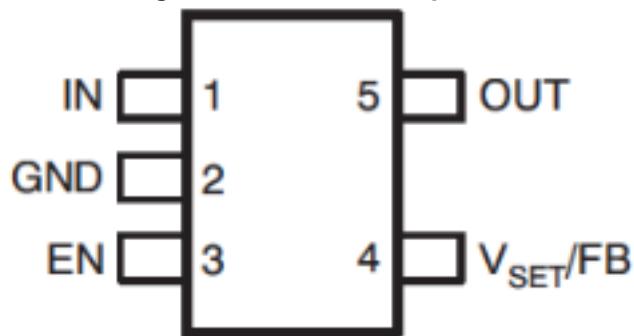

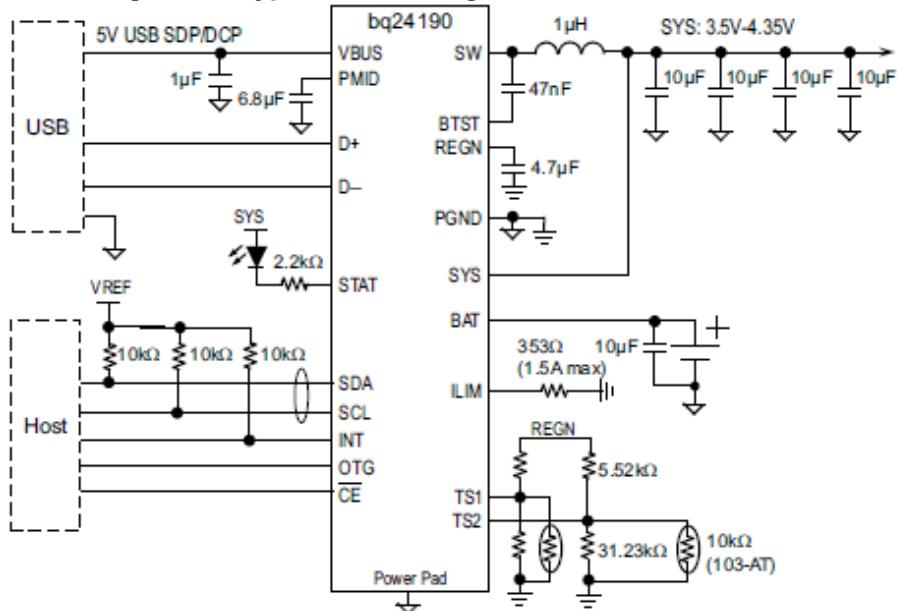

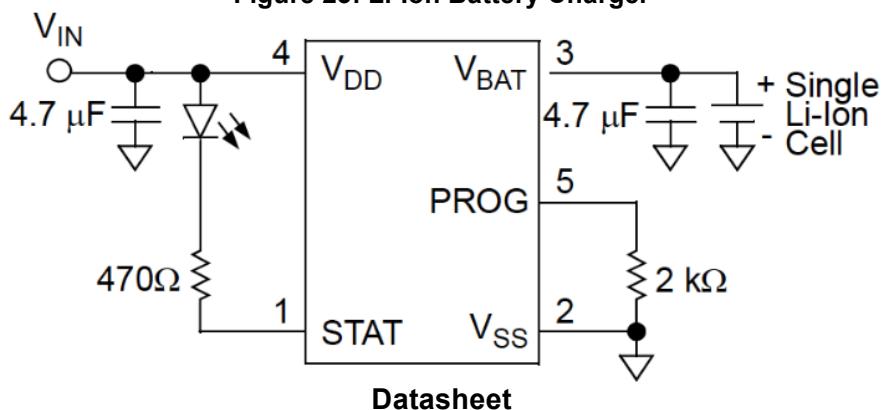

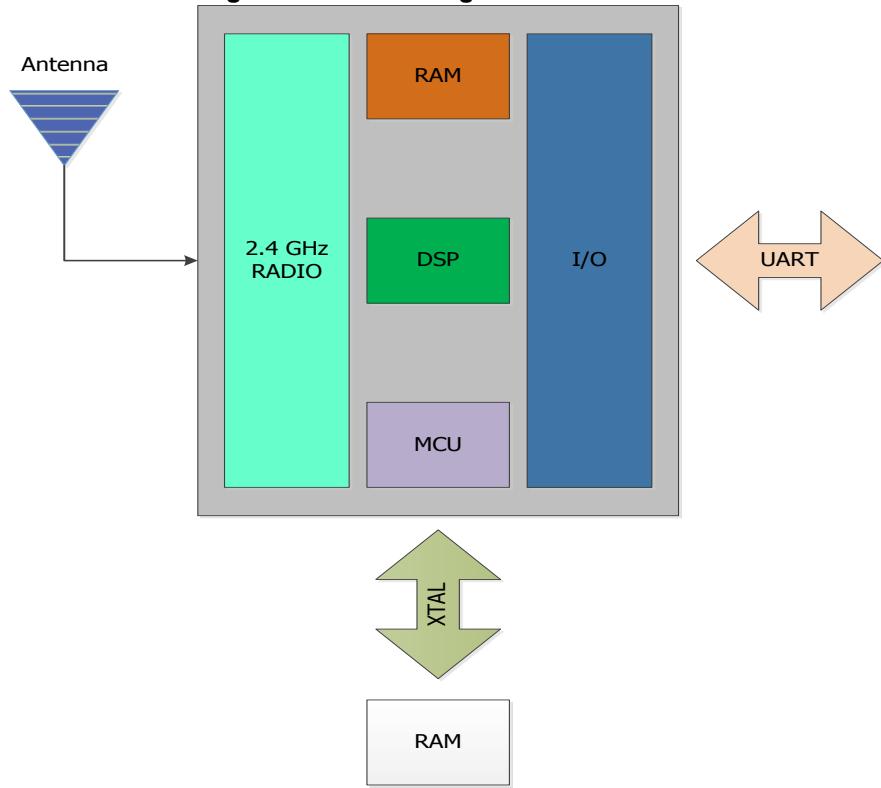

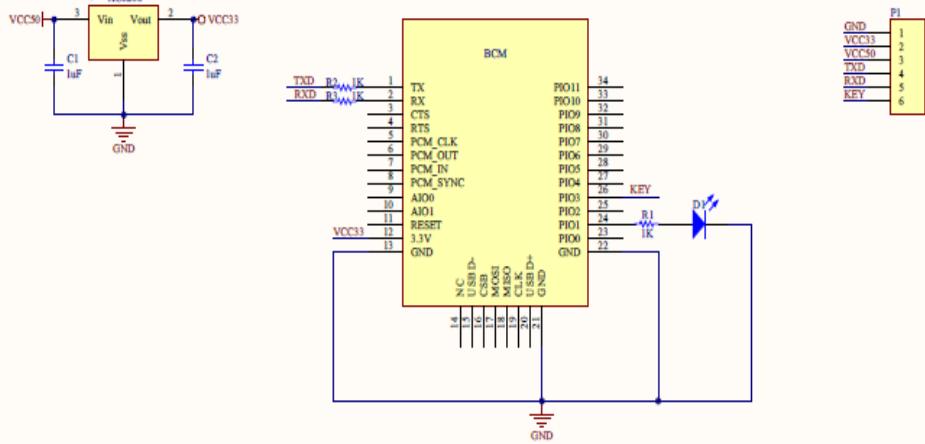

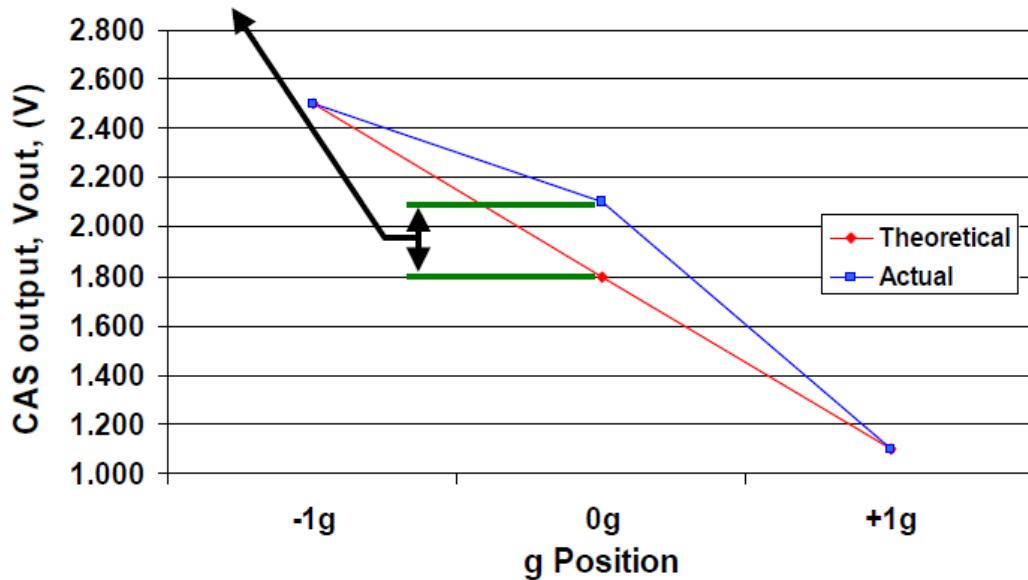

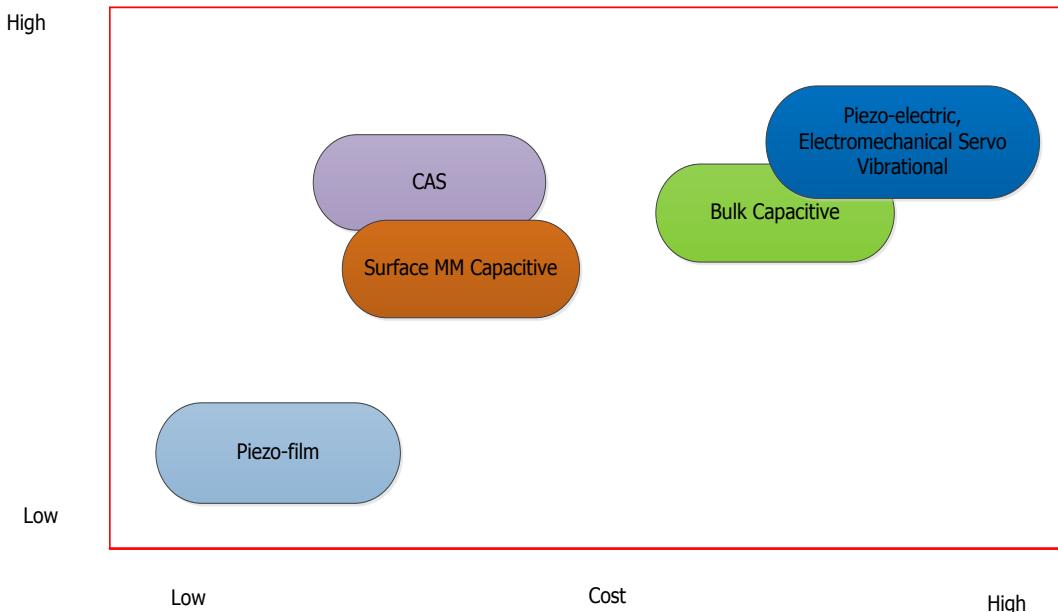

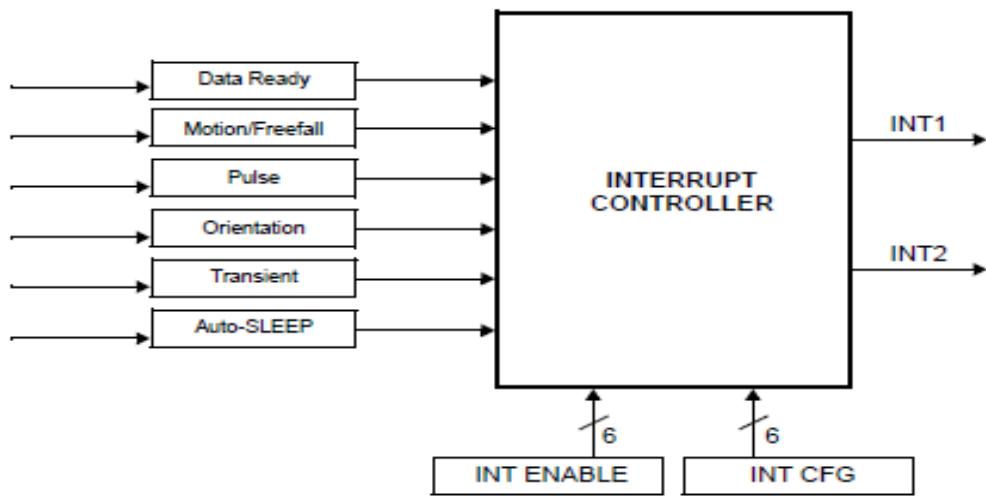

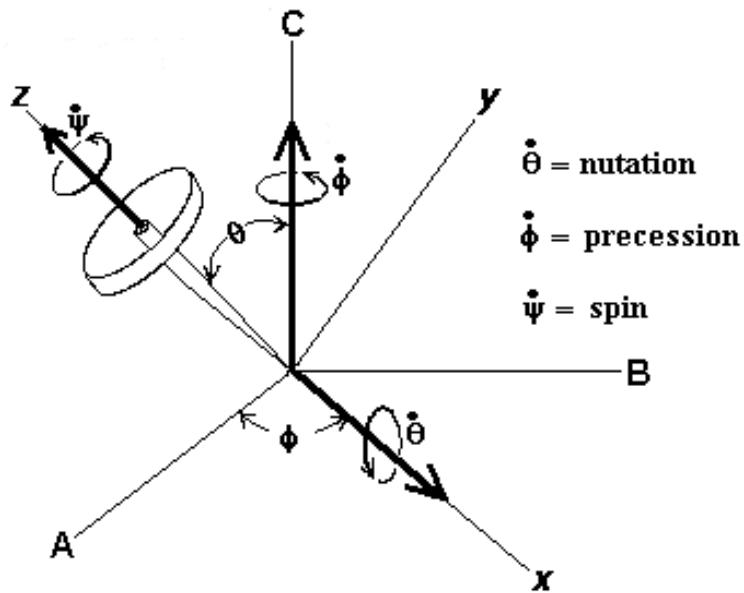

Image courtesy of Altera. Permission:10