# Flashback

Senior Design II

Group 22:

Marlon De La Cruz

**Rene Martinez**

**Trenton Reed**

**Marlon Smith**

## Table of Contents

| 1.0 Executive Summary                           | 1    |

|-------------------------------------------------|------|

| 2.0 Project Description                         | 2    |

| 2.1 Project Motivation and Goals                | 2    |

| 2.2 Objectives                                  |      |

| 2.3 Project Requirements and Specifications     |      |

| 2.3.1 Project Requirements                      |      |

| 2.3.2 Minimal Technical Hardware Specifications |      |

|                                                 |      |

| 3.0 Research Related to Project Definition      | 7    |

| 3.1 Digital Video Recorder Research             |      |

| 3.1.1 Overview                                  |      |

| 3.1.2 Features                                  |      |

| 3.1.3 Cost of DVR                               | 8    |

| 3.2 FPGA vs DSP                                 | 9    |

| 3.2.1 Overview                                  | 9    |

| 3.2.2 Performance                               | 9    |

| 3.2.3 Power Consumption                         | . 10 |

| 3.3 Digital Signal Processor                    |      |

| 3.3.1 Arithmetic Format and Data Width          |      |

| 3.3.2 Speed and Memory                          | . 13 |

| 3.3.3 Peripherals                               | . 15 |

| 3.3.3.1 USB                                     | . 15 |

| 3.3.3.2 Ethernet                                | . 15 |

| 3.3.3.3 Inter-Integrated Circuit Bus            |      |

| 3.3.3.4 Multichannel Audio Serial Port          | . 16 |

| 3.3.4 Video                                     | . 17 |

| 3.3.5 Power                                     | . 17 |

| 3.4 SATA Controller                             |      |

| 3.5 Digital Image Processing                    |      |

| 3.6 Object Resolution                           |      |

| 3.7 Real-time Processing                        |      |

| 3.8 MPEG                                        |      |

| 3.8.1 H.264                                     |      |

| 3.9 Video Tuners                                |      |

| 3.9.1 PLL Frequency Synthesizer                 |      |

| 3.10 Grounding in Mixed Signal Systems          |      |

| 3.11 DDRx SDRAM                                 |      |

| 3.12 Thermistor vs Analog Temperature Sensor    |      |

| 3.13 Debugging                                  |      |

| 3.14 ADC and DAC                                |      |

| 3.15 SPDIF                                      |      |

| 3.16 Hard Disk Drives                           |      |

| 3.17 Solid State Drives                         | 29   |

| 3.17.1 Single Layer Cell vs. Multi-Layer Cell    | . 32 |

|--------------------------------------------------|------|

| 3.18 Software Operating Environment              |      |

| 3.18.1 Operating Systems                         |      |

| 3.18.2 FreeRTOS                                  |      |

| 3.18.3 ArchLinux ARM                             | . 33 |

| 3.19 Software Development Environment            | . 34 |

| 3.19.1 Microsoft Visual Studio 2012 Professional |      |

| 3.19.2 Qt Creator                                | . 35 |

| 3.20 Signal Mediums                              | . 36 |

| 3.20.1 Coaxial Cable                             |      |

| 3.20.2 Component Video                           | . 38 |

| 3.20.3 Composite Video – RCA                     | . 38 |

| 3.20.4 High Definition Multimedia Interface      | . 38 |

| 3.20.5 Over-The-Air Transmission                 |      |

| 3.21 Media Processor Research                    | . 41 |

| 3.21.1 ARM Architecture                          | . 41 |

| 3.21.2 BroadCom BCM 2835                         | . 42 |

| 3.21.3 Texas Instruments OMAP                    | 42   |

| 3.21.3.1 OMAP 3                                  | . 43 |

| 3.21.3.2 OMAP 4                                  | . 43 |

| 3.21.3.3 OMAP 5                                  | . 44 |

| 3.22 User Interface Communications               | . 44 |

| 3.22.1 Infrared Remote Control                   | . 44 |

| 3.22.2 Phillips RC-5 Protocol                    | . 45 |

| 3.22.3 Radio Frequency Remote Control            |      |

| 3.22.4 Device Controls.                          |      |

| 3.22.5 Seven Segment Liquid Crystal Display      |      |

| 3.22.6 Universal Serial Bus v2.0                 |      |

| 3.23 Power Electronics and Heat Dissipation      | . 50 |

| 3.23.1 AC - DC Converter                         |      |

| 3.23.2 Linear Regulators                         |      |

| 3.23.3 Non - Inverting Operational Amplifiers    |      |

| 3.23.4 Flyback Converter                         |      |

| 3.23.5 FÉT Load Switch                           |      |

| 3.23.6 Electrostatic Discharge Protection        |      |

| 3.24 Audio Line Driver                           |      |

| 3.25 Related Products                            |      |

| 3.25.1 Comskip                                   |      |

| 3.25.2 ReplayTV                                  |      |

| 3.25.3 AutoHop                                   |      |

|                                                  |      |

| 4.0 Project Hardware and Software Details        | . 58 |

| 4.1 Video Signal Input/Source                    |      |

| 4.1.1 Over-The-Air Television                    |      |

| 4.2 Hauppauge WinTV-HVR-950Q Tuners              |      |

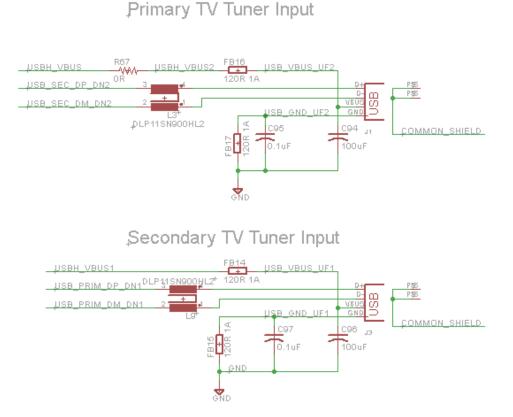

| 4.3 TV Tuner Input                               |      |

|                                                  |      |

| 4.4 Gumstix Overo® TidalSTORM                      | . 61 |

|----------------------------------------------------|------|

| 4.5 MicroSD                                        | . 63 |

| 4.6 User Interface                                 | . 64 |

| 4.6.1 Infrared Sensor                              | 65   |

| 4.6.2 Liquid Crystal Display                       | . 66 |

| 4.7 DVI-D                                          | . 67 |

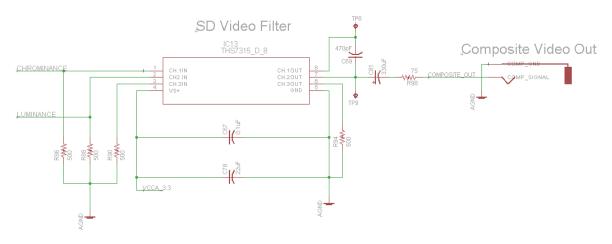

| 4.8 Standard Definition Video Filter               | . 68 |

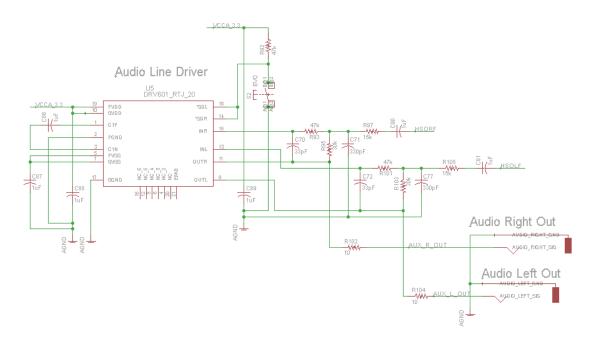

| 4.9 Audio Line Driver                              | . 68 |

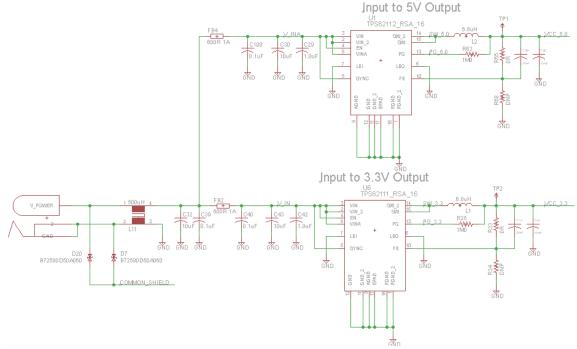

| 4.10 Power Electronics                             | . 70 |

| 4.10.1 AC – DC Converter                           | . 70 |

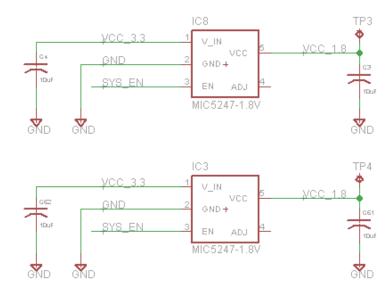

| 4.10.2 Power ICs                                   | . 70 |

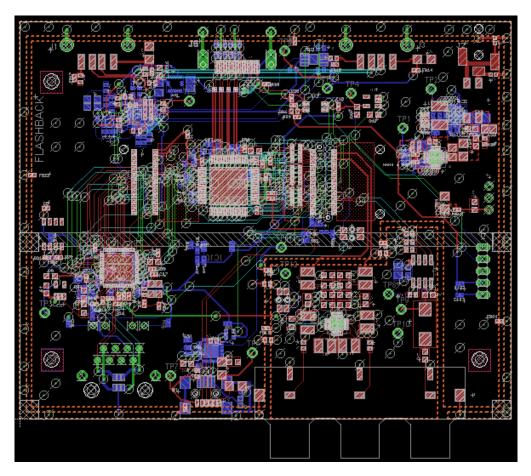

| 4.11 PCB                                           | . 73 |

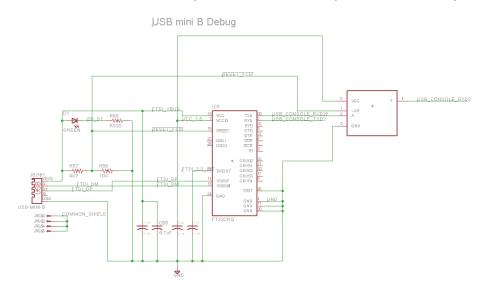

| 4.12 Debug                                         | . 74 |

| 4.13 Operating System                              |      |

|                                                    |      |

| 5.0 Design Summary of Hardware and Software        | . 76 |

| 5.1 Graphical User Interface (GUI) and Overlay     | . 76 |

| 5.2 Flashback Algorithm Analysis                   |      |

| 5.3 Hardware System Overview                       | . 81 |

|                                                    |      |

| 6.0 Project Prototype Construction and Coding      | . 85 |

| 6.1 Software Development Environment               |      |

| 6.2 Graphical User Interface Overlay Plan          | . 85 |

| 6.3 Flashback Hardware/Software Final Diagrams     | . 90 |

|                                                    |      |

| 7.0 Project Prototype Testing                      | . 91 |

| 7.1 Software Benchmarks                            | . 91 |

| 7.1.1 Commercial Detection Algorithm Efficiency    | . 91 |

| 7.1.2 Digital Video Recording Algorithm Efficiency | . 93 |

| 7.2 Hardware Benchmarks                            | . 94 |

| 7.2.1 User Interface                               | . 94 |

| 7.2.2 Power Electronics                            | . 95 |

|                                                    |      |

| 8.0 Administrative Content                         | . 96 |

| 8.1 Project Milestones                             | . 96 |

| 8.2 Final Budget and Cost Report                   |      |

| - · ·                                              |      |

| Appendices                                         | . 98 |

| Appendix A: Works Cited                            | . 98 |

| Appendix B: Permissions 1                          |      |

| •••                                                |      |

## Table of Figures

| Figure 3 – 1: DSP Memory Architecture 14                                             |

|--------------------------------------------------------------------------------------|

| Figure 3 – 2: Group of Pictures in (a) 'display' order and (b) 'bit stream' order 22 |

| Figure 3 – 3: Phase-Locked Loop Frequency Synthesizer          | 24 |

|----------------------------------------------------------------|----|

| Figure 3 – 4: Proper Grounding Scheme                          | 25 |

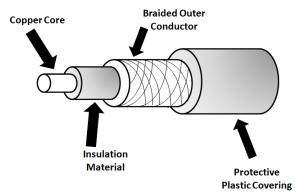

| Figure 3 – 5: A detailed cutaway of a Coaxial Cable            | 37 |

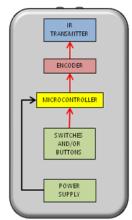

| Figure 3 – 6: Remote Control Button Layout                     | 45 |

| Figure 3 – 7: Remote Control General Block Diagram             | 45 |

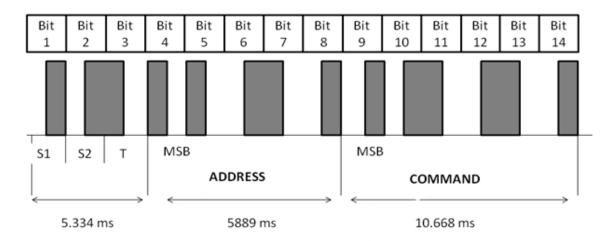

| Figure 3 – 8: RC5 Example Message Frame                        | 46 |

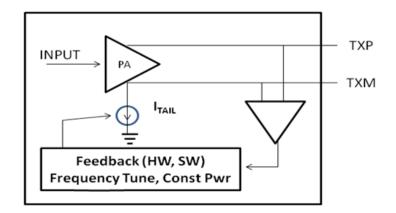

| Figure 3 – 9: Additional Feedback Loop for Antenna Tuning      | 47 |

| Figure 3 – 10: Flashback Device Controls                       |    |

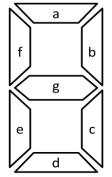

| Figure 3 – 11: Seven Segment LCD Individual Segment Definition | 48 |

| Figure 3 – 12: USB Cable                                       | 49 |

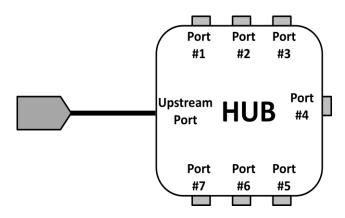

| Figure 3 – 13: Typical USB Hub                                 | 49 |

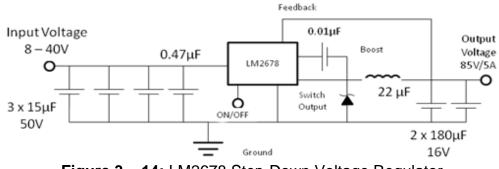

| Figure 3 – 14: LM2678 Step-Down Voltage Regulator              | 50 |

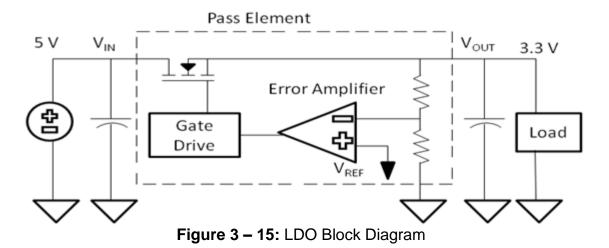

| Figure 3 – 15: LDO Block Diagram                               | 52 |

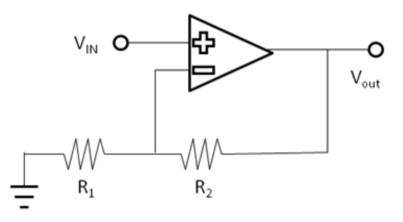

| Figure 3 – 16: Non – Inverting Operational Amplifier           | 53 |

| Figure 4 – 1: TV Tuner Connection                              |    |

| Figure 4 – 2: TV Tuner Schematic                               |    |

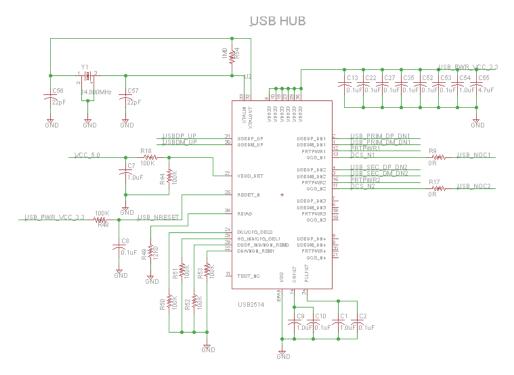

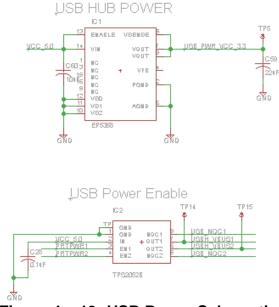

| Figure 4 – 3: USB Hub Schematic                                | 61 |

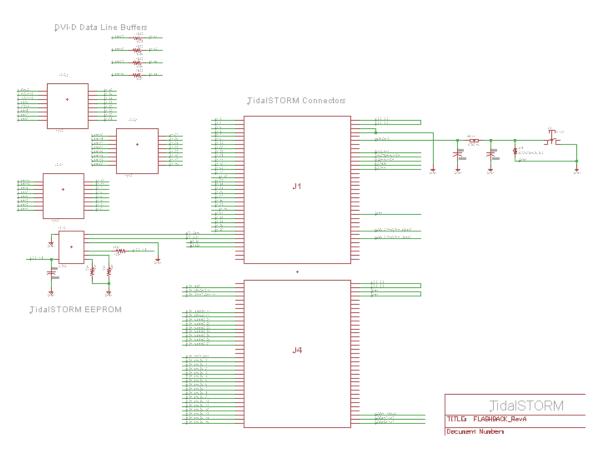

| Figure 4 – 4: TidalSTORM Connector Schematic                   | 62 |

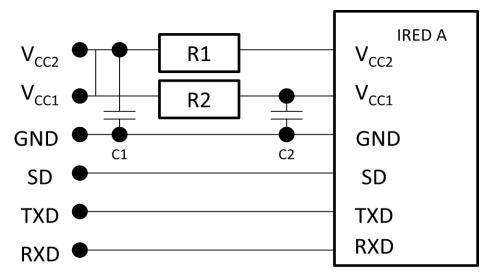

| Figure 4 – 5: TFBS4711                                         |    |

| Figure 4 – 6: Recommended Circuit Diagram                      |    |

| Figure 4 – 7: Four Character 7-Segment Display                 | 66 |

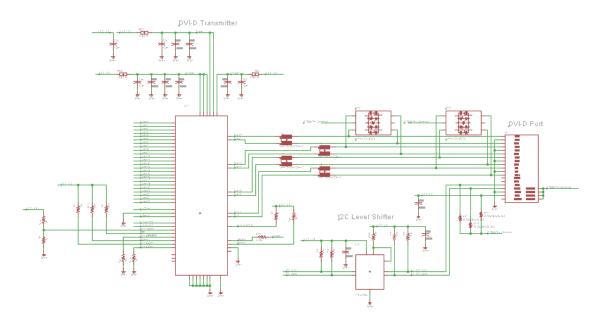

| Figure 4 – 8: DVI-D Schematic                                  | 67 |

| Figure 4 – 9: SD Video Filter Schematic                        |    |

| Figure 4 – 10: Audio Line Driver Schematic                     |    |

| Figure 4 – 11: Power ICs Schematic                             |    |

| Figure 4 – 12: MIC5247 Schematic                               |    |

| Figure 4 – 13: USB Power Schematic                             |    |

| Figure 4 – 14: PCB                                             |    |

| Figure 4 – 15: USB Mini Schematic                              |    |

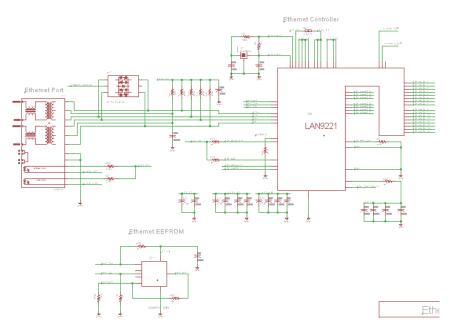

| Figure 4 – 16: Ethernet Schematic                              |    |

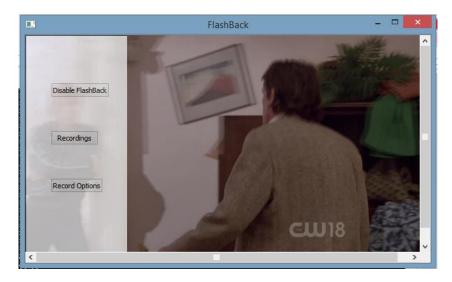

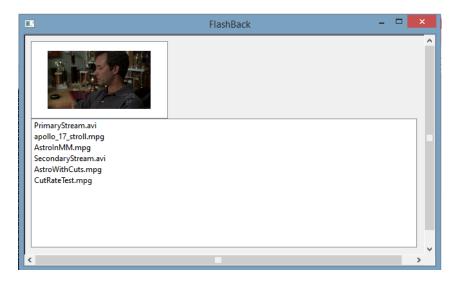

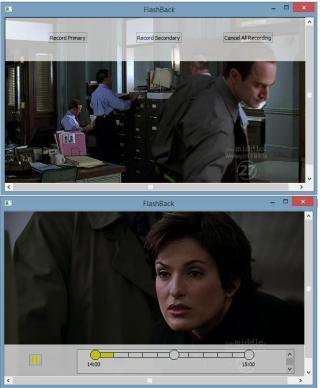

| Figure 5 – 1: GUI Side Menu                                    |    |

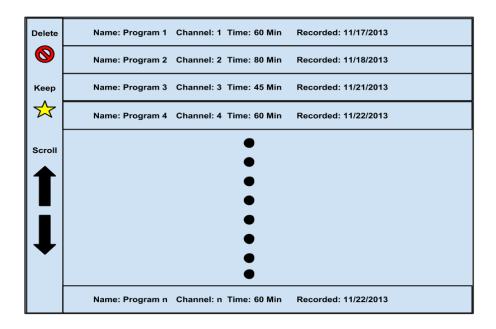

| Figure 5 – 2: Recordings List View Widget                      |    |

| Figure 5 – 3: Recording Options Menu                           |    |

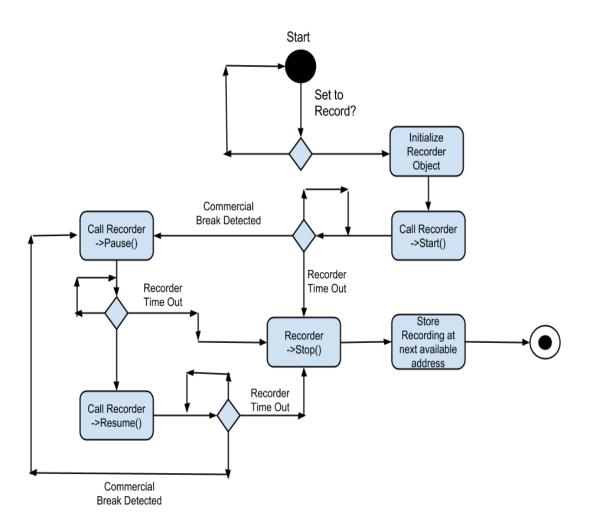

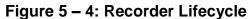

| Figure 5 – 4: Recorder Lifecycle                               | 81 |

| Figure 5 – 5: Flashback System Function Block Diagram          |    |

| Figure 6 – 1: Streaming Video from Qt Application              | 86 |

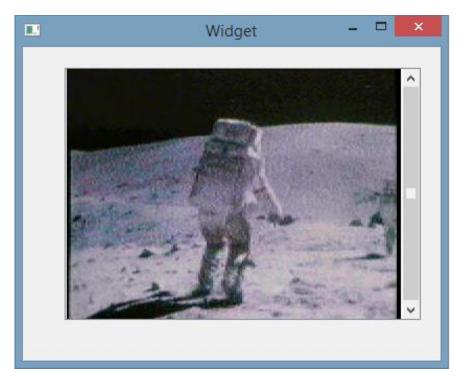

| Figure 6 – 2: Task Bar Style Menu                              | 87 |

| Figure 6 – 3: List View GUI Layout                             |    |

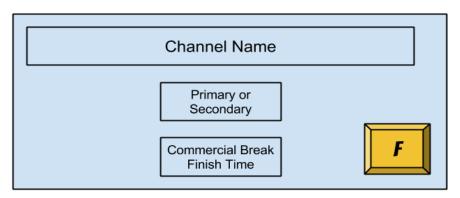

| Figure 6 – 4: Notification GUI Layout                          |    |

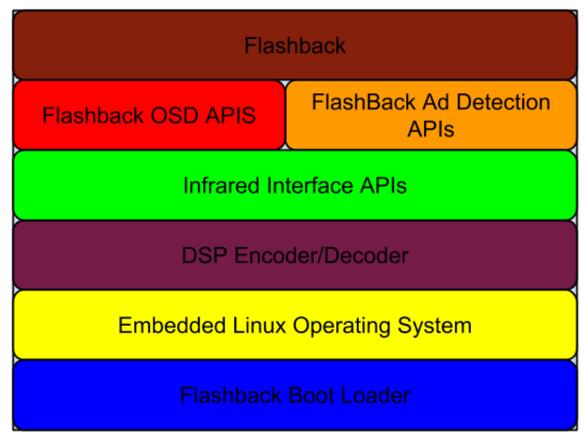

| Figure 6 – 5: Flashback Software Layers                        |    |

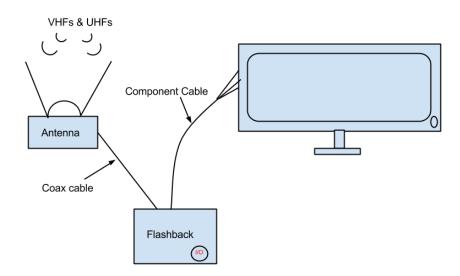

| Figure 6 – 6: Projected Flashback Setup                        |    |

| Figure 6 – 7: Channel Pivot GUI Layout 1                       | 01 |

## Table of Tables

| Table 3 – 1: Information provided from Afra and Kapadiya | 11 |

|----------------------------------------------------------|----|

| Table 4 – 1: Details of OTA Channels in Orlando          |    |

| Table 4 – 2: Specifications of ADATA SSD                 | 63 |

| Table 4 – 3: Specifications of Crucial v4 SSD            | 63 |

| Table 4 – 4: Specifications of Kingston SSDnow           |    |

| Table 4 – 5: Specifications of SanDisk Ultra Plus 2.5"   |    |

| Table 4 – 6: TFBS4711 Pin Description                    | 65 |

| Table 4 – 7: Analog Temperature Sensor Comparison        | 77 |

| Table 4 – 8: Specifications of SanDisk Ultra Plus 2.5"   | 78 |

| Table 4 – 9: LM96163 Pin Description                     |    |

### 1.0 Executive Summary

Flashback (patent pending) is a solution to the television viewer's problem of missing the action in their favorite programs. Flashback is a feature designed to detect the end of a commercial break in real-time. The user is able to enable our feature on a primary television signal of their choosing. After enabling Flashback, the user may freely roam to other secondary television signals without the worry of missing any action on the primary program. While the feature is enabled, Flashback will analyze the incoming primary television signal to detect the end of the commercial break on the primary program. When our feature determines the commercial break is ending, the user is prompted and asked if they would like to remain on the secondary program or if they would like to resume the primary program. If the user wishes to remain on the secondary program, then Flashback sets a marker on the recorded data for the primary program, so the user may return to the moment in time when the commercial break ended. If the user does return to the primary program at the end of the commercial break, Flashback records the primary program, and then the user is able to resume action on television the program from end of commercial. In addition to the recording feature, Flashback remains active until the user specifies another television signal or disables Flashback on the original primary program.

In order to accomplish Flashback, we developed a device that is a simple additional connection to the user's existing cable box, an over-the-air television programming antenna, or a satellite television receiver. Our device is able to record two television programs. The first being the channel of which Flashback is enabled and the second being the channel of which the user is watching while the primary program is recorded and analyzed. The secondary signal could be a single channel or it could be the user flipping through a number of channels. To analyze the television signal and detect commercials we used a Gumstix Overo® TidalSTORM computer-on-module and a cape board loaded with high-level software. To control the Flashback device, our group uses an infrared remote control that contains a user friendly 7-segment display to confirm user commands.

Our goal in the design of Flashback was to enhance the viewing experience while creating a device that is portable, low-powered, easy-to-use, real-time, and most important of all, accurate. We also plan to incorporate the elimination of commercials within the recording of these programs. This feature will provide users with uninterrupted, recorded playback removing the need for users to fast forward through commercials. This aspect of recording will also save space for recorded programs due to the elimination of the commercial blocks that every television program contains. Future revisions of the project will target homes, families, or sports bars when multiple games are being played in an allotted time.

## 2.0 Project Description

This section will outline the motivation and goals of the intended project, while describing the general functionality of the device we plan to build and execute. It will also discuss the objectives desired through the pursuit of Flashback.

### 2.1 Project Motivation and Goals

Flashback is a device that increases the viewing pleasure of anybody sharing a single television with different interests in television programming. Although there are already devices that detect commercials and allow for instant transitions between channels, they aren't as accurate as Flashback nor do they function with live stream video. Flashback's main goal is to detect the transition between live television and commercials so primary or secondary channels can be switched instantaneously while maintaining a high accuracy to allow viewers to pick up where they left off before the commercial break.

The idea for this device was conceived through the viewing of a sporting event on television while other individuals were present that were not interested in watching the sporting event. Since sporting events have erratic commercial breaks, the manual switching from the channel hosting the sporting event to any other channel can potentially lead to the missing of a big play or a certain amount of the time of the game, which in turn, leads to frustration. This frustration can fall true for any genre of television. Digital video recorders actually record every channel a viewer watches on its main memory; this action allows users to rewind and fast forward recorded live television, however, the catch is that once they switch channels, that recording is lost unless they set that channel to record. Using this current technology, there would be no way for a user to watch a part of the program that they missed unless that channel is set to record. With this device, we remove the chance that users could miss a part of their program since the device knows when to switch back to the channel they set as their primary.

With the new rise of smart technology, almost everything is becoming smart nowadays such as smart cars, security, and phones; why not introduce smart to your DVR? Flashback embodies the idea of 'smart' through self-detection of commercial breaks, and since the device can detect these commercials why not eliminate them from recordings? Although DVR's record programs effectively, the recording algorithm of a DVR does not discriminate between actual scheduled programming and commercials. Without this distinction, users have to fast forward through commercials that could have been eliminated. In many cases, users will forget that they are watching a recording and will spend time watching commercials. We created a device that will allow the user to take back their living room from advertisements that interrupt a user's free time to enjoy entertainment.

## 2.2 Objectives

Flashback's design utilizes many low power integrated circuits to provide the lowest possible power supply without sacrificing device functionality. Our device uses American standard wall outlet AC power translated to DC power using an external converter. Input DC voltage for safe operation on Flashback device is 5V running at 2.5 A. The device runs on an embedded operating system with a CPU dedicated to storing the current channel being watched on the main memory while running the appropriate algorithms for determining if the channel has just reached a commercial break. All the processes necessary in achieving these tasks to be threaded especially the frame by frame operations. Multi-threading is also necessary for detecting user commands that require other tasks to be run during commercial detection which will remove any lagging associated with process switching.

Flashback implements an algorithm that is at least 95 percent accurate in detecting commercials on both channels. When the algorithm detects a commercial from the on-screen display, the GUI Overlay of the software notifies the user that a channel's commercial break has ended and will either automatically change channels or require users to give the device the "okay" to switch. The algorithms are streamlined enough to prevent any lag or processor lock so that users don't experience any inconvenience from using the device.

The on-screen display of the device is similar to what users are familiar with, while limiting the input needed from the user. The display is adaptable for different television sizes. When the user inputs the commands they want executed, the options easy to understand and the different classes of options are under the correct menu so users can find them. The main goal for on-screen display was to provide effortless use of Flashback because the time spent watching television should be enjoyable; users won't want to use a device that's too complicated.

The device is able to record a user's preferred channel while maintaining responsiveness to the user. This functionality of not recording commercials provides users with a richer viewing experience since it eliminates the need to fast forward through commercials. The recording portion of the algorithm receives a signal from the commercial detection portion of the software as to whether a commercial break has begun or ended. The recording portion pauses when a commercial break is detected and resumes when a commercial break has ended.

Overall, the device's main objective was to provide the user with the best possible viewing experience. Commercials and advertisements are a hassle for

users to watch. Our group provided the user with a way to avoid these advertisements during live and recorded programming.

## 2.3 Project Requirements and Specifications

This section will discuss the project requirements, along with the hardware and software specifications of Flashback. It will also numerically define "real-time" and "live" programming for Flashback

### 2.3.1 Project Requirements

Flashback is a device that's similar to Digital Video Recorder with some extra functions to allow users to skip commercials. The Flashback device itself is low powered, responsive to user input, efficient, and easy to use. The device needs dual-television tuners to allow the software access to two channels. Without the dual tuners, the algorithm that pivots between channels wouldn't work. The processor in the device is powerful enough to handle parallel operations on matrices with at least 64 by 48 pixels in a quick manner. Each of these pixels will contain an RGB color code of 24 bits that will range from 0 to 16777216. The processor must be able to operate on a 64 by 48 frame, which includes pixel values that fall within this large range, and are able to maintain response in real-time.

Flashback contains an on-screen display that provides users with a familiar layout that contains functionality similarly to what one would see using a DVR. This interface may also request user input from a remote control, mouse, or keyboard. The interface requires minimal user input to function properly.

Every layout for the on-screen display contains font that's legible from the average distance that user's watch television from, which is about 10 to 15 feet away. The on-screen display efficiently streams frames from compressed MPEG-2 files. The MPEG-2 file format is a compression format, widely used by television programming providers to supply their viewers with high definition digital television. Without support for MPEG-2 files, Flashback would not be able to provide its user with expected or sufficient television programming.

Flashback supports the recording of channels and more importantly the recording of programs without commercials. The algorithm uses codecs to compress and encode these streaming videos into MPEG-2 files for storage onto the device's drive for playback. To support the removal of commercials from recordings, the processor is able to multi-thread, so the transition from the advertisement detection algorithm to the recording algorithm is quick and efficiently accomplished. Without the use of multi-threading, Flashback's main feature of quickly detecting and deleting commercials from live television would be extremely slow. Recording a user's program without commercials provides the user with an uninterrupted program, thus, enhancing their viewing experience.

## 2.3.2 Minimal Technical Hardware Specifications

Below our group has outlined our initial hardware requirements and expectations for Flashback

#### Processor

- Must be an ARM type

- Use ARMv6 Architecture or Higher

- DDR 2 Support

- Built in cache

- o L1 is a must

- L2 is optional

- Size of either will be based on based on processor

- Onboard Digital Signal Processor

- Onboard Graphics Processor

- Support at least two video capture channels

- Support output of High Definition Resolution

- Support scaling MPEG-2 Videos

- If it is Multi-Core

- Maximum 4 cores

- Each core must have a clock of at least 400 MHz

- Single Core

- Clock rate of at least 1.0 GHz

- Low Power

- Operating voltages of either 1.8 V or 3.3 V

- $\circ~$  I/Os, with exception of USB and DDR, operate on 1.8 V or 3.3 V

- At least two external memory interfaces for RAM and Storage Device

- Floating Point for increased dynamic range and precision

- LCD Controller

- At least two master/slave I<sup>2</sup>C buses

- SATA Controller

- At least 100 configurable pins for peripherals

#### RAM

- DDR 2

- 512 Mega Bytes

- Clock rate of 800 MHz

#### Storage

#### Hard Disk Drive

• At least 5400 RPM

- A Sizeable Cache

- Low power usage

- SATA 2 interface

- Internal/Laptop Form Factor

- 80 GB

#### Solid State Drive

- Low power usage

- SATA 2 interface

- Internal/Laptop Form Factor

- 32 GB

- Multi-Layer Cell

#### Connectivity

#### Infrared

• RC5 protocol

#### **Bluetooth Protocol**

- Version 2.1

- Version 3.0

- Version 4.0 (Low Energy)

- Must have open source stack

#### **Near Field Communication (NFC)**

- Must have open source stack

- Low profile antenna

- Support card emulation

#### WLAN

- Support for protocols:

- Wireless N

- o Wireless B/G

- 2.4 GHz Band

- 5 GHz Band

#### **Dual Television Tuners**

- Support ATSC

- Support NTSC

#### Analog to Digital and Digital to Analog Converters

#### **Internal Interfaces**

- SPI

- UART

• SATA 2.0

#### **External Interfaces**

- JTAG for hardware debugging

- GPIO Pins for future upgrades

- USB

- Prototype with Version 2.0

- Production will hopefully use 3.0

- o Multiple hubs

- LCD

- o 7 Segment Display

- Receiver LED

- o Channel Display upon input

- Clock for time display

- Potential Character display

#### External Video Interfaces

- High Definition Multimedia Interface (HDMI)

- Composite and Component Video

#### External Audio Interfaces

- Composite and Component Audio

- Optical Audio

## 3.0 Research Related to Project Definition

This section will discuss all relevant information, reference designs, costs, potential critical design options, and algorithms that may have any relation or contribution to the design and definition of Flashback

## 3.1 Digital Video Recorder

We will first discuss the digital video recorder, since it is the most similar device to the basis of Flashback, which we will expand and implement out intended design as a basis for or device. It appears to be an ideal reference design and algorithm basis.

### 3.1.1 Overview

A digital video recorder (DVR) records video provided by a digital television service provider onto a disk drive, USB, SD memory card or other mass storage devices. The incoming signal will come from an antenna, cable, or satellite device. Then it will pass through a tuner in which the user will be able to select the desired television program. Next, the signal will be sent to an MPEG-2

encoder to convert the stream to a format desired by DVR device. In the case of digital transmission from broadcast companies, no MPEG encoders will be necessary because satellite and cable companies will have converted the signal already. From the encoder the signal will be sent to two places: a storage device and a decoder, which will convert the stream and send to the television for user viewing. Flashback will need to alter the data flow slightly to enable our commercial detection algorithms, but our device will still be able to air television programs in a live feed (Strickland and Bickers).

A typical DVR device will usually operate on a highly modified Linux operating system. This operating system will reside on a local storage device, and the storage device will also have enough room to record television programs, provide a buffer for live broadcasts, and it might even have space to expand the program in the future. To record programs the device should account for approximately one gigabyte per hour of television in a basic setting and four gigabytes for a high-quality setting (Strickland and Bickers). Furthermore, DVRs require a buffer to handle the possible delays in receiving video stream information. The buffers are able to provide a consistent playback for the viewer and the user won't notice any delays that do happen.

## 3.1.2 Features

DVRs have many different features that enhance the viewing experience in comparison to only being able to watch a live feed on a single program. One of the many features that DVRs typically have is the ability to record different programs on different channels at the same time. To enable the device to perform these tasks, the DVR will have multiple television tuners. Another simple but impressive feature about digital video recorders is their ability to pause live television. DVRs actually don't "pause" the incoming signal until one is ready to view it. The device actually acts like a buffer and is constantly recording the television program. By pressing "pause," the user actually freeze-frames the current image being displayed and marks the location in memory of when the signal was "paused." When the user hits "play" the recorded program begins playing again. Furthermore, some DVR devices have the ability to record up to 300 total hours of television programs depending on the video quality (Strickland and Bickers).

### 3.1.3 Costs of DVR

DVRs usually have a monthly fee associated with their use. The reason for an ongoing payment system is because the devices will have to open up communications with a server at the broadcast company to download new program guides (Strickland and Bickers). The pricing of DVRs will depend heavily on the amount of applications desired. They could range from \$50 to approximately a couple thousand dollars.

## 3.2 FPGA vs. DSP

This section will discuss the pros and cons of choosing between a FPGA and a DSP for digital signal processing hardware and all its components. The applications we want to include in Flashback will play a huge part in this design decision

### 3.2.1 Overview

There are two front runners for digital signal processing hardware, Digital Signal Processors (DSPs) and Field Programmable Gate Arrays (FPGAs).

Digital Signal Processors are essentially a specialized microcontroller whose characteristics are optimized for high-speed processing applications. DSPs take real-world signals that have been digitized and then mathematically manipulate them for specific applications. DSPs offer a combination of arithmetic operators, memory handling, instruction set, parallelism, and data addressing are the key difference between DSPs and other kind of processors. Digital signal processors offer many benefits including the ability to process data in real-time (Skolnick and Levine).

A Field Programmable Gate Array is a programmable semiconductor device that contain a matrix of Configurable Logic Blocks (CLBs) connected with programmable interconnects. These devices are not built for a particular design. They can, in fact, be programmed to a desired application or functional requirement. If the desired application or functional requirement changes, the FPGA may be reprogrammed to implement a new design. These designs can be done very late in the design cycle even after the device has been deployed to the field. FPGAs at the minimum have CLBs, interconnects, select inputs and outputs, memory, and clock management blocks ("FPGA vs. ASIC").

The purpose of Flashback is to process video stream information in real-time while interacting with the user. To accomplish this, our device must be able to complete analysis of a current sample before the next sample arrives (Skolnick and Levine). Therefore, DSP or FPGA selection will use performance as its number one priority with power consumption, and cost as secondary priorities. All of these aspects weigh heavily on our groups decision to utilize one device over the other.

#### 3.2.2 Performance

Both Digital Signal Processors (DSPs) and Field Programmable Gate Arrays (FPGAs) are able to be reprogrammed frequently and at possibly crucial times in

the design process. However, if the design specifications change an FPGA is able to adjust to the new modifications faster than the DSP. With a DSP, there may be time spent wasted on obtaining a new component if the design specifications change (Wain).

Furthermore, FPGAs are parallel in nature unlike processors. This allows FPGAs to execute commands without competing for the same resources. In order for FPGAs to truly work in parallel the hardware contains dedicated sections of the chip and can execute without any influence on the other logic blocks. They are able to control inputs and outputs at the hardware level to provide a faster response time ("Introduction to FPGA Technology: Top 5 Benefits"). FPGA's flexible ability makes the hardware more desirable for prototyping situations.

FPGAs are typically better with tasks that involve fixed point data, and they are not that good with high precision floating-point arithmetic (Wain). DSPs are able to handle more complex algorithms and varying data sizes much better than FPGA. Since image processing focuses on "regions of interest" in an object, those regions could be varying sizes and therefore the processing will be more complex ("Choosing FPGA or DSP for Your Application").

Before an FPGA is programmed, it knows nothing about how to communicate with other devices which allows increased flexibility but also increased complexity in programming the device. Since DSPs are geared more toward specific applications, the processor is able to recognize the peripherals and how they communicate with other devices. In addition, the software development can be done in a higher level programming language, such as C (Wain). This programming environment will make it easier to incorporate more complex algorithms for the nature of our group's project. Both DSP and FPGA offer libraries for basic signal processing, such as Finite Impulse Response filters and Fast Fourier Transforms ("Choosing FPGA or DSP for Your Application").

### 3.2.3 Power Consumption

FPGA's highly flexible architecture comes with a disadvantage of more energy consumption. They have increased energy consumption because FPGAs have more gates, more silicon area, and more routing resources. DSPs are tailored for efficient implementation, and therefore, they can have lower chip-level energy consumption. Berkeley Design Technology, Inc. (BDTi) performed an analysis of power consumption on demanding DSP applications. Their results showed that FPGAs consume approximately 10 Watts, while high-end DSPs consume roughly 2-3 watts. These numbers work in favor of overall chip-level consumption but since FPGAs can support 10 to 100 times more channels the energy consumption per channel is significantly lower than that of DSPs. Our group looked at the chip-level energy consumption because Flashback's algorithms will not need to utilize more channels than the many offered through FPGA ("FPGAs vs. DSPs: A Look at the Unanswered Questions").

|     | Device Family                                                                                                                             | Device<br>Cost<br>(Dollars) | Max 32-<br>bit MMAC | Cents /<br>MMAC |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------|-----------------|

|     | C5000 Fixed Point DSPs<br>C2000 Controllers                                                                                               | <10                         | 25 - 300            | 1.8 - 46        |

|     | DaVinci Digital Media<br>Processors<br>C6000 Fixed Point DSPs<br>C6000 Floating Point DSPs<br>C5000 Fixed Point DSPs<br>C2000 Controllers | 10 - 30                     | 50 - 1200           | 1.6 - 35        |

| DSP | DaVinci Digital Media<br>Processors<br>C6000 Fixed Point DSPs<br>C6000 Floating Point DSPs<br>C5000 Fixed Point DSPs                      | 30 - 100                    | 50 - 1440           | 3 - 44          |

|     | DaVinci Digital Media<br>Processors<br>C6000 Fixed Point DSPs<br>C6000 Floating Point DSPs<br>C5000 Fixed Point DSPs                      | 100 - 300                   | 266 - 2000          | 5.8 - 48        |

|     | C6000 Fixed Point DSPs                                                                                                                    | 300 - 330                   | 2000 - 2400         | 13.4 - 14.4     |

|     | Cyclone II<br>Cyclone III                                                                                                                 | 10 - 30                     | 270 - 660           | 1.4 - 7         |

|     | Cyclone II<br>Cyclone III                                                                                                                 | 30 - 100                    | 380 - 1900          | 2.8 - 20        |

| PGA | Cyclone II<br>Cyclone III<br>Stratix III                                                                                                  | 100 - 300                   | 1000 - 4500         | 2.9 - 34        |

| FP( | Cyclone II<br>Cyclone III<br>Stratix II                                                                                                   | 300 - 1000                  | 1000 - 8300         | 4.2 - 47        |

|     | Stratix II<br>Stratix III                                                                                                                 | 1000 - 3000                 | 3000 - 11000        | 20 - 100        |

|     | Stratix II<br>Stratix III                                                                                                                 | 3000 - 10000                | 4000 - 11000        | 20 - 130        |

**Table 3 – 1:** Information provided from Afra and Kapadiya's article "Making design choices between DSP and FPGA"

## 3.3 Digital Signal Processor

Our group decided that we will use a digital signal processor over an FPGA based upon the requirements of Flashback, the groups skill set, and desire for

experience with DSP hardware. Due to the real-time nature of Flashback, our DSP selection will use performance as its number one priority. In analyzing the performance of a DSP we will look at the arithmetic format, speed, memory, peripherals, and power.

### 3.3.1 Arithmetic Format and Data Width

A key characteristic in DSP selection is whether to use fixed-point or floatingpoint arithmetic. Fixed-point arithmetic essentially means that numbers are represented as integers or fractions within a fixed range. Floating-point arithmetic means that values are represented by a mantissa (decimal part of a logarithm) and an exponent, i.e. mantissa x 2 ^ exponent ("Choosing a DSP Processor"). To determine whether the systems need for either floating-point or fixed-point the designer must first look at the following characteristics: data width, dynamic range, ease of implementation, and cost.

Floating-point devices typically have a larger data width, precision, and ease of implementation than fixed-point. The data width will have an impact on the size of the chip, number of pins, and the size of external memory. With floating-point arithmetic the designer will be able to implement greater precision. When the DSP performs a calculation, that number may be rounded to the nearest value based upon the format. Due to the larger data width, the floating-point device will not need to round or truncate the value as much and this will prevent unwanted quantization noise derived from representing analog signals in a digital format.

Floating point devices are easier to program because the programmer will not have to worry about number scaling prior to arithmetic operations to avoid rounding and truncating errors. A wider dynamic range means that the circuit will be more complex and therefore will require a larger silicon chip. The wider dynamic range of floating-point DSPs will typically cause them to be more expensive and have a higher amount of power consumption ("Choosing a DSP Processor").

Fixed point devices have speed, efficiency, and cost on their side. Fixed-point devices, with a smaller data width, do not require as large of a chip or pin count and this will reduce the cost. However, these devices are more particular when they are programmed. The designer must be aware of data flow during all stages of processing since at some points they may need to carefully scale the signals to ensure numeric precision within the limited dynamic range. Typical design practice is to choose a device with the smallest word size that can still support the fundamental application. The clocks of fixed-point systems can typically support greater speeds than floating-point. In many high-volume, embedded applications a fixed-pint device is chosen for the lower cost and power consumption ("Choosing a DSP Processor"). Furthermore, a decoder in the format of MPEG-2, MPEG-4, or JPEG-2000 utilizes decoding algorithms designed to be performed in fixed-point (Angoletta).

If needed, it is possible to perform floating-point arithmetic on a fixed-point processor through software routines that emulate the behavior of a floating-point device. The software routines may consume an extreme amount of clock cycles so in practice it is advised to proceed with caution. Fixed-point DSPs can also employ block floating-point, where a group of numbers with mantissas but a similar exponent are processed as a block of data. Block floating-point is handled in software with the assistance of hardware features ("Choosing a DSP Processor").

Data width will have a major impact on the cost of DSP chosen. The width will influence the size, number of package pins, and the size of external memory devices connected to the DSP. A good design practice is to see what minimum width each of the peripherals will require, as well as, the amount of bits required to represent the signal without losing precision. It is important to note that many, but not all, DSP processors will use an instruction word size equal to their data word size ("Choosing a DSP Processor").

### 3.3.2 Speed and Memory

There are a number of ways to test a processors speed but first consider the instruction cycle time. The instruction cycle time is the amount of time required to execute the slowest instruction on the processor. If the reciprocal of the instruction cycle time is taken, divided by one million and multiplied by the number of instructions executed per cycle then we will arrive at the processor's instruction execution rate in millions of instructions per second, MIPS. When comparing DSPs MIPS rate, check the DSPs hardware because DSP chips may have phase-locked loops (PLLs) that allow the use of a lower-frequency external clock to generate the needed high-frequency clock on-chip ("Choosing a DSP Processor").

Fast execution of MAC operations requires fetching an instruction word and two data words from memory every clock cycle. To permit this, the DSP will need to be able to access memory multiple times for each instruction cycle, separate instruction and data memories, and instruction caches ("Choosing a DSP Processor").

Digital signal processors for real-time processing will need to access data and access it very fast. DSPs need to transfer data to and from memory or other peripherals at a fast rate. Some of the items that determine a fast data access are the type of high-bandwidth memory architectures, specialized addressing modes, and direct memory access. Typically DSPs adopt the Harvard or Super-Harvard Architecture in which there are separate memories for data and program instructions and two separate buses to connect each of them to the DSP core. To improve the Harvard architecture it is recommended to add a bank of fast memory for the program instructions and data cache (Angoletta).

Instruction pipelining has become extremely important component to DSP performance. Pipelining divides the execution of instructions into multiple stages and executes the instructions in parallel. The instructions can essentially be broken up into 3 stages: instruction fetch, decode, and execute. Fetch is when a DSP calculates the address of the next instruction to execute and retrieves the op-code. Decode will route the op-code from fetch and send it to the proper functional unit in which it will execute the instruction and write he results back to registers (Angoletta).

One of the most often cited features of a Digital Signal Processor is its ability to perform one or more multiply-accumulate operations (MACs) in a single instruction cycle. The MAC operation is a useful algorithm that computes a vector dot product, such as a digital filter, correlation, and/or a Fourier Transform. DSPs now are able to incorporate multiple MAC units operating in parallel fashion to achieve more computations per instruction cycle. With multiple MACs, the DSP may run into the issue of overflow. To counteract overflow possibility the DSP will implement "guard" bits to protect the data integrity ("Choosing a DSP Processor").

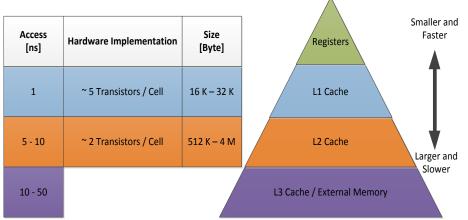

The typical DSP hierarchical memory architecture and typical number of access clock cycles, hardware implementation, and size of different memory types can be located in the Figure below provided by Texas Instruments.

Figure 3 – 1: DSP Memory Architecture

Preferably our DSP will have a large amount of L1 and L2 caches to decrease the amount of time needed to retrieve data to increase our devices ability to process in real-time. Our device will also utilize DDR SDRAM to store operating system resources, the GUI, Flashback algorithm and the recorded programs specified by Flashback users.

### 3.3.3 Peripherals

In order for our DSP to communicate with other components within Flashback we must have a wide variety of peripherals. We will be looking at devices that contain at least 10/100 Mbps Ethernet, USB 2.0, audio, and video port.

The DSP requires a reasonable amount of flexibility in I/O pins with programmable interrupts and event generation modes to be multiplexed with other peripherals. These I/O pins will be used for additional features to Flashback device.

### 3.3.3.1 Universal Serial Bus

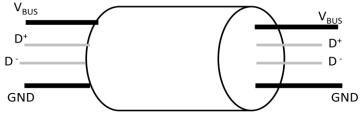

Universal Serial Bus (USB) is an external bus standard that supports data transfer and is capable of supporting up to 127 peripheral devices. Inside a USB cable there are 4 wires, one for 5 Volts, ground, and two for data. An example of a USB cable is shown below in Figure 3 - 2.

USB cables are able to be run over 5 meters without signal loss (Brain). A newer standard of USB and one that our signal processors will most likely support is, USB 2.0. USB 2.0 is known as the hi-speed USB and is capable of supporting a transfer rate of up to 480 Mbps ("USB").

USB connectors allow the user to attach mice, printers, external hard drives, and other accessories to your device quickly and easily. The operating system for our processor package must and most likely will support at least USB 2.0. Upon performing enumeration the host device will find out from each peripheral what type of data transfer it wants to perform. Some different types of data transfer are an interrupt, bulk, and isochronous. Isochronous refers to a streaming device such as speakers. Isochronous data transfer caters to our project as many of the items we will do are in real-time streaming of information (Brain).

A USB divides the available bandwidth into frames and the host can control the frames. Frames will contain 1,500 bytes and a new frame will be received every millisecond (Brain).

### 3.3.3.2 Ethernet

Ethernet is a communications protocol embedded in software and hardware devices to establish a local area network (LAN) connection (Kanye and Wynn). Ethernet cables are very efficient in sending data over long lines of communication; they can reach in the tens of kilometers in distance (Pidgeon). An Ethernet cable is shown below in Figure 3 - 3.

Ethernet follows some simple rules for its operation. Ethernet devices must be able to attach to a shared medium (segment) that will provide a signal flow path which will have devices connected to the segment (nodes). The nodes will communicate in short messages called frames (Pidgeon).

The carrier-sense multiple access with collision detection (CSMA/CD) describes how an Ethernet cable will control the communication among all the nodes. Carrier sense essentially means that before a second transmission can go through the cable, the first data set must be completed. There is also multiple accesses with carrier sense. If for some reason, data is transmitted at the same time, a "collision" will occur. Sometimes an ethernet segment will be called a collision domain because on this domain two different stations cannot transmit at the same time without colliding into one another. If a collision is detected then the transmission will halt and wait a certain amount of time until it decides to attempt to transmit again (Pidgeon).

### 3.3.3.3 Inter-Integrated Circuit Bus

Inter-integrated circuit bus is more commonly known as I<sup>2</sup>C bus. This bus is a two-wire serial bus and there is no need for chip select or arbitration logic which makes this bus cheap and simple to implement in hardware. The two signals are serial data (SDA) and serial clock (SCL). I<sup>2</sup>C bus provides good support for communication with different, slow, on-board peripheral devices. These devices are accessed in intervals and have a low-bandwidth, short distance protocol. The typical I<sup>2</sup>C operates at speeds of up to 400 Kbps and can go up to the megahertz range. The I<sup>2</sup>C protocol has a built-in addressing scheme. I<sup>2</sup>C is used for EEPROMs, thermal sensors, real-time clocks and most importantly as a control interface to signal processing devices with separate, application specific data interfaces. I<sup>2</sup>C multimedia applications extend from RF tuners, video decoders and encoders, and audio processors (Kalinsky D. and Kalinsky R.). For Flashback, we could use I<sup>2</sup>C bus to send our data from the video tuners to the video decoders, then to the audio processor after passing through our system-on-chip (SoC).

One of I<sup>2</sup>C's weaknesses is its ability to send signals over long distances. I<sup>2</sup>C will work great on a single board and even if it is sent across multiple boards but it cannot work well past a few boards.

### 3.3.3.4 Multichannel Audio Serial Port

A multichannel audio serial port (McASP) functions as a general-purpose audio serial port that is optimized for the needs of multichannel audio applications. A McASP is useful for time-division multiplexed (TDM) stream, Inter-Integrated Sound (I2S) protocols, and inter – component digital audio interface transmission (DIT). The McASP module contains sixteen serializers which can be enabled to

either transmit or receive. While in the transmit configuration the McASP can send signals to multi-channel digital to analog converters which will then be sent to amplifiers for audio output. The McASP can also be enabled for receive mode. While in this mode the McASP will act as a digital encoder or processor before it is able to send the signals to amplifiers ("TMS320C6000 DSP Multichannel Audio Serial Port (McASP)").

## 3.3.4 Video

The DSP must contain at least two video capture channels. Both of these signals will pass through the DSP and be sent to the storage device simultaneously. The primary and secondary signals will need to pass through the DSP so that the System on Chip (SoC) is able to control which MPEG transport stream to decode and display on the television screen. If Flashback is enabled and the user has wandered to a secondary program while the primary program is analyzed then the secondary program will be displayed on the television. If Flashback is disabled then our device can merely display whatever television program the user wishes to view. The two video capture channels need to be at least standard – definition with the capability of high-definition. After our group successfully performs the Flashback concept with standard definition, we will progress to working with high-definition. Due to this sequence, we need a DSP package that is capable of high-definition video capture channels.

## 3.3.5 Power

Digital Signal Processors are now being offered at reduced voltages such as 3.3, 2.5, or 1.8 V and all of these can operate at the same clock rate as the 5-V version. By reducing the operating voltage, our Flashback device will be able to minimize power and heat dissipation ("Choosing a DSP Processor").

DSPs have also begun to offer feature modes to reduce power consumption and increase the user's ability to manage power. One of those features is a "sleep" or "idle" mode. In this feature the user will be able to turn off the processor's clock to all but certain sections of the processor. To bring the processor back from "sleep" mode an interrupt can awaken the areas needed. In addition, DSPs could come with programmable clock dividers to allow the processor's clock frequency to be varied under software control in order to use the minimum clock speed required for a particular task. Lastly, some devices are able to disable peripherals that are not in use.

To optimize the efficiency of the Flashback device, it is preferred to have as many similar low-voltage rails as possible. This will first and foremost reduce the amount of power consumed by the DSP. The second purpose of this is to reduce the amount of heat within the system. Most components are rated for 90 degree Celsius or higher the high temperatures will degrade components quicker than at ambient temperature. Furthermore, if we have many similar voltage rails then we can reduce the amount of components needed to step-down and clean up power supply signals.

## 3.4 SATA Controller

Serial Advanced Technology Attachment (Serial ATA or SATA) is an attachment that enables mass storage devices to communicate with a motherboard over a high-speed serial connection. These mass storage drives could be solid state drives, hard disk drives, optical drives, etc. The SATA controller has different modes for to determine how the storage device will communicate. The controller can be set to operate in one of the following modes: integrated development environment (IDE), advanced host controller interface (AHCI), and redundant array of independent disks (RAID) ("About SATA Hard Drives and Controller Modes")

IDE mode will set the storage device to run as an IDE or a Parallel ATA drive. While in IDE mode, the drive will perform slower than the others, but it will provide better compatibility when trying to communicate with older hardware ("About SATA Hard Drives and Controller Modes").

AHCI will enable the advanced features on SATA drives, such as hot swapping and Native Command Queuing (NCQ). Hot swap is the replacement of a hard drive, CD-ROM drive, power supply, or other device with a similar device, while the computer system using it remains in operation. This essentially will give the appearance to the input / output controller that the device is still attached even though it is actually being removed and replaced ("Hot Swap"). NCQ is a technology that has been designed to improve the performance and reliability as the transactional workload increases on SATA hard disk drives. If there are multiple commands sent to the SATA drive, NCQ will group the commands in the order of processing efficiency. This will minimize the mechanical workload and increase the performance on the drive ("Native Command Queuing"). The use of AHCI will increase speed relative to IDE.

RAID enables the device to store the same data in different places on multiple storage devices. This will allow input/output operations to overlap in a balanced way and will therefore improve performance. Whenever a system uses multiple drives, the system will have an increased mean time between failures (MTBF) so storing data redundantly will increase the tolerance to failure ("RAID (redundant Array of Independent Disks)"). While in RAID mode, the SATA controller will also enable AHCI ("About SATA Hard Drives and Controller Modes")

## 3.5 Digital Image Processing

The interest in digital image processing stems from two main applications, improvement of pictorial information for human interpretation and processing image for autonomous machine. People want to understand what is really going on in a picture ("Fundamentals of Digital Image Processing"). For instance, fire control systems from defense contractors use image processing to determine if people or vehicles are moving in a threatening pattern or if they are carrying a threat. Flashback will focus on the second application. Our device will analyze the incoming video stream provided by a cable company and will search for commercials in a real-time fashion.

Images are digitized in spatial coordinates and in brightness for the image to be considered a digital image. A digital image is a 2-D array of light intensity, and the spatial coordinates of the pixel (an element in the digital array). The first step in image processing is to acquire the digital image. Next, the image will be preprocessed to improve the image to increase the efficiency of image processing algorithms. The image must now be segmented into parts or objects. After segmentation, the image will be converted to a form suitable for computer processing. Then the system can extract features that result in information of interest or features that are basic for differentiating objects from another. Based upon the information, the system will assign a label to the objects. Lastly, the image will be interpreted ("Fundamentals of Digital Image Processing").

## 3.6 Object Isolation

In comparison with a single still image, video sequences can provide more information about how objects and scenarios change over time. To detect an object's behavior, the system must first perform an isolation algorithm. The isolation algorithm will start with the current frame and a reference frame. Then the wavelet transform will be applied to each frame to create a wavelet pyramid and the filter banks. The number of levels of decomposition will be chosen depending on the size of the frame and content of the video. The background differences play a large factor in the algorithms ability to track an object.

Therefore, the algorithm will take the current image and the reference image and subtract to find the differences in the image. By doing this, all of the pixels in the frame that are consistent frame to frame will be set to zero and the differences will have a value other than zero. The differences in the images could be a result of either noise, or that an object has moved from frame to frame. To make sure that noise isn't a factor a threshold must be established for the difference of pixel values. After isolating the object(s), the system must only perform complications on a smaller range of pixel values to track the object (Wang and Doherty).

In terms of our groups project object isolation could be performed to key in on the broadcast logo. As you may have noticed, on television programs the broadcast logo will be displayed in, most likely, the bottom right quadrant of the video stream. The logo will "disappear" when the broadcast station transitions to a commercial break. Our system could employ the object isolation algorithm and detect when that object is no longer there. This would mean, with high accuracy, that the television program is on a commercial break. Then as the logo reappears, our detection algorithms will trigger our system-on-chip to prompt the user and let the user know that the commercial break has ended.

### 3.7 Real-Time Processing

Flashback will need to operate in real-time. What this means is that our processor must perform calculations on the first set of data before the second set of data arrives. Digital signals are represented with sets of samples of an analog signal at discrete moments in time. Therefore the Digital Signal Processors ability to process signals in real-time depends on the sampling rate. The sampling frequency must be at least twice the frequency of the highest frequency component of interest in the signal. For example, if we only look at a 10 kHz input signal then our sampling frequency must be at least 20 kHz. To process this data in real-time the signal processor must be able to compute in the following time budget:

time budget =

$$\frac{1}{20 \text{ kHz}} = 50 \text{ }\mu\text{s}$$

To enhance Flashback devices ability to process in real-time we will utilize the following guidelines. First, work in parallel as much as possible to increase computation speed. Working in parallel avoids significant waiting times for executing operations in comparison to working in series. Second, specify and fully document all interfaces. Third, always include validity checks on DSP inputs. Fourth, add spare parameters with different formats to maximize flexibility, as well as, allowing the addition of debugging features or implementation of small updates. Finally, validate code implemented on device.

### 3.8 MPEG

Moving Pictures Experts Group (MPEG) is a standard for "the generic coding of moving pictures and associated audio information." It describes a combination of video compression and audio data compression methods which permit storage and transmission of movies using available storage media and transmission bandwidth. MPEG is widely used as the format of digital television that are broadcasted over the air, cable, and satellite systems ("MPEG-2 Video Encoding (H.262)").

MPEG video encoding (H.262) employs an intra-frame Discrete Cosine Transform (DCT) coding and motion-compensated inter-frame prediction. A DCT expresses a finite sequence of data in terms of a sum of cosine functions oscillating at different frequencies. The DCT breaks up each frame into 8 pixels by 8 lines of each component of the picture. Then a DCT is performed on that to produce blocks of DCT coefficients. The magnitude of these coefficients indicates the contribution of a particular combination of horizontal and vertical spatial frequencies to the original picture block. This is very important lossy compression of audio and images.

Next, MPEG employs a motion-compensated interframe prediction. This prediction looks at the current frame and compares it with a reference frame (previous frame) to determine how many picture elements have changed. After finding the redundancies, the MPEG encoder will eliminate the elements from the picture. Typically the redundancy calculations are done prior to DCT in order to avoid duplicate / excessive calculations ("MPEG-2 Video Encoding (H.262)").

MPEG encoding can be done purely in software or by using an MPEG capture card or a video editing card with in-built MPEG encoding capabilities, or a dedicated hardware encoder like the ones typically built into video recorders. The transport stream contains compressed images, sequence headers, group-of-picture headers, and other data needed to decode the transport stream. The sequence header contains information concerning the frame size and the frame rate needed before the system can decode the stream ("MPEG-2 Video Encoding (H.262)").

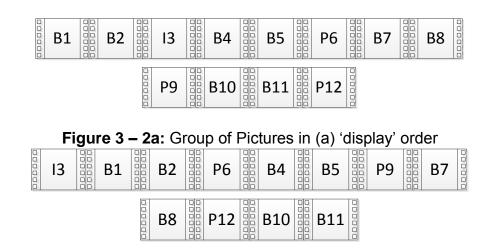

MPEG-2 defines 3 different types of pictures: Intra pictures (I-frames), Predictive pictures (P-frames), and Bidirectional-predictive pictures (B-frames). I-frames are coded without any reference to other pictures. P-frames use motion compensation as described above and could actually be used as a reference frame for further predictions. B-frames can use previous and next I-frame or P-frame for motion compensation. In addition, B-frames will offer the highest degree of compression.

Before a future image is able to be used as a reference frame the encoder must reorder the pictures from natural 'display' order to 'bit stream' order so that the B-picture is transmitted after the previous and next pictures it references. B-frame technique could come in handy with Flashback algorithms and processing in real-time. Our system desires to do a comparison of frames because when broadcast stations transition to commercials they insert a frame where all pixel RGB values are black. Since the entire frame is black all elements in the DCT blocks will be changed and transmitted. If our system can look ahead one frame, this will ease our system's ability to process in real – time ("MPEG-2 Video Encoding (H.262)").

Figure 3 – 2b: Group of Pictures in 'bit stream' order

In the video editing and processing systems, multiplexing refers to the process of interleaving audio and video into one coherent MPEG transport stream. The individual audio and video streams may have a variable bit rate. Recording the digital signals provided by the MPEG stream is straightforward since no additional hardware will be needed to quantize and compress the signal ("MPEG-2 Video Encoding (H.262)").

## 3.8.1 H.264

Transform coding for H.264, also known as MPEG – 4, is a more efficient image compression technique than MPEG – 2 H.262. H.264 first transforms the image into blocks of four elements by four elements as opposed to the eight by eight (DCT) in MPEG – 2. Next, MPEG – 2 was a floating-point arithmetic compression and H.264 is an integer to integer transform. The integer transform allows for exact reconstruction and completely eliminates decoder drift caused by a mismatch from encoder/decoder. After getting the elements in four by four blocks, there are nine different ways that H.264 can perform spatial prediction. The inverse transform will now only require 16 bits of integer precision. Furthermore, H.264 can have multiple reference frames of up to 15 frames and can also refer to the future frame by the means fo displayed the frames in 'bit stream' order (Igarta).

## 3.9 Video Tuners

Flashback provides the ability to record and display one video channel while also record and analyze a second channel. For this to be possible, Flashback will require dual video tuners. Video tuners tune into a particular television signal as specified by the user. The uses of dual tuners allow the capability of recording a live program while watching another live program simultaneously. There are many different types of video tuner ICs. Some of the tuners are geared toward digital only, analog only, or some are a hybrid of digital and analog signals.

Analog tuners can support three different types of analog television systems; National Television System Committee (NTSC), Phase Alternating Line (PAL), and Sequentiel Couleur avec Mémoire, which translates to Sequential Color with Memory (SECAM). NTSC is an analog television system that is used in most North America, parts of South America, and some Asian countries. There are 30 frames per second (fps) transmitted each second and these frames are composed of 525 individual scan lines. PAL is mostly used overseas in Middle Eastern, parts of South America, Europe, and Asia. PAL uses 25 fps and each frame is composed of 625 scan lines. SECAM uses frequency modulation to encode chrominance information. SECAM takes the post-production analog signal that was done in PAL and then transforms it to SECAM at the point of transmission ("PAL & NTSC & SECAM").

Digital tuners support Advanced Television Systems Committee (ATSC) / Quadrature Amplitude Modulation (QAM), Digital Video Broadcasting – Terrestrial and -Cable (DVB-T or DVB-C) or various newer standards (DVB-T2/C2), Integrated Services Digital Broadcasting – Terrestrial and -Cable (ISDB-T/C), and lastly Digital Terrestrial Multimedia Broadcast (DTMB). ATSC employs MPEG-2 data compression standard to perform a 50:1 reduction in data (Nist). QAM is both an analog and digital mod scheme; QAM changes the phase and amplitude of carrier waves using either a Amplitude-Shift Keying (ASK) or Amplitude Modulation (AM) ("Quadrature Amplitude Modulation (QAM)"). DVB-T2/T is the standard for transmission of digital television signals from aerial antenna to aerial antenna ("What Is DVB-T?"). DVB-C2/C is the digital broadcast standard that uses cable as the transmission medium. ISDB is a Japanese and Brazilian version of DVB with improvements in mobile reception ("Comparison of 3 DTTB Systems"). Lastly, DTMB is the Chinese version of DVB-T utilizing multiple carrier signals to transmit television content ("DTMB Technology").

Hybrid tuners are able to capture both analog and digital television transmissions. Tuners can be selected for low power consumption and operate on 3.3 V and 1.8 V power supplies with a typical dissipation of only 1 W. They also feature a low-noise amplifier (LNA) and high-Q tracking filter which will provide gain only around the channel desired (Schweber).

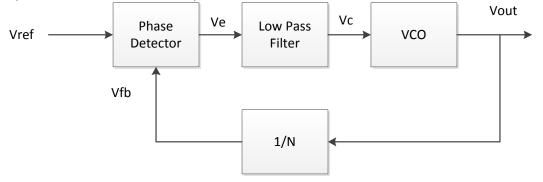

### 3.9.1 PLL Frequency Synthesizer

A frequency synthesizer is important in any transceiver. Frequency synthesizers must be able to look at different frequency bands and for different wireless standards. A Phase-Locked Loop (PLL) circuit will synchronize the output signal with an input reference signal. This means that the two signals will have the same frequency and will operate at a constant phase difference. PLLs in television applications perform the horizontal and vertical synchronization and

color reconstruction. PLL can be used as a frequency synthesizer by placing a loop divider in the feedback path as shown below:

Figure 3 – 3: Phase-Locked Loop Frequency Synthesizer

The output frequency for the diagram above is equal to where is the Voltage Controlled Oscillator (VCO) center frequency and is the VCO conversion gain. By adjusting N we can adjust the frequency of the PLL synthesizer. In order to allow the frequency synthesizer to account for a larger range of frequencies, the VCO's conversion gain must be very large. This might bring on some unwanted phase noise so the diagram should implement a switched tuning VCO instead. The switched VCO can tune over a wide range while still maintaining a low conversion gain (Palermo).

The use of a frequency synthesizer in the Flashback device could help hone in on certain video signals. By controlling the parameters of VCO and the feedback loop, we could adjust the PLL to accommodate for all frequencies within the overthe-air television spectrum.

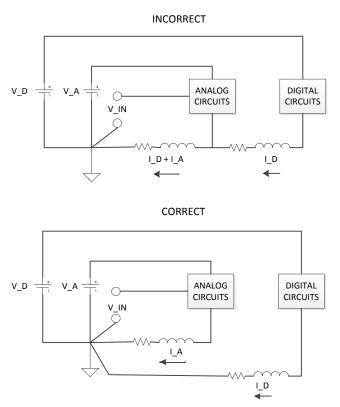

## 3.10 Grounding in Mixed Signal Systems

Maintaining a strong, wide dynamic range analog signal with minimal noise next to a digital environment will depend upon signal routing, decoupling, and grounding. Mixed-signal integrated circuits could have low or high digital currents. The different levels of digital current will need to have different grounding schemes to obtain optimum performance. It is desirable to separate sensitive analog components from the noisy digital components and hence the ground planes for analog and digital circuitry (Kester and Bryant).

A low impedance large area ground plane is critical to all analog circuits. This ground plane will act as a low impedance return path for decoupling high frequency currents (caused by fast digital logic) and it will also minimize EMI/RFI (electromagnetic interference / radio frequency interferance) emissions. All integrated circuit ground pins should be soldered directly to the ground plane to minimize inductance and resistance. Power supply pins will need to be

decoupled to the ground plane using low inductance capacitors (Kester and Bryant).

At least one entire layer of a PCB system should have a dedicated ground plane. If it is a double-sided board then one side should be ground and the other should be interconnects to the best of the designer's ability. Due to power, interconnects, and through holes, reserving one side of the board for ground will be near impossible. So best practice is to keep at least 75% of the board area on one side for ground plane. In addition, use at least 30% to 40% of PCB connector pins for ground. Lastly continue the ground plane on the backplane motherboard to power supply return (Kester and Bryant).

The analog to digital converters (ADCs) and digital to analog converters (DACs) and other mixed signal ICs with low digital current should be treated as an analog component and grounded and decoupled to the analog ground plane (Kester and Bryant).

After designating an analog and a digital ground plane, it is recommended to tie these planes together through a chunk of metal. This will allow the noisy digital currents to flow through the power supply and digital ground plane then back to the digital supply. The analog plane will not be affected (Kester and Bryant).

**Figure 3 – 4:** Proper Grounding Scheme

## 3.11 DDRx SDRAM

DDRx SDRAM stands for Double Data Rate Type x Synchronous Dynamic Random Access Memory; "x" is the number of revision to the DDR standard. With each new revision, DDR SDRAM is able to transmit at a higher theoretical transfer rate and the operating voltage lowers. SDRAM means that they use a clock signal to synchronize data. Dynamic RAM means that data is stored in an array of capacitors. DDR memory transfers two data sets for each clock cycle. Because DDR SDRAM sends two data sets per clock cycle, they are able to achieve double the performance of memories without this feature running at the same clock rate. DDR utilizes the rising and falling edges of clock cycles to transmit information (Torres).

Usually DDR, DDR2, and DDR3 operate at typical voltages of 2.5 V, 1.8 V, and 1.5 V respectively. Each revision, in addition to transfer rates, had a goal of reducing the total power consumption. If the memory is being overclocked then the operating voltage can raise approximately ten percent. The power consumption is a factor of speed, type of usage, and operating voltage (Torres).

DDR3 memories have the highest latency. Latency is the time the memory controller has to wait between requesting the data and sending the data. Even though DDR3 has the highest latency value, it is based on the number of clock cycles passed before receiving or sending data. This means that the latency value doesn't necessarily correlate to a longer wait time (Torres).

DDR memories also feature On-Die Termination (ODT). ODT is a resistive termination network located inside the memory chips to provide cleaner signals. ODT also increases the time frame for memory to read or write data which will allow better clocks to be achieved (Torres).

## 3.12 Thermistor vs. Analog Temperature Sensor

Thermistors and analog temperature sensors are the two most popular sensors for gauging temperature for electronics and their applications. The thermistor will require a resistive network to linearize the relationship between output voltage and temperature. While operating in room temperature range, the thermistor shows an almost linear slope and can have the "linear" range altered by the resistor network. However, once the system gets too hot or too cold, the thermistors will no longer have a linear relationship and the actual temperature value reading from the thermistor will not be accurate.

An analog temperature integrated circuit can output an exact linear response over the temperature range -50 degrees Celsius to 150 degrees Celsius. In the terms of supply current versus temperature, the greater the temperature the greater the supply current desired for the thermistor. The thermistor supply current range could be from single digit micro-Amps to a few hundred microAmps. As temperature varies for analog temperature integrated circuits the current could fluctuate by about four to five micro-Amps (Gosselin).

## 3.13 Debugging

A starting point of debugging the real-time design flow is to make sure that our group has an executable code; one that doesn't have compilation and linker errors. We will use this code to make sure the code behaves as expected. This could be something as simple as switching on and off an LED (Light Emitting Diode). To debug code, our DSP will use the following tools: simulation, emulation, and real-time debugging techniques. Simulation tools will provide full visibility into the DSPs internal registers, peripheral performance, and interrupts. Emulation tools will embed debug components into the target to all an information flow between Flashback device and host computer. Lastly, real-time debugging techniques allow a real-time data exchange between host and device without stopping the DSP (Angoletta).

## 3.14 ADC and DAC

An analog signal means that the signal is continuous over time. Real world signals such as sound, light, heat, etc. are all analog signals and these signals can be shown through electrical signals. A digital signal is the sampled version of the analog signal.