# P.H.A.T.C.A.T.

# PHASOR-HARMONIC ANALYSIS FOR TRANSFORMER CONDITION ASSESSMENT AND TELEMETRY

## Group Six Authors:

| Brett Ross  |

|-------------|

| Electrical  |

| Engineering |

Johnathon DeFour

Computer

Engineering

Daniel Hobbs

Electrical

Engineering

Edward Millet

Electrical

Engineering

Mentor:

Dr. Chung Yong Chan

## TABLE OF CONTENTS

| 1. | Executive Su           | ımmary                                                       | 1  |  |  |

|----|------------------------|--------------------------------------------------------------|----|--|--|

| 2. |                        | Project Description                                          |    |  |  |

|    |                        | ackground and motivation                                     |    |  |  |

|    |                        | bjectives                                                    |    |  |  |

|    |                        | Specifications                                               |    |  |  |

| 3. |                        | 1                                                            |    |  |  |

|    |                        | vant Technologies                                            |    |  |  |

|    | 3.1.1                  | Power System Transformers                                    |    |  |  |

|    | 3.1.2                  | Instrument Transformers                                      |    |  |  |

|    | 3.1.3                  | Protective Relaying Circuitry                                | 13 |  |  |

|    | 3.1.4                  | Overcurrent Protection                                       |    |  |  |

|    | 3.1.5                  | Current Differential Protection                              | 15 |  |  |

|    | 3.1.6                  | Harmonic Blocking                                            | 16 |  |  |

|    | 3.1.7                  | Overexcitation Protection                                    | 16 |  |  |

|    | 3.2 M                  | arket offerings                                              | 16 |  |  |

|    | 3.2.1                  | Schweitzer Engineering Laboratories: SEL-487E                |    |  |  |

|    | 3.2.2                  | Siemens: SIPROTEC 7UT87                                      |    |  |  |

|    | 3.2.3                  | PHATCAT Versus Market Offerings                              | 19 |  |  |

|    | 3.3 Co                 | ore components and Parts Selection                           |    |  |  |

|    | 3.3.1                  | Electronics Protection                                       |    |  |  |

|    | 3.3.2                  | Current Sensing                                              |    |  |  |

|    | 3.3.3                  | Low-Pass Filters                                             |    |  |  |

|    | 3.3.4                  | Programmable Gain Amplifier                                  |    |  |  |

|    | 3.3.5                  | Analog-to-Digital Conversion                                 |    |  |  |

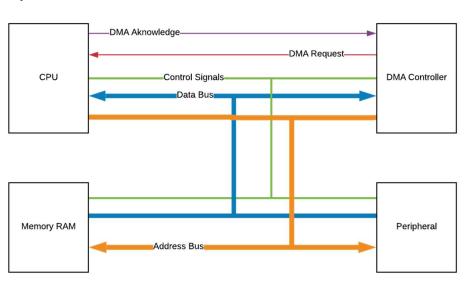

|    | 3.3.6                  | Direct Memory Access (DMA)                                   |    |  |  |

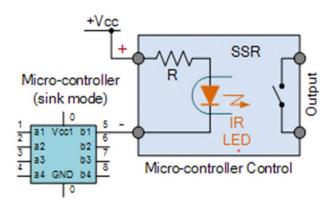

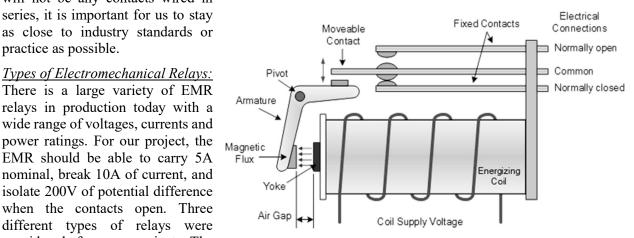

|    | 3.3.7                  | Output Contacts                                              |    |  |  |

|    | 3.3.8                  | Sense Inputs                                                 |    |  |  |

|    | 3.3.9                  | Led Indicators                                               |    |  |  |

|    | 3.3.10                 |                                                              |    |  |  |

|    | 3.3.11                 | 1 2                                                          |    |  |  |

|    | 3.3.12                 |                                                              |    |  |  |

|    | 3.3.13                 |                                                              |    |  |  |

|    | 3.3.14                 |                                                              |    |  |  |

|    | 3.3.15                 | $\varepsilon$ $\varepsilon$ $\varepsilon$ $\varepsilon$      |    |  |  |

|    | 3.3.16                 | 1 11                                                         |    |  |  |

|    | 3.3.17                 | , , , , , , , , , , , , , , , , , , , ,                      |    |  |  |

|    | 3.3.18                 | $\mathcal{E}$                                                |    |  |  |

| _  | 3.3.19                 |                                                              |    |  |  |

| 4. |                        | dards                                                        |    |  |  |

| 5. |                        | Design Constraints                                           |    |  |  |

|    |                        | conomic Constraints                                          |    |  |  |

|    | -                      | me Constraints                                               |    |  |  |

|    |                        | afety Constraints                                            |    |  |  |

|    |                        | nvironmental, Sustainability, and Sociopolitical Constraints |    |  |  |

| 6. | System hardware Design |                                                              |    |  |  |

|    |                        | vervoltage Protection Design                                 |    |  |  |

|    | 6.2 Ct                 | urrent-Sensing Design                                        | 80 |  |  |

|      | 6.3               | Voltage-Sensing Design                                    | 82  |

|------|-------------------|-----------------------------------------------------------|-----|

|      | 6.4               | ADC Design                                                | 83  |

|      | 6.5               | Output Contact Design                                     |     |

|      | 6.6               | LED Indicator Design                                      |     |

|      | 6.7               | Sense Input Design                                        |     |

|      | 6.8               | Push-Button Design                                        |     |

|      | 6.9               | Microcontroller Design                                    |     |

| _    | 6.10              | Power Electronics Design                                  |     |

| 7.   | Systen<br>7.1     | Philosophy and Development Environment                    |     |

|      | 7.1               | Software Version Control                                  |     |

|      | 7.2               | Phasor Construction                                       |     |

|      | 7.3<br>7.4        | Protection Algorithm Design                               |     |

|      | 7.5               | LCD Display Design                                        |     |

|      | 7.6               | Desktop Application Design                                |     |

| 8.   |                   | n Fabrication                                             |     |

|      | 8.1               | PCB Design Software                                       |     |

|      | 8.2               | PCB Design Philosophy                                     | 101 |

|      |                   | 8.2.1 Reliable PCB Design Practices                       | 103 |

|      | 8.3               | PCB Schematics                                            |     |

|      | 8.4               | Enclosure Design                                          |     |

| 9.   |                   | ype System Testing                                        |     |

|      | 9.1               | Prototype Hardware Testing                                |     |

|      | 9.2               | Prototype Software Testing                                |     |

|      |                   | 9.2.1 PHATCAT Software Testing                            |     |

| 10   | TI N              | 9.2.2 Desktop Application Testing                         |     |

|      |                   | ual Instructionstive Content                              |     |

| 11./ | Aummistra<br>11.1 | Project Budget                                            |     |

|      | 11.1              | Milestones                                                |     |

| 12.1 |                   | nmary and Conclusion                                      |     |

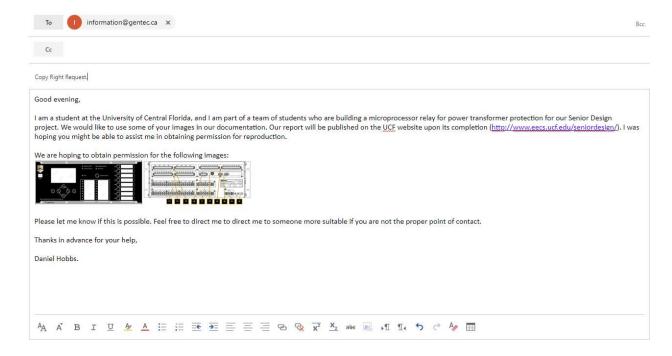

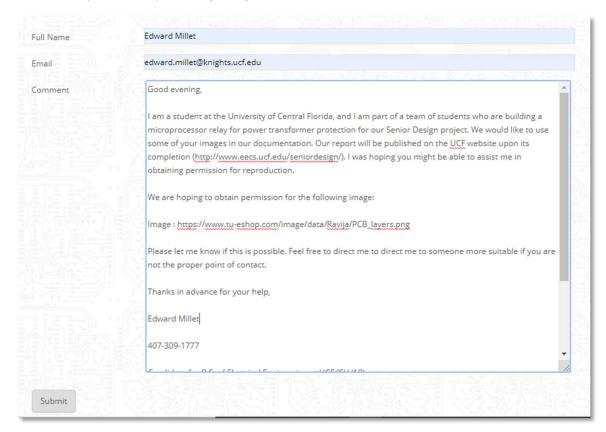

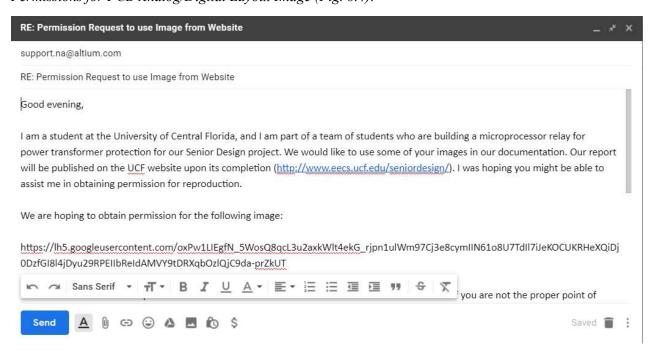

|      |                   | Copyright Permissions                                     |     |

|      |                   | References                                                |     |

|      | L                 |                                                           |     |

| Lic  | T OF FIGUR        | DEC                                                       |     |

|      |                   |                                                           |     |

| Fig  | . 2.2. A          | modern microprocessor relay                               | 2   |

| _    |                   | ribution transformer in a substation                      |     |

|      |                   | ept of microprocessor relay front (Top) and rear (bottom) |     |

| _    | •                 | et hardware diagram                                       |     |

| _    | •                 | et software diagram                                       |     |

|      |                   | sformer's magnetic and electrical circuits                |     |

| Fig. | 3.2. A non        | i-ideal transformer model                                 | 10  |

|      |                   | connection for three coils                                |     |

| _    |                   | connection for three coils                                |     |

| Fig. | 3.6. 230kV        | gas-insulated breaker with bushing mounted CTs.           | 12  |

| Fig. 3.7. A typical CT excitation curve                                                      | 12 |

|----------------------------------------------------------------------------------------------|----|

| Fig. 3.10. Reading circuit breaker position with sense input                                 | 13 |

| Fig. 3.9. Controlling a circuit breaker with a relay contact                                 | 13 |

| Fig. 3.11. Basic logic gates with relaying circuitry                                         | 14 |

| Fig. 3.13. Coordinated Overcurrent Settings                                                  | 15 |

| Fig. 3.12. PHATCAT as 51 on Distribution Transformer.                                        | 15 |

| Fig. 3.14. Restrained Differential Element                                                   | 15 |

| Fig 3.15. SEL487 relay                                                                       | 18 |

| Fig 3.16. SIPROTEC series relays                                                             | 18 |

| Fig. 3.17. I-V Characteristic of a TVS Diode                                                 | 21 |

| Fig. 3.18. Hall effect seen in an IC                                                         | 24 |

| Fig. 3.19. Current Transformer with terminals                                                | 25 |

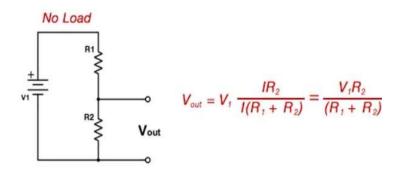

| Fig. 3.21. Voltage Divider with no load                                                      | 27 |

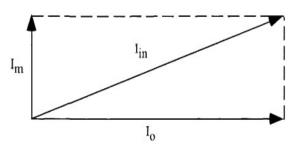

| Fig. 3.22. Input current relationship                                                        | 27 |

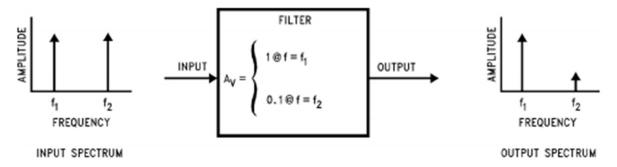

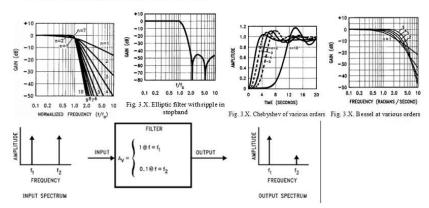

| Fig. 3.23. Amplitude vs. frequency affected by a filter                                      | 33 |

| Fig. 3.24. Fundamental frequency and additional harmonics                                    | 33 |

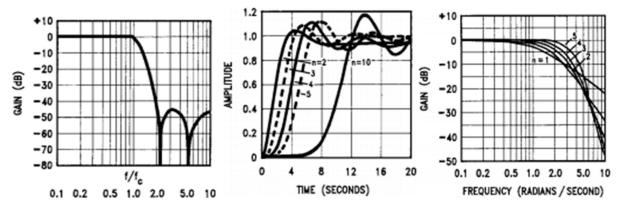

| Fig. 3.26. Butterworth filter of various orders                                              | 34 |

| Fig. 3.25. Elliptic (Left), Chebyshev (Center), and Bessel (Right) filters at various orders | 34 |

| Fig 3.27. DMA Block Diagram                                                                  | 39 |

| Fig. 3.28. Solid-State relay                                                                 | 41 |

| Fig. 3.29. Electromechanical Relay                                                           | 41 |

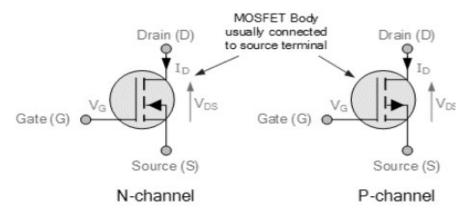

| Fig. 3.30. N-channel and p-channel MOSFETs                                                   | 45 |

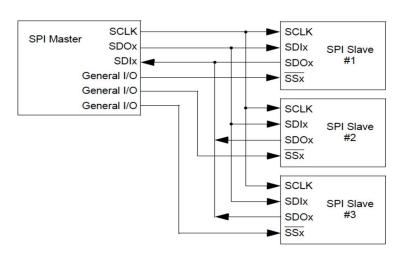

| Fig 3.31. Master Slave SPI                                                                   | 56 |

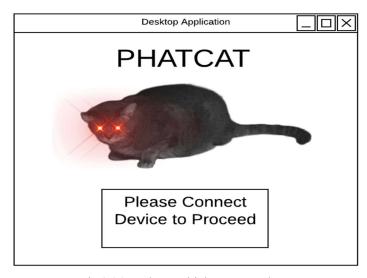

| Fig 3.34 Desktop Initial Open Mockup                                                         | 62 |

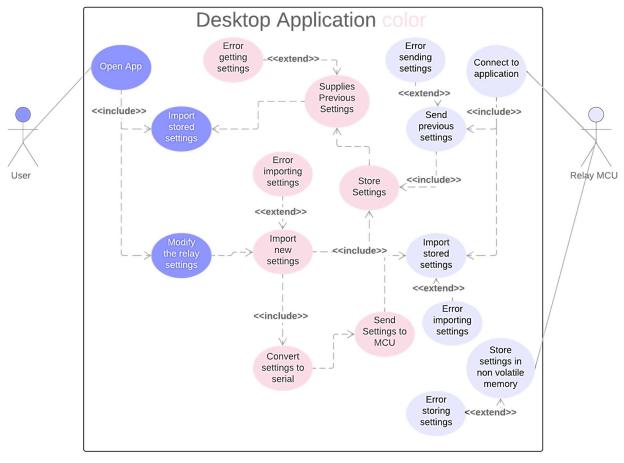

| Fig 3.33. Desktop Use Case Diagram                                                           | 63 |

| Fig 3.35 Desktop Config Settings Mockup                                                      | 63 |

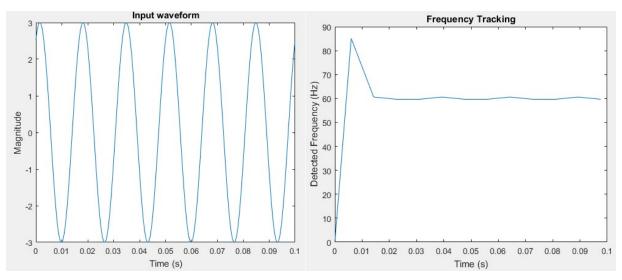

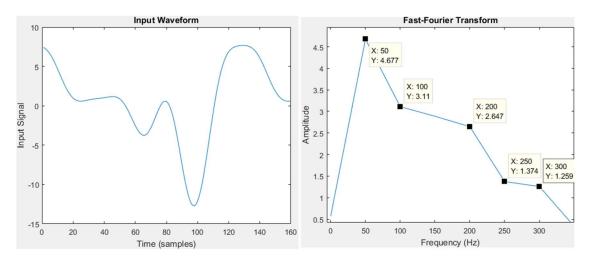

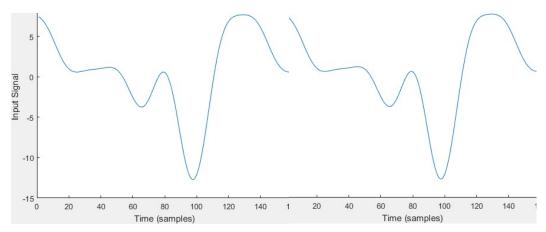

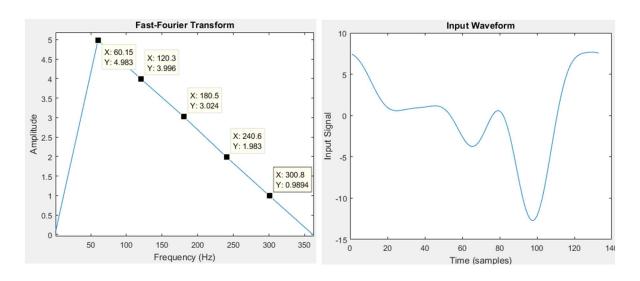

| Fig. 3.36. Input waveform for ZCD algorithm (left) and algorithm results (right)             | 65 |

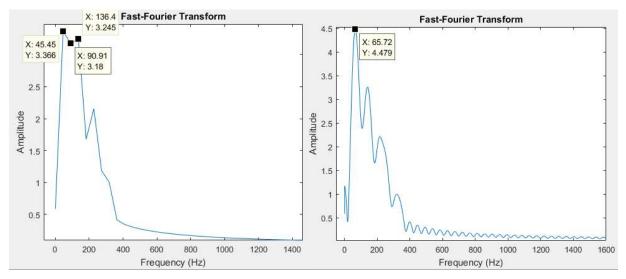

| Fig. 3.37. Fundamental frequency detection without (left) and with (right) zero padding      | 66 |

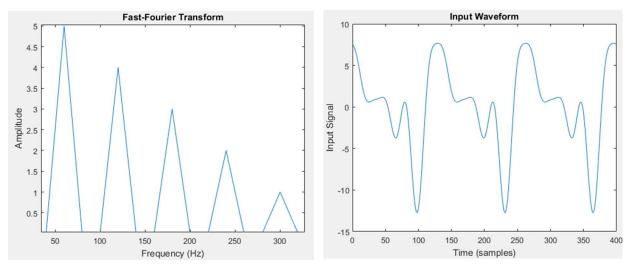

| Fig. 3.38. FFT Magnitude Components and Input Waveform – 50ms window                         | 67 |

| Fig. 3.39. FFT Magnitude Components and Input Waveform – 20ms window                         | 68 |

| Fig. 3.40. Discontinuity between periods of sampled signal                                   | 68 |

| Fig. 3.41. FFT Magnitude Components and Input Waveform                                       | 68 |

| Fig. 3.42. Standard Relay Rack                                                               | 70 |

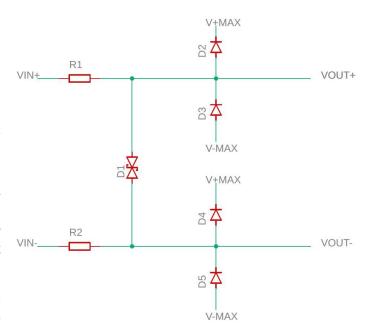

| Fig. 6.1 Baseline overvoltage protection design.                                             | 80 |

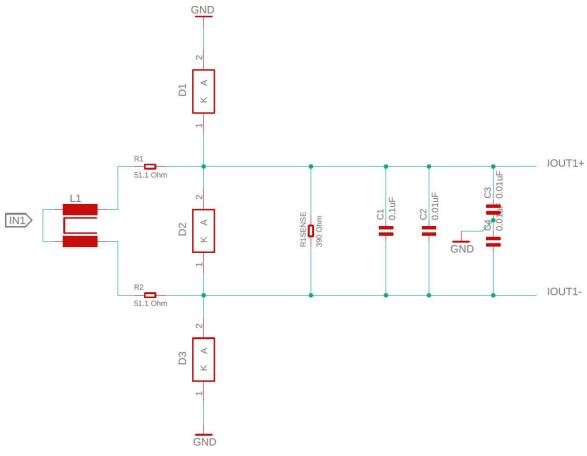

| Fig. 6.2 Current Sensing Schematic                                              | 81  |

|---------------------------------------------------------------------------------|-----|

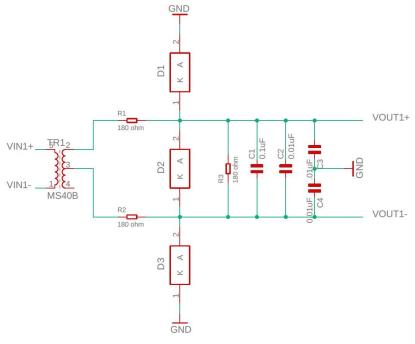

| Fig. 6.3 Voltage Sensing Schematic                                              | 82  |

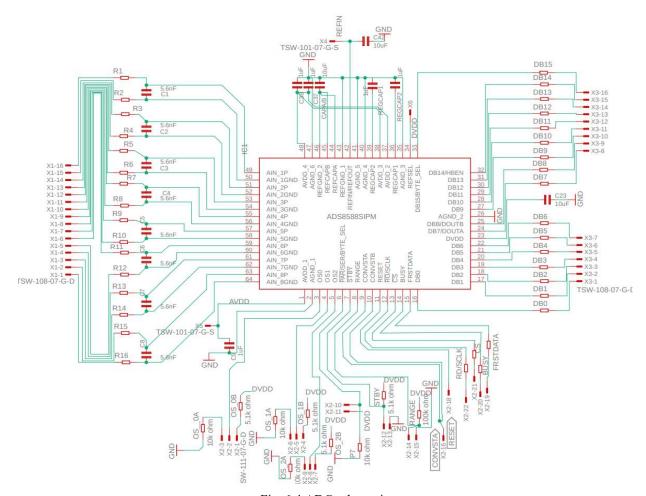

| Fig. 6.4 ADC schematic                                                          | 83  |

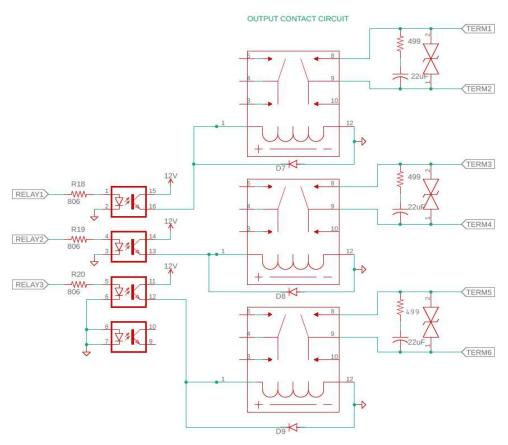

| Fig. 6.5 Output Contacts Circuit Schematics                                     | 85  |

| Fig. 6.6 LED Indicator Circuit Schematic                                        | 86  |

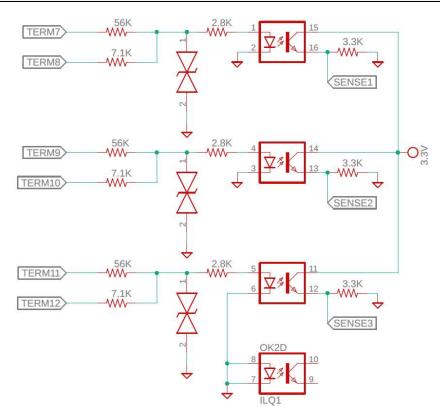

| Fig. 6.7 Sense Input Circuit Schematic                                          | 87  |

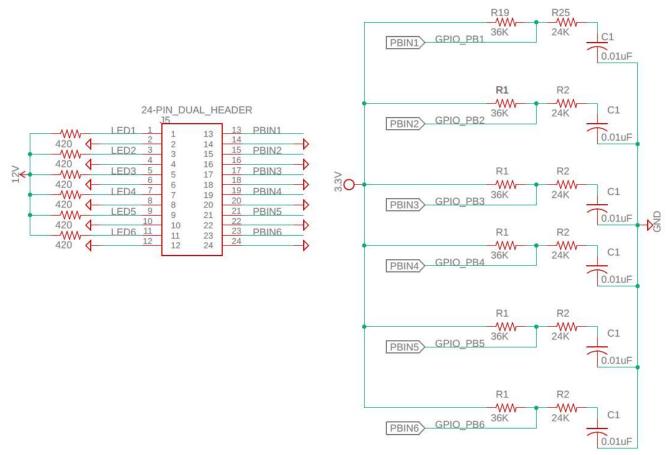

| Fig. 6.8 Push Button Circuit Schematic                                          | 88  |

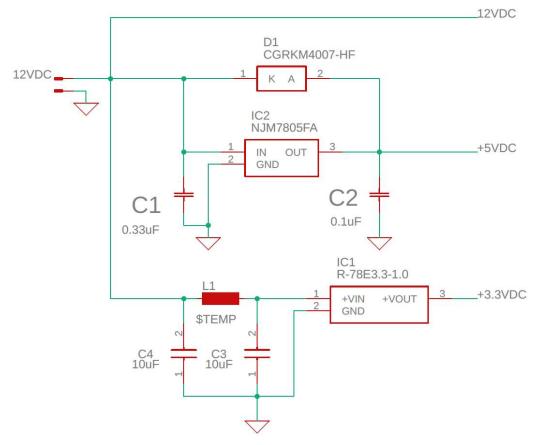

| Fig. 6.10. Power Electronics Design                                             | 90  |

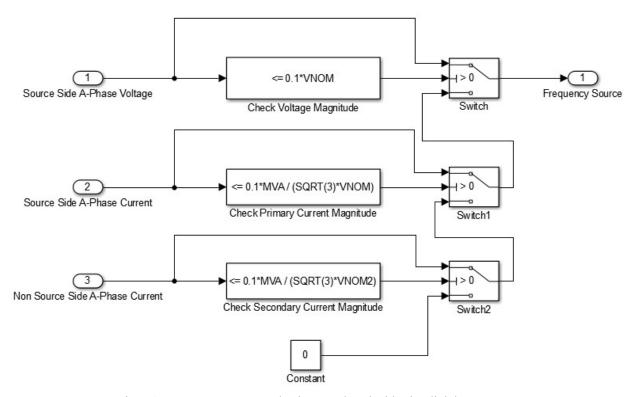

| Fig. 7.1. Frequency Source Selection                                            | 96  |

| Fig 7.2 Information shown on PHATCAT's display                                  | 99  |

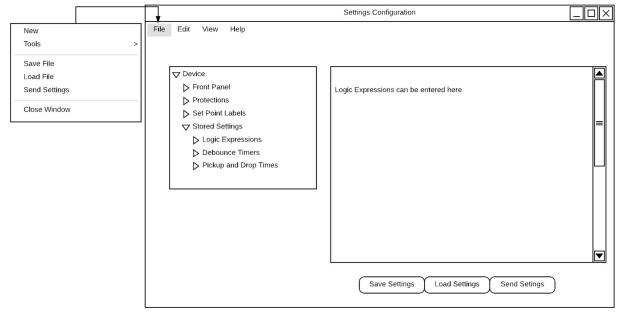

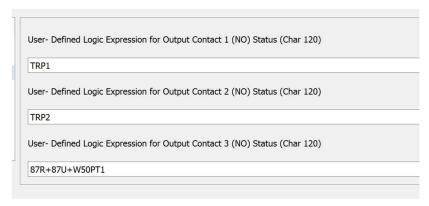

| Fig. 7.3 User Entered Logic Expression                                          | 100 |

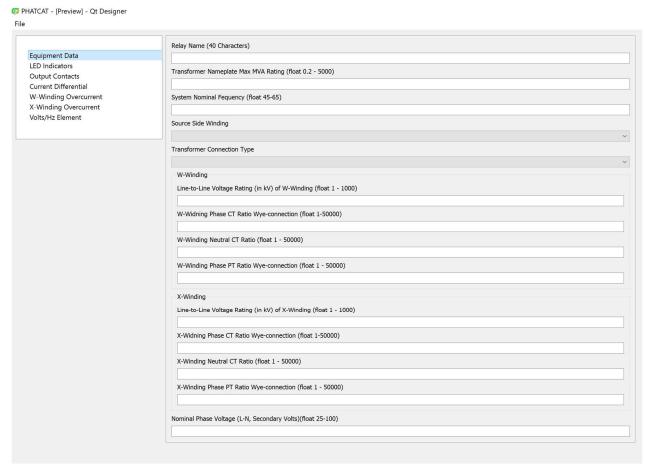

| Fig. 7.4 Desktop Application Settings                                           | 100 |

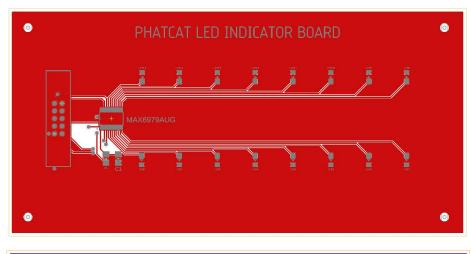

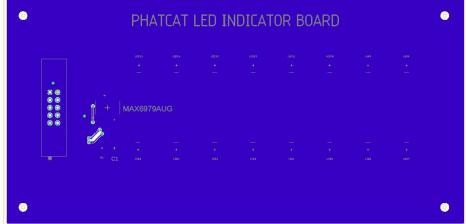

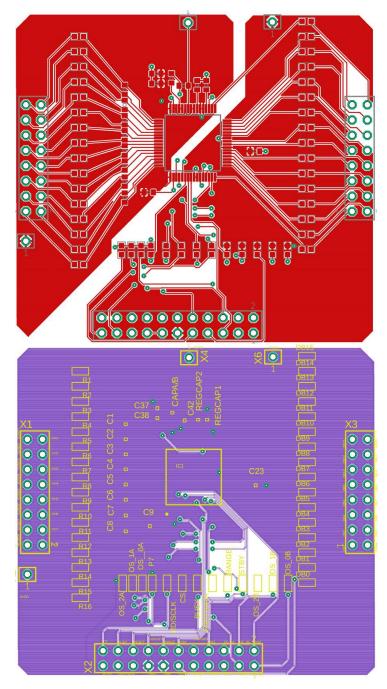

| Fig. 8.6 LED Indicator Board Layout – Top (Red) and Bottom (Blue) Layers. Board | 106 |

| Fig. 8.7 ADS8885S breakout board layout, top (Red) and bottom (purple) layers   | 107 |

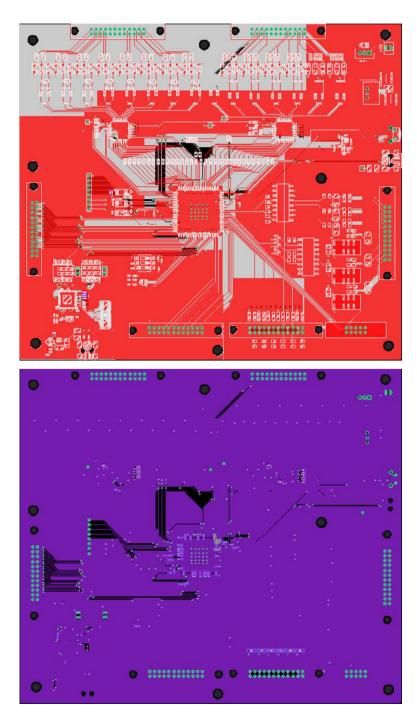

| Fig 8.8 Main board layout, top (Red) and bottom (purple) layers                 | 108 |

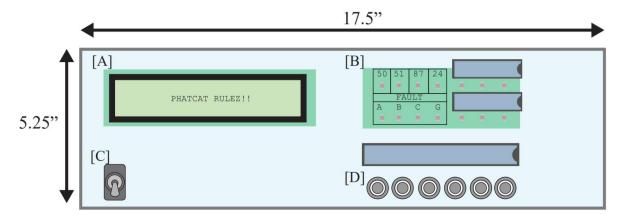

| Fig. 8.9 PHATCAT Front Panel Illustration.                                      | 109 |

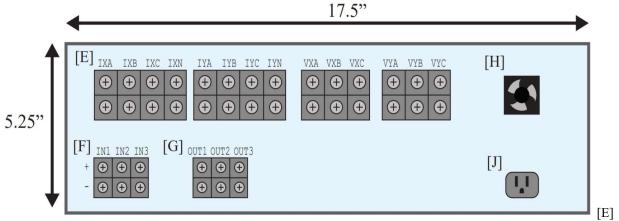

| Fig. 8.10 PHATCAT Rear Panel Illustration                                       | 110 |

| Fig. 8.11 PHATCAT Side View Illustration.                                       | 110 |

| LIST OF TABLES                                                                  |     |

| Table 2.3.1. Rear Panel Current and Voltage Measurements                        | 7   |

| Table 2.3.2. Rear Panel Control Inputs/Outputs                                  | 8   |

| Table 2.3.3. Protection Function Specifications                                 | 8   |

| Table 2.3.4. External & User Facing Features                                    | 8   |

| Table 2.3.5 Realistic Design Constraints                                        | 9   |

| Table 3.1. Comparison of PHATCAT and market offerings                           | 19  |

| Table 3.2. Considered Transformer and Isolation Amplifier                       | 23  |

| Table 3.3 Current Sensing Methodology Comparison                                | 29  |

| Table 3.4 Current Transformer Comparison                                        | 30  |

| Table 3.5 Current Sensing Shunt Resistor Comparison                             | 32  |

| Table 3.6. Four common filter design comparison                                 | 35  |

| Table 3.7. Programmable gain amplifiers considered                              | 36  |

| Table 3.8. Analog-to-digital converters under consideration                     | 38  |

| Table 3.9 Electromechanical Relays Considered                                   | 42  |

| Table 3.10: LED Driver Comparison                               | 46  |

|-----------------------------------------------------------------|-----|

| Table 3.11. Power Toggle Switch Comparison Table                | 47  |

| Table 3.12 Momentary Push Button Comparison                     | 48  |

| Table 3.13 Display options considered                           | 50  |

| Table 3.14. Estimate input and output needs for microcontroller | 52  |

| Table 3.15. Memory needed for storing user-settings             | 53  |

| Table 3.16. Microcontroller options considered                  | 54  |

| Table 3.17. PHATCAT Approximate Power Needs                     | 55  |

| Table 3.18. PHATCAT Power Electronics                           | 55  |

| Table 3.19 Embedded Application Language Comparison             | 60  |

| Table 3.20 Desktop Application Language Comparison              | 61  |

| Table 3.19 – Comparison of materials for enclosure              | 72  |

| Table 6.1 - Current Sensing BOM                                 | 81  |

| Table 6.2 - Voltage Sensing BOM                                 | 82  |

| Table 6.3 – Analog to Digital BOM                               | 84  |

| Table 6.4. BOM – Output Contact Circuits                        | 85  |

| Table 6.5 BOM – LED Indicator Circuits                          | 86  |

| Table 6.6 BOM – Sense Input Circuits                            | 87  |

| Table 6.7 BOM – Push Button Circuits                            | 89  |

| Table 6.8. BOM – Power Electronics                              | 90  |

| Table 7.1 Comparison of Python Development Environments         | 92  |

| Table 7.2 Coefficients of U.S. Relay Curves                     | 97  |

| Table 7.3. Test Case for PHATCAT's Metering Functionality       | 115 |

| Table 10.1: Project Budget                                      | 122 |

| Table 10.2: Project Documentation Milestones                    | 123 |

| Table 10.3: Prototyping Execution Milestones                    | 123 |

#### 1. EXECUTIVE SUMMARY

On all fronts—academic, political, and industrial, there is a great deal of change and growth occurring in the electrical power industry. This comes after a period of long stagnation which has resulted in a high need for educated, young power engineers. One key facet of power systems is their protection and control. Sparked by a desire to both learn and create a needed educational resource, PHATCAT was originally conceived to provide insight into the design and functionality of modern microprocessor relays, which are the heart of the power system's protection and control.

PHATCAT is primarily intended for protecting large, three-phase power transformers, such as those located in substations. It contains a suite of protective algorithms commonly used in power system protection, including time-inverse overcurrent, restrained current differential with harmonic blocking, and overexcitation protection (Volts/Hz). It uses transducers and digital signal processing to convert analog voltage and current signals into internal phasor representations of power system quantities. By manipulating these phasors, it accommodates different kinds of transformer connections and turns ratios. Additionally, PHATCAT provides all of the functionality necessary for interfacing with other substation equipment. It possesses DC sense inputs for reading binary statuses, such as circuit breaker positions. It also has switchable contacts for providing binary statuses to other devices or energizing circuits (e.g. a circuit breaker trip coil circuit). PHATCAT provides user-interactivity, displaying power system data on its front panel, indicating protective trips with LEDs, and receiving user-commands with pushbuttons. All of these functions are user-customizable with a desktop application – important setpoints for protective algorithms, transformer data, LED behavior, push button behavior, sense input behavior, and output contact behavior are all robustly customizable via a graphical user interface that supports user-defined Boolean expressions. These settings can then be easily downloaded to PHATCAT via USB.

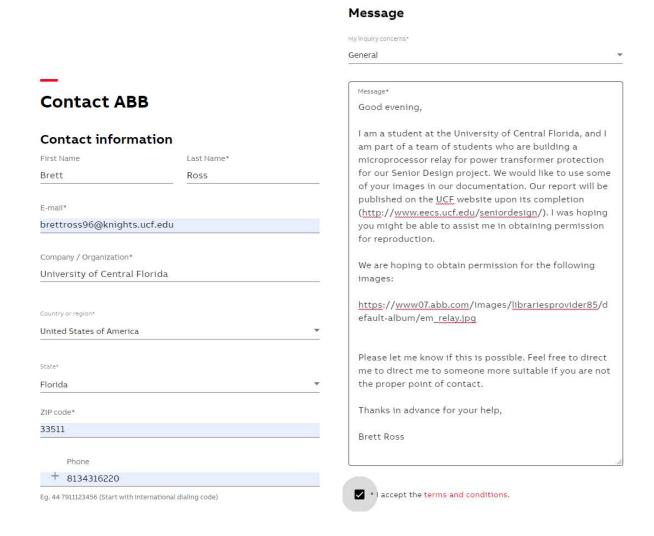

This paper documents PHATCAT's design process, including key technologies and theory, design philosophy, relation to current industry practices, testing, and fabrication. The project's context is provided first, along with a detailed set of engineering requirement specifications for PHATCAT. Important technologies and protective algorithms are briefly discussed, and two state-of-the-art transformer protective relays are analyzed. A detailed discussion of PHATCAT's core components is then given and general hardware and software implementations are chosen. Real world design constraints, such as those imposed by sociopolitical factors and standards, are also analyzed. More detail is then provided regarding the detailed design of PHATCAT, including abbreviated circuit schematics and bills of material. The actual fabrication plan for PHATCAT is then provided, including printed circuit board (PCB) schematics. Next, the test plan for evaluating PHATCAT's performance is given. Administrative content, such as project milestones and the project budget are also documented before the project's final conclusions are presented. Appendixes are provided containing permissions for copyrighted material reproduced and references.

#### 2. Project Description

In the Project Description, the background of the project is first shared, along with the factors motivating its selection for Senior Design. The qualitative objectives are then provided—these statements define what the project should provide to the authors and readers, as well as what final prototype should be capable of on a high-level. Lastly, the required specifications are listed. These quantitative guidelines establish the required physical capabilities of those features of the final prototype necessary for it to achieve the project objectives.

#### 2.1 PROJECT BACKGROUND AND MOTIVATION

The reliable availability of high-quality electric power is foundational in nearly every aspect of modern society. Furthermore, there is a great deal of academic and industrial development ongoing in the energy sector. UCF recently appointed a Director of Energy Initiatives, devoted exclusively to helping UCF become a leader in the field. Duke Energy, a utility serving ~ 2 million electric customers in Florida, is currently launching some of the most sweeping and expensive transmission upgrades in the company's history. All over the world, new applications are being pushed and tested to modernize the way power systems are engineered. A critical system within each aspect of power systems, from generation to distribution, is that which provides the system's protection and control.

Protection systems are responsible for detecting system disturbances (e.g., faults) and taking actions to mitigate their effects. Control systems are responsible for regulating power systems equipment for optimal system performance. Devices, referred to as 'relays,' are used to perform these functions. The first relays were electromechanical, but microprocessors, first applied in the late 1960's, have since risen to become the predominate technology (Fig 2.2). Modern microprocessor relays¹ receive analog voltages and currents from instrument transformers that correspond to voltages and currents in the power system by a known ratio. These signals pass through analog filters before being sampled digitally, from which phasor representations are derived. Most modern relay features work in the phasor domain (c.f. [2.1]). A wide variety of fault detection functions are in use today, each with varying requirements for proper application. This project seeks to design a microprocessor relay capable of performing the protection functions for a power transformer.

Power transformers facilitate the transfer of power between two points in a power system that are at different voltages. This occurs often. High voltage (e.g., 230kV) is preferred for transmission of power due

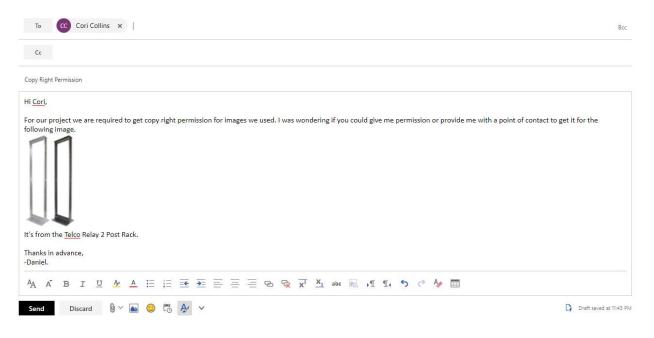

Fig. 2.2. A modern microprocessor relay. Reproduced with the permission of GE Grid Solutions.

<sup>&</sup>lt;sup>1 1</sup> To those outside the power systems industry, this may sound almost like an oxymoron. However, this is commonly used terminology and stems from both their electromechanical heritage and their frequent use of switching as a response to disturbances.

to its higher efficiency and lower voltage drop. Medium voltage (e.g., 13kV), on the other hand, is preferred for generation and distribution of power due to its lower insulation requirements. Microprocessor relays are typically applied larger for (10MVA+)transformers such as those housed at substations and generation plants. Even the smaller, lower voltage transformers such as those at distribution stations. can cost several hundred-thousand dollars and weigh several hundredthousand pounds. This makes them valuable assets that can take as long as a year to replace. As such, great care is taken to monitor their condition and ensure that, should a disturbance occur, they are de-energized before they can

Fig. 2.3. A distribution transformer in a substation. Photo by B. Ross.

become damaged. However, it is not enough for this monitoring to merely detect disturbances. It must also be able to differentiate between different kinds of disturbances and behave appropriately.

Consider a distribution transformer that supplies multiple distribution lines. It is undesirable for a transformer's protection to trip immediately for a single faulted distribution line—this would take all distribution lines out of service. Instead, a different protection is designed specifically to detect faults on a particular feeder. It should trip first. However, this feeder protection may not always work perfectly. So, the transformer protection must serve as a backup, tripping when other protections are malfunctioning. In the industry, this process is referred to as 'coordination.' A protection system must not only be able to detect disturbances, but to differentiate between the different kinds of disturbances that necessitate different actions be taken.

This particular project is motivated by several drivers. Senior Design serves as the capstone achievement for the ABET engineering undergraduate. It is a demonstration of technical and interpersonal competency, as well as of dedication and self-motivation. In these ways, it serves to help validate that those who succeed in it are worthy of an engineering degree and the responsibility it confers. Through the completion of this project and the development of a working prototype, this validation is achieved. This specific project originated as a result of some authors' power systems backgrounds and their desire to further their knowledge in the field of protection and controls. A transformer was chosen as the various challenges associated with its protection serve as examples of the power of phasor-based protection but do not require communications for effective function. Support for protection communications was determined to be out of the scope for this project. As will be seen in Sections 2.2 and 2.3, the wide variety of functionalities required presents an interesting and complex project that requires knowledge in many different fields of electrical and computer engineering.

It is important to clarify that the purpose of this project is not innovation, it is education. It is only in recent years that energy has become a dynamic field; for many years, it was highly static when compared to industries such as communications and integrated circuit design. But the coal plants and radially-fed distribution systems that have powered America for over a century are no longer sufficient for today's sustainability and efficiency requirements. As a result, the energy industry is now facing a large body of complex work that must be undertaken at a time when many of their experts are retiring. Young engineers are very rapidly having to take on and execute multi-million-dollar projects. Furthermore, the ever-expanding role of communications in protection and controls has made cyber-security a cause of great focus

from regulating bodies. This had led to ever stricter and more complex compliance requirements being placed upon protection and controls engineers.

These factors culminate in what is a very challenging and dynamic time for protection and controls engineering, heightening the risk of human performance errors. The penalty for such errors can be quite severe. Service outages for thousands, millions of dollars in equipment damage, and even loss of human life can occur if protection and controls systems are not engineered to the highest level of robustness and resiliency. It is the authors' hope that this project's educational benefit will serve as a countermeasure, extending beyond their own personal growth to contribute to the industry, where other young engineers can gain deeper insight into how microprocessor relays function.

## 2.2 Project Objectives

PHATCAT carries out a series of protection functions that accurately detect certain system disturbances with the goal of protecting two-winding three-phase transformers. It differentiates between different kinds of disturbances that necessitate different action. These protection functions include instantaneous overcurrent, time-inverse overcurrent, current differential, overexcitation, and harmonic blocking. In order to carry out these functions, it performs all of the signal processing necessary. Incoming analog signals coming from three-phase potential transformers and current transformers are converted into digital representations of phasors. The sequence components of these three-phase phasors are also calculated before they can be used in the protection functions. The percentage values of certain harmonics are also calculated.

PHATCAT is able to close and open output contacts. The term 'contacts' is used to make their function clear, but the actual mechanism may be electromechanical or solid-state. These contacts can be wired up so as to operate other equipment such as circuit breakers that will mitigate the disturbance's impact and/or remove the disturbance from the power system. It also possesses 'coils' that can sense active high/low inputs and use these in internal logic. This allows for sensing the closing of other contacts, such as those that represent breaker positions, or for certain auxiliary functions, such as the sensing of transformer alarms, to be performed by the relay.

PHATCAT also supports a modicum of flexibility; nearly every application of protective relays requires engineering specific to the situation at hand. Short circuit studies, custom logic equations, and wiring external to the relay are all used when protecting and controlling power systems equipment. In the current state-of-the-art, it is not possible to sell a transformer protection relay that requires no engineering work for its application. The relay must then allow for easy configuration of those characteristics that might need to be altered during its application. This is done through the use of a graphical-user interface (GUI) driven program running on a PC. This allows for the creation of files that determine the relay's behavior as well as the retrieval of the relay's current configuration.

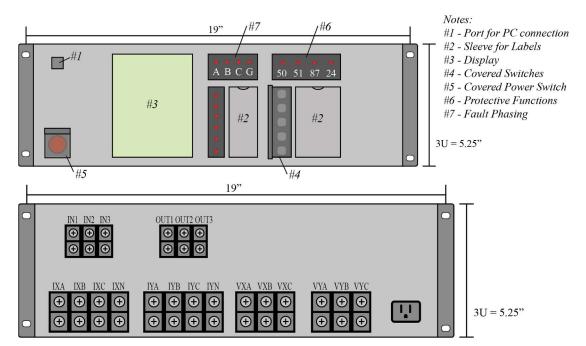

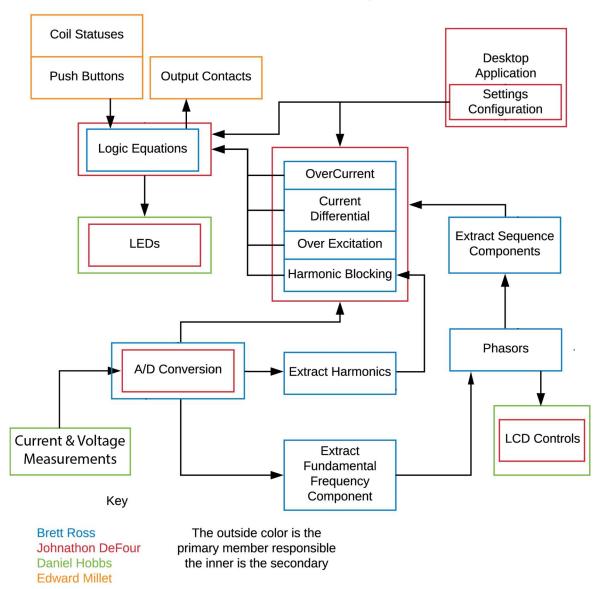

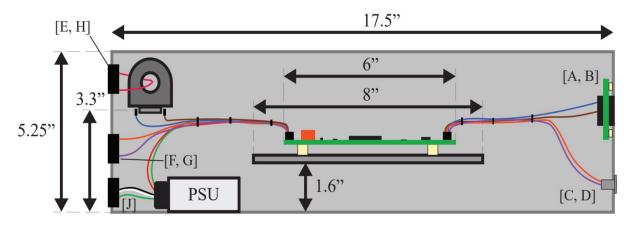

Field personnel are also able to gain insight into the PHATCAT's measurements and perform basic configuration changes by interacting with it. A display showing the measured currents and voltages is used. The relay has a setting for inputting used instrument transformer ratios and use this to present values in primary-side quantities. The relay has a two-factor power switch that prevents accidental switching. It should also have LEDs and push-buttons or switches on the front panel. Some LED and push-button functions can be hard-coded, but some are also available for use in custom logic equations. Fig. 2.4 depicts a concept of PHATCAT's physical construction. Fig. 2.5 and 2.6 relate hardware and software block diagrams of PHATCAT's functionalities.

In the documentation of all these features' implementation, reference is made to specifications and features utilized in industry wherever possible. While it is not always feasible to meet these specifications given the time, capital, and labor resources available, the goal of this project is to inform the readers about microprocessor relays. As such, industry practices will be shared, even when their implementation lies outside the scope of the project.

Fig. 2.4. Concept of microprocessor relay front (Top) and rear (bottom). By B. Ross

Hardware Block Diagram

#### Front Panel Microcontroller Two-Factor Power Switch GPIO Display GPIO LEDs **Output Contacts** IC Power & Sense Inputs Push Buttons / Switches Transient A/D Conversion Protection IC-Level Analog IC Power Voltages Instrumentation Step Down Board (PCB) Low-Pass Filters High Voltage to Low Voltage Conversion Curent to Voltage Conversion Transient Protection Transient Protection Power Supply Outside Device PTs/CCVTs in Substation Yard Relaying Circuitry User 120 VAC CTs in substation yard Key Brett Ross Johnathon DeFour Outside color primarily

Fig. 2.5. Project hardware diagram. By document authors.

At this time, all blocks are 'To be Acquired'

Daniel Hobbs

Edward Millet

## Software Block Diagram

Fig. 2.6. Project software diagram. By document authors.

## 2.3 REQUIRED SPECIFICATIONS

In order to achieve the project objectives, the following specifications are required:

Table 2.3.1. Rear Panel Current and Voltage Measurements

| Required Specifications                                 | Current Measurements  | Voltage Measurements  |

|---------------------------------------------------------|-----------------------|-----------------------|

| Qty                                                     | 8                     | 6                     |

| $f_{-3db}$ Frequency                                    | $2(kHz) \pm 10\% \le$ | $2(kHz) \pm 10\% \le$ |

| Capture $2_{nd}$ , $4_{th}$ , and $5_{th}$<br>Harmonics | Accuracy ±10%         | Accuracy ±10%         |

| Sampling Rate                                           | 650(Hz) ≤             | 650(Hz) ≤             |

| Fundamental Frequency<br>Tracking Range                 | 45-65(Hz)             | 45-65(Hz)             |

| Phasors: Magnitude and Phase                            | Accuracy:             | Accuracy:             |

|                                                         | Magnitude-±5%         | Magnitude-±5%         |

|                                                         | Phase-±1              | Phase-±1              |

| Continuous Thermal Rating                               | 5(A)                  | N/A                   |

| One Second Thermal Rating                               | 30(A)                 | N/A                   |

| ESR                                                     | 100(mΩ)               | $1(k\Omega)$          |

| Current Rating                                          | ≤30(A)                | N/A                   |

| Voltage Rating                                          | N/A                   | 67(V)                 |

Table 2.3.2. Rear Panel Control Inputs/Outputs

| Required Specifications | Detect 125VDC Input Signal | Output Contact Signal   |

|-------------------------|----------------------------|-------------------------|

| Qty                     | 3                          | 3                       |

| Current Rating          | >10(mA)                    | ≤2(A)                   |

| Voltage Rating          | 125(VDC)                   | OPEN CIRCUIT @ 125(VDC) |

| Breaking Capacity       | N/A                        | 2(A)                    |

| Voltage Drop            | N/A                        | ≥1(V)                   |

Table 2.3.3. Protection Function Specifications

| Required Specifications | Instantaneous<br>Overcurrent | Inverse-Time<br>Overcurrent | Instantaneous<br>Differential | Restrained<br>Differential | Over-<br>excitation |

|-------------------------|------------------------------|-----------------------------|-------------------------------|----------------------------|---------------------|

| Trip Time               | <u>+</u> 10%                 | <u>+</u> 10%                | <u>+</u> 10%                  | <u>+</u> 10%               | <u>+</u> 10%        |

|                         | Set Trip Time                | Set Trip Time               | Set Trip Time                 | Set Trip Time              | Set Trip            |

|                         | ≤ 33.3ms                     | ≤ 33.3ms                    | ≤ 33.3ms                      | ≤ 33.3ms                   | Time                |

|                         |                              |                             |                               |                            | ≤ 33.3ms            |

| Trip Value              | <u>+</u> 10%                 | <u>+</u> 10%                | <u>+</u> 10%                  | <u>+</u> 10%               | <u>+</u> 10%        |

|                         | Set Trip Value               | Set Trip<br>Value           | Set Trip Value                | Set Trip Value             | Set Trip<br>Value   |

Table 2.3.4. External & User Facing Features

| Feature                       | Quantity | Purpose                                                                                                                           |  |

|-------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| Front Panel Indicator         | 16       | 1-Indicate Power On                                                                                                               |  |

| LEDs                          |          | 4-Indicate Phasing of a Detected Fault(A,B,C,G)                                                                                   |  |

|                               |          | 5-Indicate Protection Function(50,51,87,24)                                                                                       |  |

|                               |          | 6-User programmable LEDs                                                                                                          |  |

| Front Panel Push Buttons      | 6        | User Programmable Buttons                                                                                                         |  |

| Front Panel Power Switch      | 1        | Power Disconnect                                                                                                                  |  |

| Front Panel LCD Display       | 1        | Display Measured Current and Voltage Phasors                                                                                      |  |

| Power Electronic<br>Enclosure | 1        | An Enclosure for relay electronics capable of being mounted in a 19" equipment  Screw Terminals required for external connections |  |

| PC Application                | 1        | Deliver user defined configuration to the microcontroller Retrieve the device's current configuration                             |  |

Table 2.3.5. Realistic Design Constraints

| Type of Constraint         | Reason                                                                                                                                                |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Time Constraints           | Completion times must abide by milestone documentation                                                                                                |  |

| Economic Constraints       | Assets paid for by sponsor must have purchase documentation                                                                                           |  |

| Sustainability Constraints | Authors must provide technical grounds for exceeding initial budget                                                                                   |  |

| Safety Constraints         | Components cannot be used if declared as obsolete or for new design                                                                                   |  |

| Sociopolitical Constraints | The device must not support any form of wireless communication or LAN connectivity                                                                    |  |

| Standard Constraints       | All communications should abide by communication protocol standards                                                                                   |  |

|                            | All circuits should have galvanic isolation in some form (optocouplers, transformers, etc) between the outermost component and the rest of the relay. |  |

|                            | All circuits should have overvoltage protection capable of protecting the input/output from a 50% overvoltage for at least 15 ms                      |  |

|                            | No protection on current sense circuits is to create an open circuit, either intentionally or by failure                                              |  |

#### 3. Research

In this section, several key technologies and relevant concepts are related to provide context for key aspects of PHATCAT's functionality. A brief market analysis of transformer protection offerings is then conducted. Core implementations for PHATCAT's functionality are then explored.

#### 3.1 Relevant Technologies

Due to the project's specialized application, relevant technologies are presented before the market offerings, providing context.

#### 3.1.1 POWER SYSTEM TRANSFORMERS

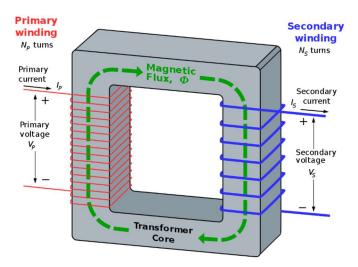

At a basic level, a transformer is a fairly simple device. Two coils of conductor are wound around a material with a high magnetic permeability (e.g. an iron core) such as to create a strong coupling of the magnetic fluxes through each of the coils (i.e. a high mutual inductance) (Fig. 3.1). As a result, a time changing voltage applied at the terminals of one winding generates a magnetic flux that in turn induces a voltage on the other winding. Faraday's law of induction relates the electromotive force (V) to the magnetic flux through a coil of N turns:

$$EMF = N \frac{d\Phi_B}{dt} \tag{3.1}$$

Because the voltage is proportional to the number of turns, a transformer with a perfect magnetic coupling relates the voltages in each coil by the ratio of the number of turns.

Fig. 3.1. A transformer's magnetic and electrical circuits. Credits to Bill C at the English language Wikipedia [CC BY-SA 3.0 (http://creativecommons.org/licenses/by-sa/3.0/)]

The currents flowing in the primary and secondary windings are inversely related to the voltages. Thus, if the transformer is lossless, power is conserved.

$$\frac{V_p}{V_s} = \frac{N_p}{N_s}$$

;  $\frac{I_s}{I_p} = \frac{N_p}{N_s}$ ;  $V_p I_p = V_s I_s$  (3.2, 3.3, 3.4)

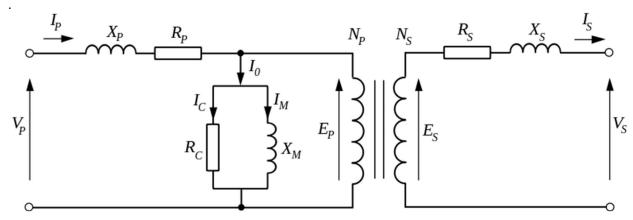

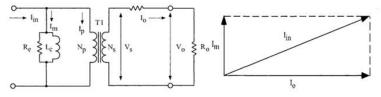

This relationship allows for transformers to facilitate the transfer of power between voltage levels. However, real transformers do not have this exact IV characteristic. An accurate steady-state model of a nonideal transformer is given in fig. 3.2

The series impedances model the resistance and self-inductance of the windings. The shunt impedance models two non-idealities within the transformer core: eddy currents and hysteresis loss. Eddy currents are unwanted currents induced in the transformer's core by the electromagnetic field. These cause losses and core heating and are often mitigated through the use of nonconductive layers of 'laminate' that break up current loops and reduce the ability of eddy currents to flow. Hysteresis loss results from the energy required to align the magnetic domains within the core material with the time-changing voltage. In reality, it is not a constant impedance value, but is dependent on past core states. For steady-state conditions, the shunt impedance of the transformer is very large, and the approximation is still very good.

Fig. 3.2. A non-ideal transformer model. Credit to Cblambert [CC BY-SA 3.0 (https://creativecommons.org/licenses/by-sa/3.0)]

For proper transformer protection, it is important to understand that the current flowing through the core losses, called the 'excitation current,' can sometimes be large. During transient conditions, especially during initial energization, large amounts of excitation current flow to magnetize the transformer core to its new steady state. This transient, referred to as 'inrush current,' contains large amounts of harmonic content, and the need to avoid an unintentional trip during transformer energization is the primary motivation for this project's incorporation of harmonic blocking. Another cause of large excitation current is 'core saturation.', Every iron core has a certain amount of flux it can produce. One this threshold is exceeded, the core begins to saturate and is unable to reproduce an accurate secondary current. This is modeled by a drastic reduction in the shunt impedance. This can cause damage to the transformer through excessive core heating. It can also cause the misoperation of certain protections. It can be shown that the degree of core excitation is proportional to the voltage divided by the system frequency. As such, 'Volts/Hz' or 'overexcitation' elements are used to protect against these conditions.

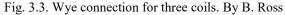

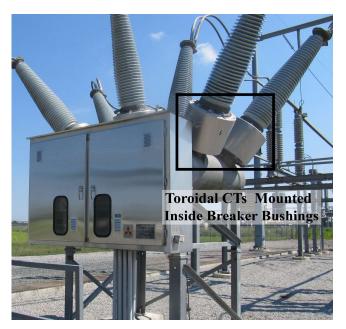

In three-phase systems, there are multiple ways to connect three sets of transformer windings. The first is 'wye' or 'star' connection (Fig 3.3). Three coils receive phase connections on one end and are joined in the center on the other. The center point may be grounded and/or connected to a neutral wire on which the system imbalance (i.e., the zero-sequence com) can flow. Another is the 'delta' connection (Fig 3.4). Three coils are connected end-to-end, forming a triangle. Phase conductors are connected at the vertices of the triangle. No neutral is used. A variety of transformer connections (e.g. Wye-wye, wye-delta, etc.) are formed that utilize these two connections in different combinations.

Depending on the combination of connections used, different transforms of phasor magnitude and phase angle will have to be applied to the read phasors in order to meaningfully compare high and low side currents. This gives rise to the need for the project to perform connection compensation within the relay. Additionally, many power system transformers contain devices called 'load-tap changers' (LTCs) that vary the transformer's turns ratio by a small amount to improve voltage regulation. Protections that operate based on voltage or normalize values between the high and low sides of the transformer should be set to account for possible variation ( $\sim\pm5\%$ ) in the turns ratio.

Fig. 3.4 Delta connection for three coils. By B. Ross

#### 3.1.2 Instrument Transformers

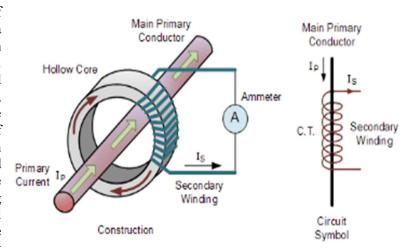

Devices that monitor electrical quantities in power systems face a challenge, namely, the magnitude of the quantities to be measured. 'Instrument Transformers' are often used to linearly step-down current and voltage magnitudes to those more suitable for distribution within an enclosure. Microprocessor devices (e.g., PHATCAT) often require additional internal hardware to further reduce the levels to board-level quantities (e.g. 30A to 10V). The physics of transformers are discussed throughout this paper, so this section

will focus primarily on explaining how they are applied to relate primary power system quantities (e.g. 3000A, 230kV on a 300 MVA power transformer) to those available to devices such as PHATCAT.

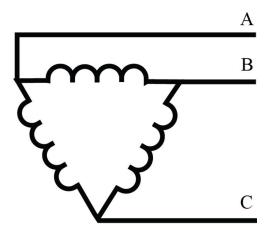

Application of Current Transformers: Current transformers are usually applied as toroids (Fig. 3.5) that slip-over the primary conductor. They are often located within the bushings of circuit breakers (Fig. 3.6) and transformers. Their maximum provided turns ratio is often chosen to carry 5A at the rated ampacity of the rated current. For example, a 3000A nominal circuit breaker would have 3000:5 CTs. These CTs typically come with multiple taps that allow for a selection to be made from several different ratios. Multiple sets of CTs are usually provided within one piece of equipment, for use with different devices where sharing a common connection might constitute a reliability risk. A thermal rating factor (TRF) is given, which gives the

Fig. 3.6. 230kV gas-insulated breaker with bushing mounted CTs. Photo by B. Ross.

nominal thermal rating of the CT as a factor of its secondary ampacity. For instance, a 3000:5 CT with a TRF of 2.0 can carry 10A nominal on its secondary. A TRF greater than 1 is frequently necessary when tapping a CT below its maximum ratio, as the nominal primary side current will then induce a secondary current greater than 5A.

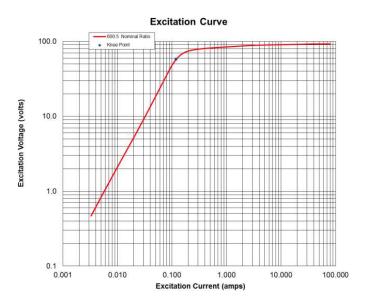

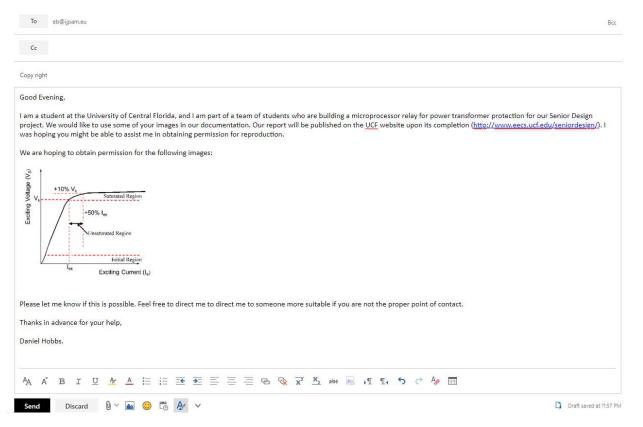

The chief measure of protective CT performance is the location of the CTs 'knee point,' or, where the CT saturates. This can be visualized by looking at a CT's excitation curve (fig 3.7). The excitation voltage, or the voltage at the CT secondary terminals, is given to be a good indicator of how intense the magnetic flux

inside the CTs core is (see Section 3.1.7 -Overexcitation Protection for a derivation). The excitation current, which is the shunt current required to sustain the magnetic circuit, is related to the voltage using this curve. On fig 3.7, the knee point occurs somewhere just after 0.1A. Up until this point, the ratio between excitation voltage and current is linear. In other words, the excitation impedance is constant. At and beyond the knee point, this relation becomes nonlinear and the impedance (the slope of the curve) overall becomes much lower. So, past the knee point, large harmonic content can be expected. Additionally, the excitation impedance will be greatly reduced. The excitation branch forms a parallel path with the relay sensing the CT current, so a reduction in excitation impedance will result in a portion of the current not being measured by the relay. Thus, it is very important that protection CTs do not enter

Fig. 3.7. A typical CT excitation curve. Reproduced with the permission of Voltage Disturbance.

saturation during a large fault current. This is the driver for PHATCAT's requirement that the current sensing circuit have an extremely low input impedance. The higher the burden, the higher the excitation voltage created for a given current, and the higher the excitation voltage, the more likely it is that the CT will saturate.

For CTs used for protective relaying, IEEE C57.13 provides guidelines for classification of CT accuracy. Given in the form CX00, where X is commonly 2, 4, 8, or 12. A C400 CT is accurate for an excitation voltage of 400V where the CT burden is 4 Ohms. The chief physical difference between a C400 and C1200 CT is the size of the iron core. By providing the maximum excitation voltage, this rating provides a measure of the performance of the CT's core that is much easier to work with than one given in Webers. By summing all of the impedances constituting the CT's burden (cable, relay coil, CT winding impedance), the excitation voltage for a given fault current is easily obtainable.

Application of Potential/Voltage Transformers: Potential or Voltage Transformers (PT or VT - the terms are used interchangeably) are usually installed as standalone devices and placed at the ends of runs of bus work or at line terminals. Much like loads, they are connected in shunt. They are designed to draw very little current, though some degree of oil or air cooling is still used. Because they are not subjected to extreme fields during faults the same way CTs are, their application is much simpler. For a given voltage level, the PT ratios are chosen to give secondary-side voltages for relaying, 67V and 115V options are common. Many times, PTs will have two secondary windings and taps for both 67V and 115V will be available on each. Because we want to minimize heating in the PTs and any voltage drop in the control cables, which can be several thousand feet long, and are not sized to the thicker gauges that CT cables are, very little current should be drawn by PHATCATs voltage inputs

One modification of the PT worth mentioning is the capacitively-coupled voltage transformer (Fig. 3.8). The traditional PT (the three-winding transformer in the figure) is supplemented by a capacitive voltage divider. A compensation inductor, L, is added to compensate for the equivalent capacitance of the capacitive divider. At transmission voltage levels, CCVTs become cheaper due to the lower transformer turns ratio required. As such, they are commonly used. However, their frequency response makes them susceptible to damage from high frequency signals. The transients potentially induced by CCVTs is one motivator for the overvoltage protection in PHATCAT.

#### 3.1.3 PROTECTIVE RELAYING CIRCUITRY

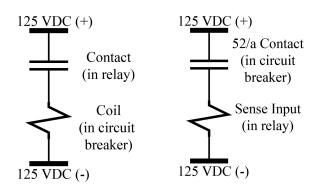

In order to understand some of the design underlying philosophy PHATCAT's functionality, some explanation is due regarding how protective relays are applied in a substation environment. While digital communications are playing an ever-increasing role in protection and controls, much information is still exchanged by opening and closing contacts. These are used to energize or de-energize inputs. Such inputs may be actual loads or coils for actuating electromechanical devices. Alternatively, they may be sense inputs, such as those used in PHATCAT, that simply translate the energized state into a logical '1' in the microprocessor logic

Fig. 3.9. Controlling a circuit breaker with a relay contact. By breaker position with sense B. Ross

Fig. 3.10. Reading circuit input. By B. Ross

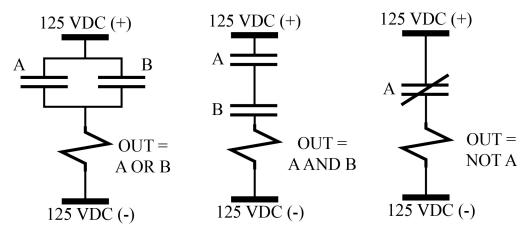

levels. Fig. 3.9 gives an example of one of the most elementary applications of protective relaying circuitry. A contact in a protective relay (e.g., PHATCAT) is connected to the trip coil of a circuit breaker in the substation yard. A DC voltage source is provided, and the contact's position determines whether or not this voltage source energizes the circuit breaker trip coil. In this way, protective relays can have internal logic functions programmed to assert their various output contacts, opening the correct devices and sending informative signals to other relays. Similarly, the protective relays can have internal logic functions programmed to treat their sense inputs as a certain piece of information. One simple and common application of this is the detection of circuit breaker position (Fig 3.10, a '52/a' contact is an auxiliary contact in a power system circuit breaker that mirrors the breaker's position). Because the energized/deenergized state of the sense input follows the 52/a contact position, it effectively acts as a binary logic variable representing circuit breaker position. In fact, such relaying circuits can be thought of in terms of the logical expressions they implement. There are three basic tools: paralleling contacts to 'OR' them, cascading contacts serially to 'AND' them, and using normally-closed (as opposed to normally open) contacts to 'NOT' them (Fig. 3.11).

These basic elements are combined into much more complicated control logics that provide the interactivity desired by the protection and controls engineer. This is why it is key that PHATCAT support user-defined logic – depending on the other devices at the substation and design preferences of the engineer, the role of PHATCATs sense inputs and output contacts will have to be customized.

Fig. 3.11. Basic logic gates with relaying circuitry. By B. Ross

#### 3.1.4 OVERCURRENT PROTECTION

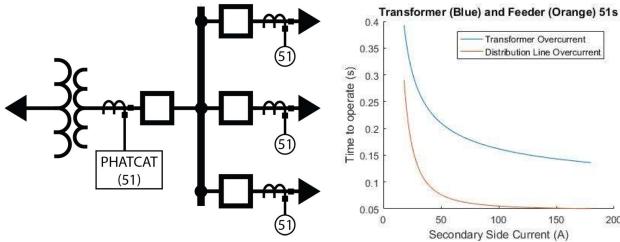

Perhaps the simplest form of protection, overcurrent elements operate based on measured current. Instantaneous overcurrent elements (ANSI code: 50) simply compare the measured current to some preset threshold. A 'definite time' delay, measured in power system cycles, can be added to avoid accidental tripping for quick transients. Instantaneous overcurrent elements are usually set to high thresholds and are used to detect 'close-in' faults. That is, faults that are electrically very close to the measured point. In such situations, it is nearly always desirable that the protection operate as quickly as possible. However, there are many other fault scenarios where a single, instantaneous threshold is unacceptable. In order to preserve its ability to serve its loads, a power system should not remove more components than absolutely necessary to remove the disturbance. Time-inverse overcurrent elements (ANSI code: 51) operate with a time delay that is inversely proportional to the current. This allows for fast tripping for close-in faults but leaves some time delay to allow for protections closer to the fault to clear it. A 51 element's operating time is characterized by the following expression:

$$t_{op} = TD(a + \frac{b}{M^c - 1})$$

The operating time,  $t_{op}$ , is inversely proportional to the ratio, M, of measured current to some chosen pickup current, which is the minimum current for which the element will operate. The time dial (TD) linearly scales the operating time. Coefficients a, b, and c are determined by the curve type chosen, and primarily affect the steepness of the curve. These coefficients are standardized and can be found in the operating manual of

any relay with overcurrent elements. Consider a system where a transformer, protected by the PHATCAT's 51 elements, is to be coordinated with three distribution feeders (Fig 3.12).

The transformer overcurrent will still operate quickly for faults on the bus or distribution lines, but not as quickly as the distribution line protections (Fig. 3.13). Thus, it provides a backup without compromising coordination. 50 and 51 elements can operate on phase, residual, or neutral currents, and are suffixed by 'P', 'G', or 'N' respectively to denote the operating current. The residual current is the calculated sum of the phase currents and can be used in place of the neutral current if a neutral CT is unavailable. Residual and neutral elements are frequently set to be much more sensitive than phase elements, as the power system is mostly balanced during normal operations and sizable ground currents only flow during ground faults.

Fig. 3.12. PHATCAT as 51 on Distribution Transformer. By B. Ross.

Fig. 3.13. Coordinated Overcurrent Settings. Figure produced with Matlab by B. Ross

200

#### 3.1.5 CURRENT DIFFERENTIAL PROTECTION

Current differential elements (ANSI Code 87) utilize Kirchhoff's Current Law to detect unwanted current paths. Current measurements are taken at every branch connected to a protected 'zone.' If the currents do

not sum to zero, there is assumed to be some unwanted current path, i.e., a short circuit. This protection is extremely effective as it not only differentiates between proper operation and short circuit conditions, but it also works within a very clearly defined boundary. For faults external to the zone, the fault current will flow through the zone, but the currents will still sum to zero. For PHATCAT, this intended to be the primary protection.

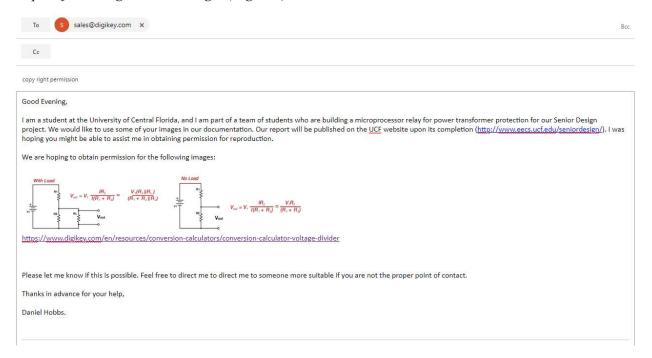

The key to proper application of 87 elements is not the detection of the current difference during an internal fault, this difference is drastically larger than the steadystate value, which should theoretically be zero. Rather, it is mitigating factors that might create a 'falsedifferential'. For instance, an 87 algorithm must normalize currents measured at different voltage levels and remove any phase shifts introduced by transformer connections such as wye-delta. In order to avoid a falsepositive for real-time error sources such as LTC changes, CT error, and noise, a 'restrained' differential

Fig. 3.14. Restrained Differential Element. By B. Ross.

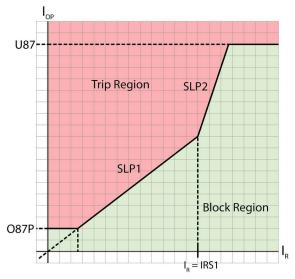

is used (Fig. 3.14). In addition to the phasor sum of the currents ( $I_{OP}$ ), a restraining quantity ( $I_R$ ) is calculated. Its purpose is to estimate the magnitude of overall current flow and, based on the assumption that this is proportional to the error, increase the  $I_{OP}$  required to operate the 87 element. A minimum threshold (O87P) is set along with two slope values (SLP1, SLP2) and a slope intersection point (IRS1). An unrestrained pickup value (U87) can also be set.

Some transformers, such as delta-wye connected, only allow ground fault currents to flow on one side of the transformer. In the delta-connected winding, there is no path to neutral/ground, and any ground currents flowing in the wye-connected winding will remain trapped within the delta winding—they will not be measured by the CTs, which measure the phase current. In order to prevent a false differential for external ground faults, the PHATCAT must remove the zero-sequence current component before performing its restrained differential calculations.

#### 3.1.6 HARMONIC BLOCKING

Harmonic blocking is not used to trip protections, but rather to prevent protections from tripping for false positives. When a transformer is first energized, a large amount of current flows in the excitation branch. At this point, the transformer has not yet started to serve its load, so the through-current in the transformer is nearly zero. So, how is the differential protection to distinguish between an internal transformer fault and transformer energization? Because the excitation impedance of the transformer core is both nonlinear and time-varying during energization, large harmonics are produced. These harmonics are far in excess of what might be produced by a fault. Harmonic blocking simply compares the magnitudes of the second, fourth, and fifth harmonics to the magnitude of the fundamental frequency component. If any of these ratios exceed set percentage thresholds, the differential protection logic is blocked. The third harmonic is not used as there are many other sources of third harmonics in power systems that might cause undesirable blocking. Harmonic blocking also helps prevent false differential operation for other sources of harmonics such as power transformer saturation (overexcitation), CT saturation, and energization of other nearby transformers (e.g., another transformer bank connected in parallel).

#### 3.1.7 Overexcitation Protection

As we've discussed, the excitation branch of a transformer models those losses incurred in the core of the transformer. If these losses are high enough, the core becomes damaged, degrading the transformer's impedance or even destroying it. When the flux within an iron core becomes too intense, it can saturate. During saturation, there are no more magnetic domains within the material that can be aligned to produce more flux. The effect is that of drastically decreasing the excitation branch's impedance, greatly increasing losses. By rearranging Faraday's law of induction, we can establish that this flux is proportional to the system voltage and inversely proportional to the system frequency:

$$EMF = Vsin(\omega t + \phi) = N \frac{d\Phi_B}{dt} = > \Phi_B(t) + \Phi_0 = \frac{1}{N} \int Vsin(\omega t + \phi) dt = \frac{-V}{\omega N} cos(\omega t + \phi)$$

By setting a threshold of  $V/\omega$  to trip for, we effectively set a threshold of magnetic flux. This should be set to a value below the maximum magnetic flux that the core can withstand. PHATCAT will just implement an instantaneous threshold trip, as this proves proper implementation of the protection, but many manufacturers utilize time-inverse characteristics so as to avoid tripping for transient system states that will not persist long enough to harm the core.

If the transformer utilizes an LTC to regulate the voltage, the overexcitation element should be set to operate based on the side of the transformer without the LTC.

#### 3.2 Market offerings

There are many companies that sell microprocessor relays, including GE, ABB, Schweitzer Engineering Laboratories (SEL), Siemens, Beckwith, and Schneider Electric, among others. Two top-of-the-line

transformer protection relays, by one made by SEL and another by Siemens, are examined in detail. While these devices give a good representation of the breadth and depth of functionality available today from all these manufacturers, not all applications require such complex devices. For instance, the older and simpler SEL-587 is still used in new constructions at some utilities. Core protective functions, such as time-inverse overcurrent and restrained current differential, vary little in their behavior between products and vendors, though there are certainly quirks and variances to be observed. The main difference between older and newer microprocessor relays lies mainly in the number of inputs/outputs supported, the number of different functions performed by one device, and the variety and modernity of the communications systems offered.

The primary end-users of these devices are protection engineers at consulting firms, utilities, and businesses with large or specialized power needs. As such, they are marketed in a very technical manner, with an emphasis on features, standards, and numerical values. Vendors also heavily utilize industry conferences as an avenue for marketing. They often publish whitepapers on the proper application of protection functions. When they work with a utility to use their relays in a challenging or unusual application, they often like to publish a paper sharing it. Relay manufacturers also offer a variety of seminars and trainings on power systems topics. All these strategies benefit the industry by sharing knowledge while also helping relay manufacturers share their products, establish rapport with customers, and build their reputation as knowledgeable experts.

Notable features of the two analyzed market offerings will be presented, then a table will be given that compares their quantitative specifications with one another and with PHATCAT.

#### 3.2.1 SCHWEITZER ENGINEERING LABORATORIES: SEL-487E

The SEL-487E (Fig. 3.15) is SEL's newest and most powerful transformer protection relay [3.1]. It supports up to five sets of three-phase winding currents, making it suitable for transformers with more than two sets of windings. It provides all of the protection functions typically used in transformer protection, including current-differential, overcurrent, overexcitation, restricted earth fault, and harmonic blocking. For each function, it supports multiple elements of the same function with different settings. These elements also have 'torque equations'— user-definable logical expressions that control whether or not the element is enabled. SEL touts the relay's ability to be used with a variety of kinds of transformers and in a variety of substation topologies. This is a vital marketing point as every customer has different needs and tested practices; they want to be engineering their equipment to fit their application, not the other way around. SEL also mentions the relay's ability to track breaker operations and through-faults over time. Such data is valuable for equipment owners, power system circuit breakers and transformers are expensive pieces of equipment and must have a long service life to produce value justifying their cost. Circuit breaker operations and external faults put stresses on these components that can increase their maintenance needs and shorten their lifespans. The SEL-487E provides information that asset management entities can use to improve preventative maintenance and repair. Another aspect of the 487E that SEL emphasizes is its flexibility with a wide variety of communications architectures. Some of these are for Supervisory Control and Data Acquisition (SCADA) and others are for relay-to-relay communications. While many utilities have yet to fully utilize all of the benefits modern communications systems can bring, relay manufacturers have been pushing the boundaries forward.

The SEL-487E starts at \$6750 but configuring it to include the fullest of its functionality brings the cost up to a \$10,435. This is mainly driven by the inclusion of additional networking functionality and a larger number of higher-performance I/O.

Fig 3.15. SEL487 relay. Reproduction permission obtained from SEL, inc.

### 3.2.2 SIEMENS: SIPROTEC 7UT87

The 7UT87 is a part of Siemens' SIPROTEC 5 generation of relays (Fig. 3.16). It is the generation's most powerful and robust transformer protection relay. This generation stresses the relays' modular nature [3.2]. All of the relays use the same form factor for their base and allow for horizontal expansion via additional modules. With this modularity, it supports up to 9 sets of three-phase current measuring points. It possesses all of the standard transformer protections, including current differential, restricted earth fault, overcurrent, etc. One interesting protection is that of an impedance protection designed for transformers (21T). Siemens stresses the flexibility of the DIGSI 5 software used to configure the devices. A tremendous variety of functions are included in the relays and the software is used to combine those desired by the user into a custom arrangement of features. Customers then buy a certain number of 'function points', which then determine how many concurrent features they can run. This serves customer needs on a more specific basis by allowing absolute customization, even on a software level. Another feature Siemens highlights is the relays' conformance to cyber security requirements. Such assurances are critical as protection and controls engineers are under close scrutiny as they tackle the potential vulnerabilities introduced by modern communications systems.

Cost data for the 7UT87 was not available online but can be expected to vary significantly depending on the desired function points and expansion modules.

#### 3.2.3 PHATCAT VERSUS MARKET OFFERINGS

With two market offerings related, some highlights can be compared so as to illustrate the ways in which PHATCATs performance has been curtailed from the industry standard so as to comply with the project's realistic design constraints. Note that this list is not exhaustive, there are many useful features included in these devices that it is simply out this project's scope to discuss. Additionally, these represent the maximum capabilities offered for each device. For market offerings, there are several configurations available for customers to strike the right balance between cost, functionality, and form factor.

Table 3.1. Comparison of PHATCAT and market offerings

| Product:                                    | SEL-487E                                                       | SIPROTEC 7UT87                                                                 | PHATCAT (specified)                                 |

|---------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------|

| Measuring Points:                           | 18 Currents, 6 Voltages                                        | 32 Currents, 15 Voltages                                                       | 8 Currents, 6 Voltages                              |

| Measurement Ranges:                         | 91A, 300V                                                      | 500A, 200V                                                                     | 30A, 200V                                           |

| Current Measurement Accuracy <sup>2</sup> : | Magnitude: <u>+</u> 0.2% <u>+</u> 4 mA<br>Phase: <u>+</u> 0.2° | Not given                                                                      | Magnitude: ±5%<br>Phase: ±1°                        |

| Voltage<br>Measurement<br>Accuracy:         | Magnitude: $\pm 0.1\%$<br>Phase: $\pm 0.5^{\circ}$             | Not given                                                                      | Magnitude: ±5%<br>Phase: ±1°                        |

| Current Differential:                       | Restrained, Unrestrained,<br>Negative Sequence                 | Restrained, Unrestrained                                                       | Restrained,<br>Unrestrained                         |

| Harmonic Blocking:                          | 2 <sup>nd</sup> , 4 <sup>th</sup> , 5 <sup>th</sup>            | 2 <sup>nd</sup> , 3 <sup>rd</sup> , 5 <sup>th</sup>                            | 2 <sup>nd</sup> , 4 <sup>th</sup> , 5 <sup>th</sup> |

| Overcurrent:                                | Instantaneous, Time-inverse,<br>Adaptive, Directional          | Instantaneous, Time-inverse, Voltage-Dependent, Directional, Negative Sequence | Instantaneous, Time-<br>inverse                     |

| Volts/Hz:                                   | Instantaneous, Time-inverse                                    | Instantaneous, Time-inverse                                                    | Instantaneous                                       |

| Protection Accuracy <sup>3</sup> :          | $\pm 1\%$ to $\pm 5\% \pm 0.10$ A                              | 2%                                                                             | <u>+</u> 10%                                        |

| Protection Delay <sup>5</sup> :             | 0.5 cycle to 1.75 cycle<br>(8.33ms – 29.17ms)                  | 20-33 ms,                                                                      | 2 cycles (33.3ms)                                   |

| Sense Inputs:                               | Optoisolated, Up to 250 VDC/VAC, <5mA drawn                    | Up to 300VDC, <2.5mA drawn                                                     | Optoisolated, Up to 200VDC, <10 mA drawn            |

| Output<br>Contacts:                         | Standard: Carry 6A, Break 0.3A @ 125VDC, <6ms                  | Standard: Carry 5A, Break 30VA,<br>Close 8 ms                                  | Carry 2A, Break 2A                                  |

|                                             | Hybrid: Carry 6A, Break<br>10A @ 125VDC, <6ms                  | Fast: Carry 5A, Break 30VA,<br>Close 4 ms                                      |                                                     |

|                                             | High-Speed: Carry 6A,<br>Break 10A @ 125VDC,                   | High Speed: Carry 5A, Break 1<br>kVA, Close 0.2 ms                             |                                                     |

|                                             | Pickup 10us,                                                   | Power: Carry 5A, Break 1 kW,<br>Close 16 ms                                    |                                                     |

<sup>&</sup>lt;sup>2</sup> These are only guaranteed for a certain operating range. For exact range, consult manufacturer datasheet.

<sup>&</sup>lt;sup>3</sup> These vary based on the protection type. For exact values for each protection, consult manufacturer datasheet.

| Personnel<br>Interaction: | 12 pushbuttons, 26 LEDs,<br>Display with detailed menus<br>and substation view                                 | Arrows and keypad, Display with<br>detailed menus and substation<br>view, Many LEDs, Physical key<br>access | 6 pushbuttons, 16<br>LEDs, Display listing<br>key quantities |

|---------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Notable<br>Additional     | Restricted Earth Fault,<br>Over/Underpower, Station                                                            | Restricted Earth Fault, Distance protection, Power swing blocking,                                          | Made with love                                               |

| Features:                 | DC Monitoring, Open-Phase<br>Detection, Event Reporting,<br>C61850, Breaker Wear<br>Monitoring, Synchrophasors | Arc protection, Synchrophasors, LTC control, C61850, Event Reporting,                                       |                                                              |

#### 3.3 CORE COMPONENTS AND PARTS SELECTION

In this section, the features required for the hardware and software implementations of project specifications are analyzed, and implementation options are proposed. Pros and Cons are weighed, and decisions are made as to the implementation to be used. Major components, such as the microprocessor, are chosen so that more detailed design can begin. Minor components (e.g. an exact model of diode) are chosen in Section 6 as their required specifications will be dependent on other, more major parts selections.

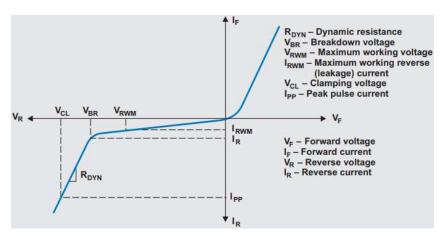

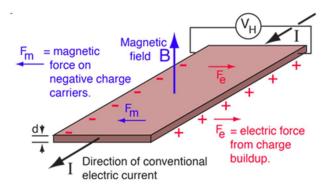

#### 3.3.1 ELECTRONICS PROTECTION