Group Members:

Catherine Donoso Keith Weston Diego Rocha

**Sponsor:** Scott Faulkner, Lockheed Martin

# **Radar Interface Design Project**

University of Central Florida Senior Design I Summer 2009

August 10, 2009

# Table of Contents

| 1 - Introduction                              | 1  |

|-----------------------------------------------|----|

| 1.1 - Executive Summary                       | 1  |

| 1.2 - Motivation                              | 2  |

| 1.3 - Objectives and Goals                    | 2  |

| 1.5 - Specification Overview                  | 3  |

| 2 – System Design Specifications              | 4  |

| 2.1 - 32 V Input                              | 4  |

| 2.2 - Voltage Generation Requirements         | 4  |

| 2.3 - Noise Requirements                      | 4  |

| 2.4 - Thermal Requirements                    | 5  |

| 2.5 – EMI Requirements                        | 5  |

| 2.6. – PCB Layout Constraints                 | 5  |

| 2.7 - RoHS Compliance                         | 6  |

| 3 – Research                                  | 6  |

| 3.1 – Introduction                            | 6  |

| 3.2 – Research Methods                        | 6  |

| 3.3 – Simulation                              | 7  |

| 3.4 – Electro-Magnetic Interference Solutions | 8  |

| 3.5 – Thermal                                 | 11 |

| 3.6 - Communications Protocols                | 12 |

| 3.6.1 – I^2C                                  | 12 |

| 3.6.2 – SPI                                   | 13 |

| 3.6.3 – UART/USART                            | 14 |

| 3.6.4 – 1 Wire                                | 15 |

| 3.7 – Power Architecture                      | 16 |

| 3.7.1 – Linear Voltage Regulator              | 16 |

| 3.7.2 – DC-DC Converter                       | 17 |

| 3.7.2.1 - Paralleling DC/DC Convertors        | 19 |

| 3.7.2.2 - Ripple Attenuation                  | 20 |

| 3.7.2.3 - LTM4607 uModule                     |    |

| 3.7.2.4 - LTM4612 uModule                                     | 20 |

|---------------------------------------------------------------|----|

| 3.7.2.5 - LTM4612 Pins                                        | 26 |

| 3.7.2.6 - LTM4612 Summary                                     | 29 |

| 3.8 - Positive to Negative Voltage Converter                  |    |

| 3.9 - Ripple Attenuator                                       |    |

| 3.10 - PCB Layout and Topology                                | 30 |

| 3.11 – Filtering                                              | 31 |

| 3.12 -Analog to Digital Signals                               |    |

| 3.13 - RoHS Compliant                                         |    |

| 3.14 – Trade Studies                                          |    |

| 4 - Hardware Description                                      | 35 |

| 4.1 - Available Resources                                     | 35 |

| 4.2 - Heat Dissipation Capabilities                           | 35 |

| 4.3 - Power Architecture                                      |    |

| 4.3.1 - Linear Voltage Regulator and DC-DC converter/Switchin |    |

| Supply                                                        | -  |

| 4.3.2 - EMI                                                   | 41 |

| 4.3.2.1 - Noise Simulations                                   | 41 |

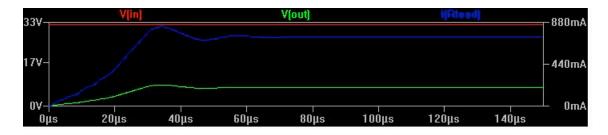

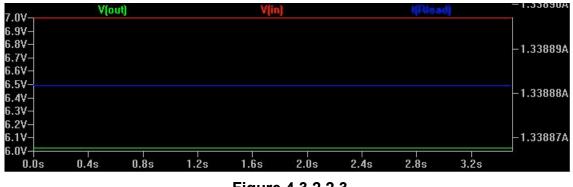

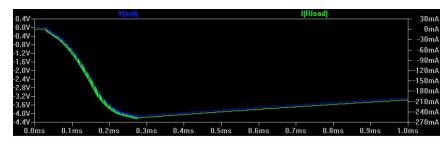

| 4.3.2.2 - Voltage, Current, and Time Response Simulations     | 45 |

| 4.3.3 - Power Sequencing                                      |    |

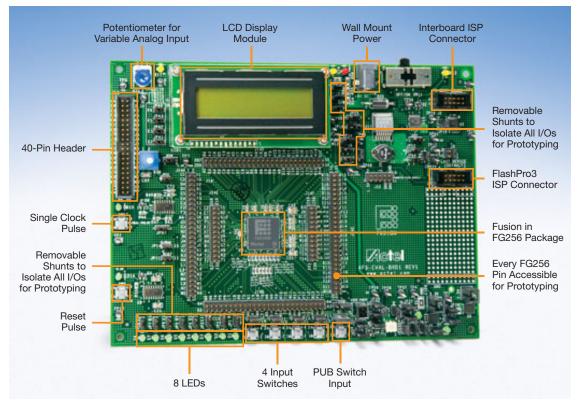

| 4.4- Timing and Control Architecture                          | 51 |

| 4.4.1 - Overview/Selection Process                            | 51 |

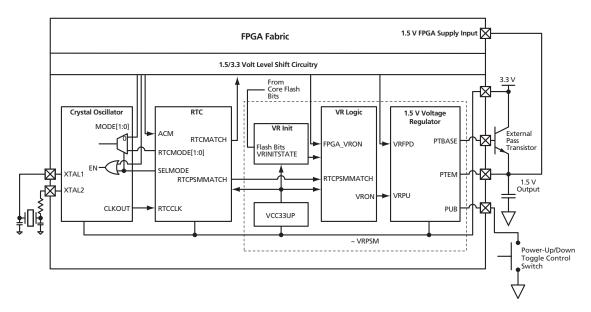

| 4.4.2 - Power                                                 | 53 |

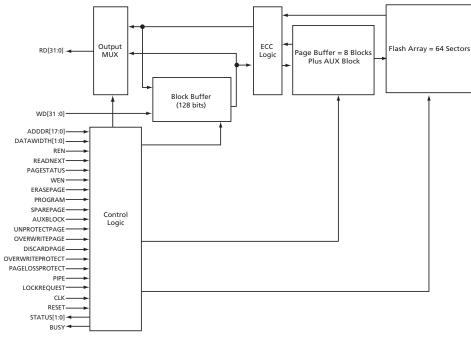

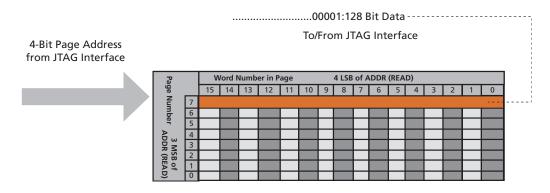

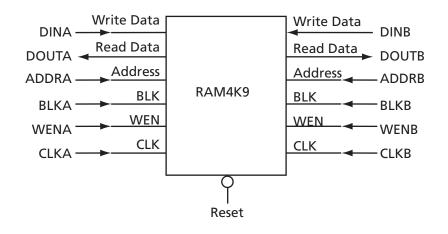

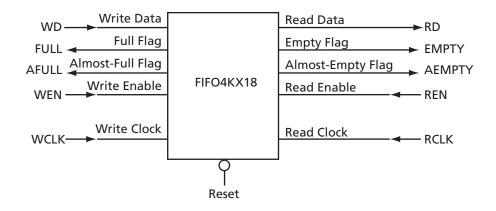

| 4.3.3- Embedded Memory                                        | 54 |

| 4.4.4 - Current Monitoring                                    |    |

| 4.4.5 – Software                                              |    |

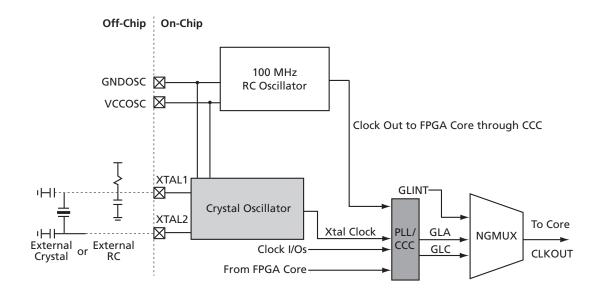

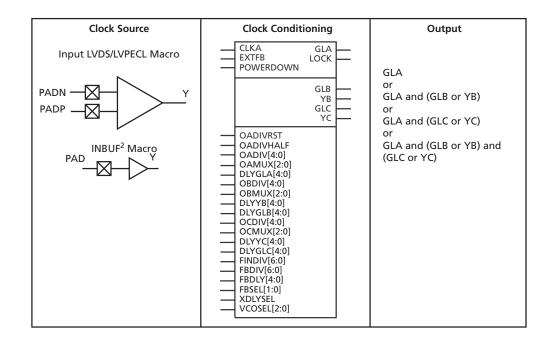

| 4.4.6 - Clock Resources                                       |    |

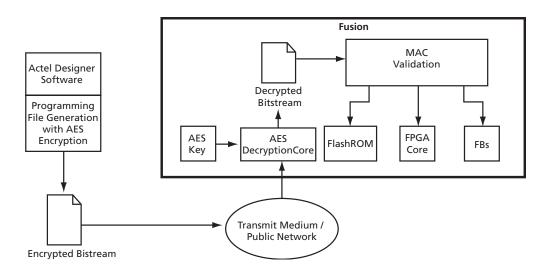

| 4.4.7 - Security                                              |    |

| -                                                             |    |

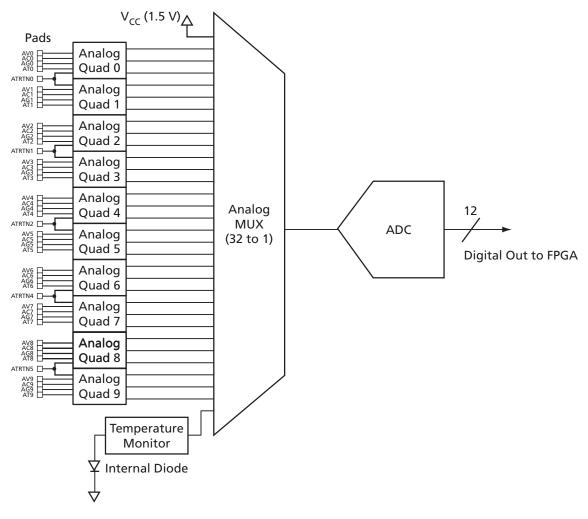

| 4.4.8 - Analog to Digital Converter<br>4.5 Schematics         |    |

| 4.6 - PCB Layout                                              |    |

|                                                               |    |

| 5 - Testing                                                   |    |

| 5.1 – Introduction                                            |    |

| 5.2 – Safe To Turn On Test Plan                               |    |

| 5.3 - 6XMIT Test                                              | 77 |

| 5.3.1 – Test Plan                           | 80 |

|---------------------------------------------|----|

| 5.4 - Low Power Signals Test                | 83 |

| 5.5. Demostration                           | 88 |

| 6 - Facilities                              | 88 |

| 7 - Budget and Milestone Chart              | 88 |

| 7.1 - Budget                                | 88 |

| 7.2 - Milestone Chart                       | 90 |

| 8 - Design Summary                          | 91 |

| 9- Summary of Figures and Summary of Tables | 91 |

| 10 – Appendix                               | A  |

| 10.1 - Works Cited                          | A  |

| 10.2 - Permissions                          | C  |

# 1 - Introduction

#### **1.1 Executive Summary**

Lockheed Martin is one of the primary defense contractors for the United States military and to the National Aeronautics and Space Administration, and contractor to many other militaries around the world. Lockheed Martin Missiles and Fire Control in Orlando, Florida is sponsoring the project. The plant concentrates on radar development and weapon defense. Currently, one of the main programs at this facility is Joint Air to Ground Missile, or JAGM. The missile will serve as the next generation missile to the U.S. Army, U.S. Navy, and U.S. Marine Corps. It will replace the HELLFIRE missile and Longbow HELLFIRE missile now used on the Apache attack helicopter, and also missiles on the F/A18 Hornet, the Apraho reconnaissance helicopter, the Super Cobra attack helicopter, the Seahawk reconnaissance helicopter, and the Warrior unmanned aerial vehicle. It may also be used on the F-35 Lightning II platform. The JAGM missile has a tri-mode seeker, which will enable it to have far reaching limitations. The seeker is equipped with a semi-active laser, infrared imaging, and millimeter wave radar making it versatile and an all-weather capable missile.

JAGM needs a next generation power supply for the transceiver of this missile. The circuit board must convert the power source voltage and convert it to multiple voltages for the transceiver. The circuit board must also have a timing control unit that will do power up sequence and power down sequence, as well as monitoring the temperature. Timing signals are expected to be highly accurate and reliable. One of the main challenges of this particular project is the limited circuit board space and limited airflow in the system. This is a particular challenge because there must be low heat dissipation from the board. Low heat parts and proper package will have to be considered. Electromagnetic interference (EMI) must be kept to a minimum to insure optimal performance of missile guidance and tracking systems. The power supply needs to be clean, contiguous, and responsive.

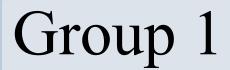

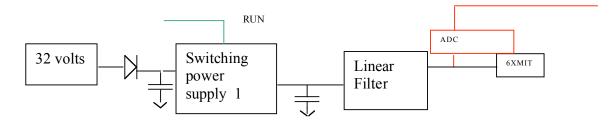

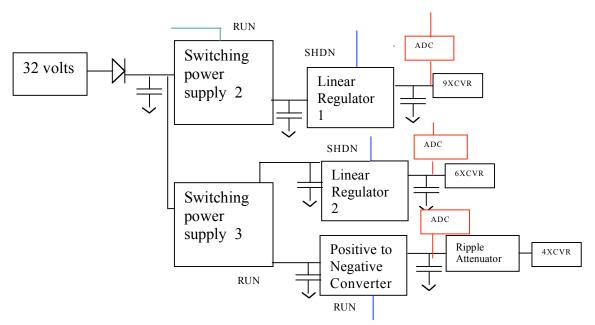

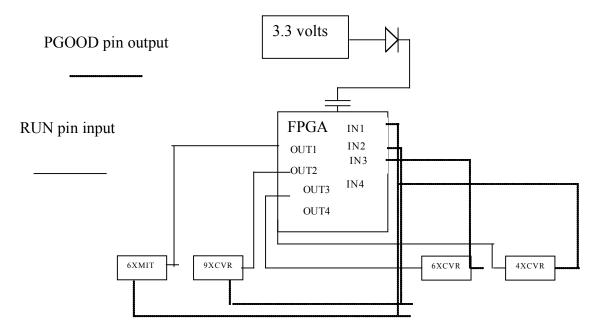

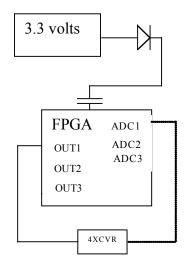

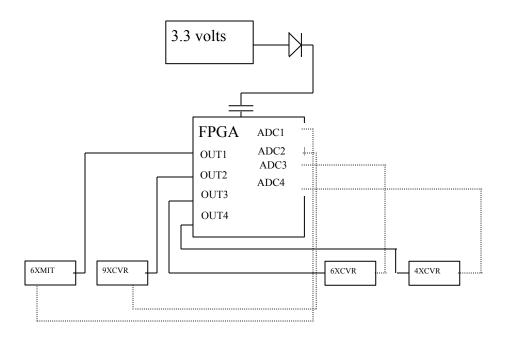

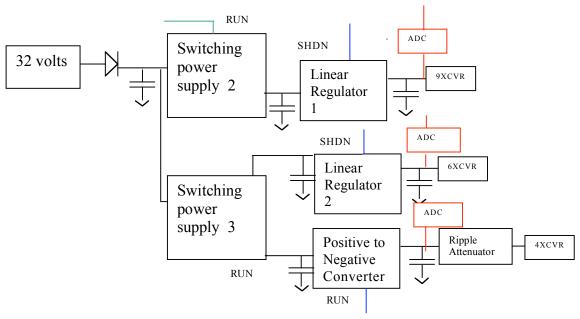

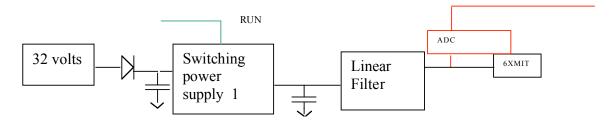

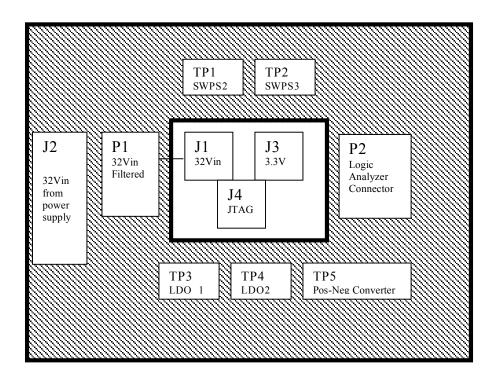

The following diagram, Figure 1, is a basic block diagram of the power supply system. In more detail of the system, 32 volts is the only voltage source to the power supply system. The 32 volts must be used to power everything in the circuit and will also be converted into high power and low power voltages. The voltages that will be created from 32 volts is +6V high power, -4 volts, +6 volts low power, and 9 volts. These voltages that need to be generated will be used for a separate circuit board. However, this circuit board will not be considered in this design. The control unit will monitor the output voltages and output currents of specific voltage converters, it will control when the voltage converters are turned on and off, and it will monitor the temperature from a specified temperature sensor in the system.

Figure 1.1.1 Block Diagram of system

#### 1.2 Motivation

As engineers, we strive to improve people's lives. The team members of this project want to accomplish this very aspect. The motivation of the project is to design a more useful power supply for the transceiver. A fully functioning transceiver with reliability contributes to a more reliable seeker. The missile itself becomes more reliable because of the seeker. This is like dominoes falling in line. One thing affects the other. Pilots need the reassurance that they are carrying missiles that will save their lives in combat and help them succeed in their mission.

#### 1.3 Objectives & Goals

The JAGM (Joint Air to Ground Missile) is to be a replacement to the Hellfire II, Longbow HellFire missile, and Maverick missiles in current use on many platforms throughout the United States Armed Forces and our Allies. Current platforms include the US Army Apache Helicopter, US Marine Corps Super Cobra, and the US Navy's Seahawk armed reconnaissance helicopter. JAGM could also replace the Maverick missile aboard the US Navy's FA-18 Hornet.

The goal of our project is to create a circuit card that provides sufficient voltage and current required to drive the transceiver subsystem assembly of the missile and provide the appropriate timing and control architecture to implement a power sequence and monitor these voltages. The timing and control architecture's primary responsibility will be to monitor and power sequence the voltages to their subsequent subsystems. Parameters to the problems we will face include extreme temperatures, EMI, thermal constraints and very precise DC voltages with low ripple. With this multi-platform and multi-environment situation we were tasked to provide a circuit card that could work in harsh environments. This would require us to procure parts that could handle extreme temperature and stress. These parts are generally considered military grade electronics. The fact that the missile the circuit card is going in will possibly be flying at high altitudes where temperatures could exceed -40 degree Celsius and were factors we needed to keep in mind during selection of parts.

The heart of the timing and control architecture subsection will be controlled using some sort of a programmable logic device, such as a CPLD (Complex Programmable Logic Device), Micro-Controller, or Field Programmable Gate Array (FPGA). This device will accept control signals from an external FPGA and provide the appropriate action required. Over this command bus the timing and control architecture will provide status updates on the voltages and current we are monitoring, temperature in the transceiver monitored by the AD590 temperature sensor, and provide power sequencing status updates. This two way communication will require the design of a serial or parallel communication bus with an external clock source that will be provided.

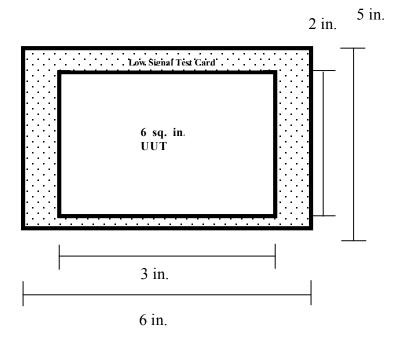

The printed circuit board design will be a challenge in itself. The entire power architecture and timing control unit must all fit onto a single board that has an area of 6 square inches. This specification requires us to select the smallest and most energy efficient parts that we can find. Due to the lack of space these constraints will elevate thermal and EMI problems. Therefore, the group will have the challenge in designing a PCB and selecting parts to alleviate such problems.

#### **1.5 Specification Overview**

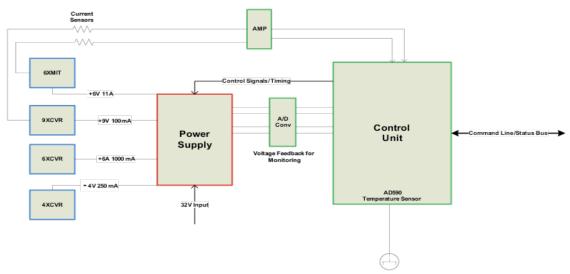

Lockheed Martin is designing a new radar interface. The RF Engineers of XYZ Corporation have completed their design of the RF components in a new radar transceiver. The rest of the design has been assigned to us. The power supply architecture for the radar transceiver has to be designed in a printed circuit board with an area no greater than 6 inches. The power supply along with its timing and control architecture will receive an input voltage of +32 V. The input voltage has to be processed into different output voltages as required by the radar transceiver. The 6XMIT is used to drive the transceiver. It has to supply a load for durations of 1 to 100  $\mu$ S and shall not exceed 50% duty cycle. The other voltages supply power to continuous loads. In addition, the output voltages have to follow a power sequence. The 4XCVR must be powered first, then +6, then +9, and laslty the +6 VDC. Upon a system failure or shutting down the system the power down sequence is reversed by turning off the 6XMIT first and then following the same order in a reversed manner. Figure 1.5.1 summarizes the power sequence.

Figure 1.5.1 Power Sequence Summary

# 2 - System Design Considerations

# 2.1 32 V Input

32 volts (32Vin) will be provided to power the system. The 32Vin will only have a voltage ripple of 100uV. The 32Vin is used to generate voltages that the specifications mention. 3.3 volts (3.3Vin) will also be provided to supply operating power to the FPGA. This voltage will not need to be filtered.

# 2.2 Voltage Generation Requirements

Four voltages must be generated in a specific sequence. There is one high power signal to be generated. Then three low power signals that must be generated. The high power signal has more tolerance for ripple voltage than the low power signals. The four output voltages that the radar transceiver needs are as follows in Table 2.2.1. The table includes the necessary output current, regulation, and ripple voltage.

| Signal | Output<br>Voltage | Output<br>Current | Regulation | Ripple<br>Voltage |

|--------|-------------------|-------------------|------------|-------------------|

| 6XMIT  | 6VDC              | 11 A              | 3%         | 1mV               |

| 9XCVR  | +9VDC             | 100mA             | 3%         | 100uV             |

| 6XCVR  | +6VDC             | 1000mA            | 3%         | 100uV             |

| 4XCVR  | -4VDC             | 250mA             | 3%         | 100uV             |

#### Table 2.2.1 Voltage Generation Requirements

# 2.3 Noise Requirements

Noise is the unwanted part of an electrical signal. It is created by electrical interferences by other devices in a circuit or by electrical interferences external to the system coming from the environment. It is a nuisance because it interferes with accuracy. Voltage ripple is a result of noise. Some systems may need to be more accurate than others and voltage ripple is a major factor to consider a particular device and whether it is appropriate for that particular circuit design. The input power will have 100uV ripple voltage. The low power output signals must have only 100uV ripple voltage. However, the high power output power can be 10mV ripple voltage. The power supply must output clean voltages to the transceiver.

#### 2.4 Thermal Requirements

The radar transceiver is mounted on gimbal with only convection cooling of approximately 3 watts and heat sink available to control temperature. The heat sink is aluminum with 5 inch diameter and 0.35 inch thickness. Due to the lack of cooling means, the heat generated in the conversion of +32 V to other voltages must be minimized to maximize the operation time of the radar transceiver. The goal is to operate the radar transceiver in 7 minutes intervals between power downs for cool off. In order to meet these requirements, DC to DC convertors have to be implemented to obtain efficiencies above 90 %. Operating temperature range called by the customer is -55 degrees Celsius to +85 degrees Celsius.

#### 2.5 EMI Requirements

The EMI requirement is to use the devices with the lowest EMI rating. EMI is the generation of unwanted frequencies from nearby devices or equipment. EMI can come from the switching of any device. Digital devices can be extremely noisy because of the internal switching. EMI is especially critical in the design of the power supply because it cannot affect the transceiver. The transceiver's efficiency can be affected by the frequencies generated from the power supply. Even the harmonics from the generated frequencies can affect the operation of the transceiver.

#### 2.6 PCB Layout Constraints

One of the limiting factors of the topology is the area is only 6 square inches. The height of the parts mounted on the board has negligible clearance. Any part should fit in the space allotted for the board in the seeker. The circuit board may be any shape. Parts may be mounted on both sides of the board or just one side of the board. The only constraint is that the parts chosen for the design only take 6 square inches of real-state on the board. There are no constraints on how or where the board must be manufactured. There is unlimited amount of layers allowed in the PCB design.

#### 2.7 RoHS Compliance

It is preferable to acquire parts that are non-RoHS compliant. If it is necessary to purchase RoHS compliant parts because of availability, then the pins must be coated with lead. Also, it is imperative that the part not be made mostly with tin. Parts used in the design must be rugged, and if the part is RoHS compliant it will degrade more quickly.

# 3 - Research

# 3.1 Introduction

Proper research for this project is vital to achieve the task of completing a functioning design. The project will require the team members involved to learn about new topics that have not been taught in the undergraduate program. Most of the material that the members of the group will deal with in this project is considered 'graduate level' material. In order to gain a better understanding of the overall picture, Scott Faulkner, the sponsor of the project will meet with the group every two weeks in order to keep the group in the right track. The project will be split into three parts; each member will get a section of the project. Extensive research on the assigned topic will be done by the members of the group and at the end of the first semester a design will be proposed based on the research done by the group. It is believed that the main challenge of this project without overheating the components and keeping the electromagnetic interference levels extremely low so that other components in the circuit are not affected by it.

# 3.2 Research Methods

At first the group consisted of four EE students. Upon reading the guidelines of the project given to the group by Lockheed Martin, it was decided that the initial research would be equally divided among the group members since all members have gone through the same pre-engineering classes. During the second week, specific topics were chosen by each group member based on interest of the topic. The power supply architecture and hardware design was split between Catherine Donoso and Diego Rocha. The timing and control architecture was split between Josef Von Niederhausern and Keith Weston. For the first two months, each member searched for numerous resources that could be used to meet the design goals given to the group. The group focused mainly on the data-sheets of well known companies such as Linear Technology, Texas Instruments, and Xilinx. During that period, the group met twice a week to discuss the progress of the team as a whole and to set goals such as having a certain amount of information for the next meeting. In addition, the group met

with the sponsor of the project, Scott Faulkner every two weeks to discuss questions. A month before the first phase of the project had to be finished; Josef Von Niederhausern dropped the class because of personal conflicts. His part of the project was divided equally among the rest of the members of the group. As of right now, the group is finishing the design; the prototype will be built next semester.

#### 3.3 Simulation

Simulation is a powerful tool for analyzing, designing, and operating complex systems. It enables the designer to test the prototype and debug it before actually building it. Additionally, a proper modeling of the system will prove to some extent that the prototype design will function properly and will give the designer a better insight of how the components operate within the system. In general, the advantages of simulating circuits are the following:

- Predict results and verify equations provided by manufacturer.

- Understand why observed events occur.

- Identify and solve problems before building prototype.

- Explore new ideas and verify its impact on the circuit.

- Communicate the integrity of the prototype.

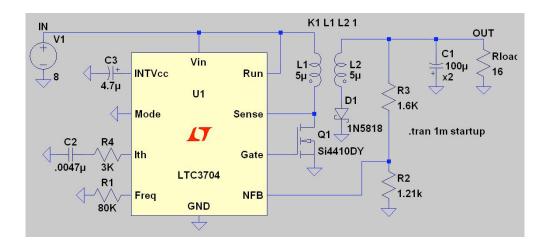

Several fancy programs for circuit simulations are available in the industry. However; most of them are very expensive and therefore it is almost impossible for students to get a hold of them. Ironically, major manufacturers have started developing spice programs that simulate their products and even go a step further as to build the circuit that the designer needs to implement as is the case with Texas Instruments. So in order to simplify the design process, all the components for the power supply were chosen from one manufacturer and that is Linear Technology. Upon weeks of doing research, it was found that Linear Technology provided the components needed to complete the design. Consequently, Linear Technology provides a spice program for simulation purpose called LTspice. As a result, all the simulations in this document were done in LTspice.

LTspice is another spice program in the market that is provided for free by Linear Technology. The program allows measurements of currents and voltages that are "virtually impossible to do any other way" according to the designer at Linear technology. The success of these analog circuit simulators has made circuit simulation spread to board level circuit design. It is easier in many cases to simulate rather than breadboard, and the ability to analyze the circuit in the simulation for performance and problems speeds the design of well understood robust circuits.

There are currently approximately fifteen hundred Linear Technology products according to the Linear Technology website. The program includes

demonstration files that allow the designer to watch step-load response, start-up and transient behavior on a cycle by cycle basis. Included with the spice is a full featured schematic entry program for entering new circuits. Further, spectrum analysis can also be done in the software. This facilitates meeting the noise requirements given to the designer.

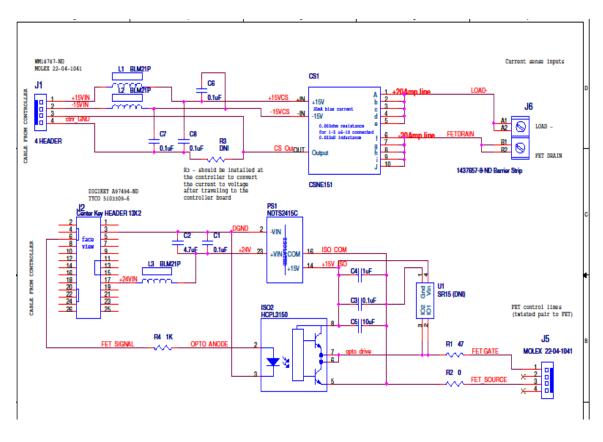

#### 3.4 Electro-Magnetic Interference Solutions

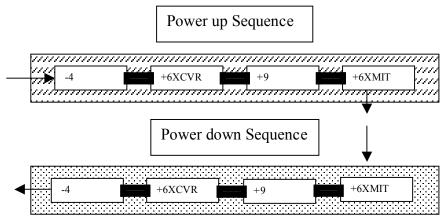

Electro-Magnetic Interference or EMI emissions come out of equipment or components and affect the performance of the circuitry. The two types of EMI are radiated and conductive EMI. Radiated EMI occurs when two components that are separated by space with no hard wire connection somehow end up being connected through a path provided by radiated noise. On the other hand, conductive EMI results when two components that are not supposed to be connected end up with a connection through wire paths within the circuit. Incidentally, both types of noise can exist at the same time. The figure below illustrates both radiated and conductive noise.

ElectroMagnetic Interference Situation

Figure 3.4.1 Shows unwanted coupling paths through radiated and conducted EMI

As mentioned before, one the disadvantages of using dc/dc in power supplies is that they introduce noise in the system. When any element switches logic from two reference voltages, it generates current spikes that produce a voltage transient. This introduces conducted noise in the system which can be eliminated using filters. Radiated noise in a dc/dc buck topology comes out of the magnetic field in the inductor. One way to suppress the radiated noise is by shielding the source of noise, and grounding the element that is acting as a shield. All these different solutions add more size to the area in which all the components will be mounted, and since the area given in the specs is limited only to six inches squared, minimizing the size of the components is critical.

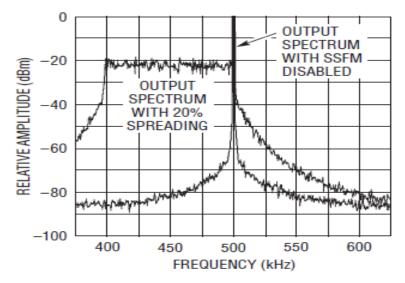

LTI4612 belongs to the µModule family of the Linear Technology dc/dc modules. One of the main features of the LTI4612 is that it is an "ultra-low-noise" module. The designers at Linear Technology have taken all the required measurements to minimize the radiated and conducted EMI caused by the device. Low pass filters are incorporated in the module thereby reducing the conducted noise and the inductor is also inside the package as opposed to the LTM4607 where the inductor is outside the package which results in a potential source of radiated EMI. Furthermore the LTM4607 can also be driven by an external clock. This adds a great advantage in reducing noise because a clock that spreads the spectrum such as the LTC6908-1 can be used. The idea behind using a spread spectrum technique to reduce EMI is to keep the clock moving. Thus the energy released by the device does not have a strong signal at a fixed frequency; instead the energy is spread out randomly within a certain range of frequencies with less intensity. The figure below is a clear example of what happens in the frequency domain when the spectrum is spread and when it is not.

Figure 3.4.2 Frequency spectrum of clock with and without spread spectrum.

Previously it was determined that special care must be taken when paralleling two sources and that the simplest solution to this problem is to find a dc-dc module that addresses the issue. Linear Technology offers what they call the "µModule power supply solutions." They have developed eight dc/dc µModule families to address specific power requirements. The LTM4607 is one of the eight modules of the µModule family. It is a high power surface mount buck/ boost package that can handle up to 10A in continuous mode. There is also the LTM4605 which offers an output current of up to 12A; this will indeed solve the problem of having to parallel two chips to get more power. However, there is a

problem with the LTM4605 which is that it can only take an input voltage ranging from 4.5V to 20V and since the voltage provided to the system is 32V, the LTM4605 will not work unless the input voltage is dropped. As opposed to the LTM4605, the LTM4607 input voltage ranges from 4.5V to 36V which meets the input voltage requirement. The only issue with this module is that it can only output a maximum current of 10A and hence paralleling the modules becomes the only solution to get the current needed. Since the first requirement every time two sources are paralleled is to have the same output voltage, the dc/dc module has to be set up to meet this requirement. This is done by programming the output voltage through the internal PWM controller of the LTM4607. Adding a resistor from the Vfb pin to the SGND pin programs the output voltage. The following equation determines the output voltage:

Vout = (0.8) \* [(100k + Rfb) / (Rfb)]

where Rfb is the resistor across the VFB pin to the SGND pin, see Figure 3.4.3 for pins reference.

The table, Table 3.4.1, below shows the resistance value to get a desired output voltage.

| Rfb Re | esistor (0 | ).5%) vs ( | Output Vo | oltage |       |       |      |

|--------|------------|------------|-----------|--------|-------|-------|------|

| Vout   | 0.8V       | 1.5V       | 2.5V      | 3.3V   | 5V    | 6V    | 8V   |

| Rfb    | Open       | 115k       | 47.5k     | 32.4k  | 19.1k | 15.4k | 11k  |

| Vout   | 9V         | 10V        | 12V       | 15V    | 16V   | 20V   | 24V  |

| Rfb    | 9.76k      | 8.66k      | 7.15k     | 5.62k  | 5.23k | 4.12k | 3.4k |

Table 3.4.1 look up table to set up the output voltage for the LTM4607.

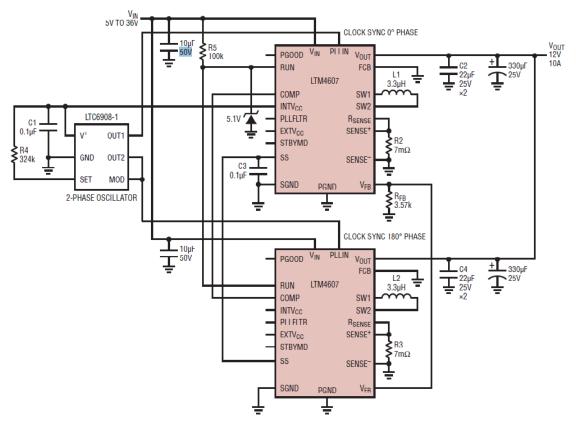

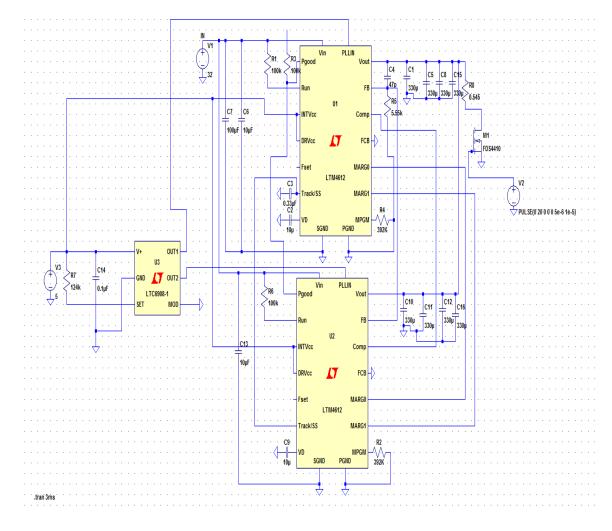

Once the two voltages have the same magnitude then they are ready to be paralleled. Linear technology uses a poly-phase parallel configuration. The purpose of the configuration is to reduce the output voltage ripple. This is achieved by running an external clock signal that connects to the PLLIN pin of each module with one of the clocks being shifted by 180° electrical degrees. The figure below, Figure 3.4.3, shows the poly-phase configuration.

Figure 3.4.3 LTM4607 in Parallel

The schematic above from Linear Technology shows two LTM4607 µmodules connected in parallel. The 2-phase oscillator sends two clock signals that are 180° electrical degrees at a rate of 400 kHz. This is also known as the polyphase or interleaved switch operation, which lowers the output voltage ripple by a theoretical value of two.

#### 3.5 Thermal

Thermal considerations must be taken into account in any design. The temperature will affect the performance of the system and even may prevent the system from operating if it is not running under necessary temperature ranges. The ambient temperature and junction-to-ambient temperature are measured for each part on a circuit board. The ambient temperature is the temperature of the air around the system when the part is operating, while the junction-to-ambient temperature is the temperature of the silicon die in the part. The ambient temperature is dependent on the PCB layout. The junction-to-ambient temperature is a constant given by the manufacturer of the part multiplied by the dissipated heat of the part. It is measured in degrees Celsius per watt. The temperature of the part is then the ambient temperature added to the calculated junction-to-ambient temperature.

#### **3.6 Communication Protocols**

Our project requires a serial communication interface in order to receive and send command and control information to and from the main system. We looked at several serial interfaces. We were given the general specification of how they have accomplished this in previous versions of the missile. This included a generic serial bus using three wires sending a 24 bit address, 8 bits for addressing and 16 bits of data.

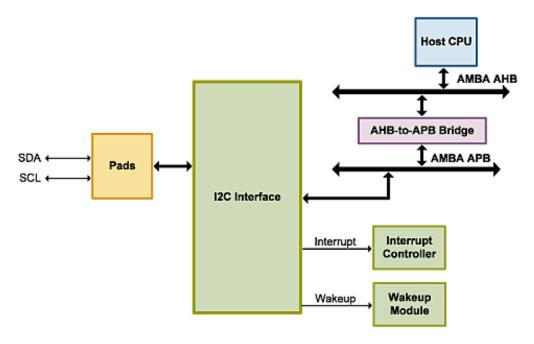

#### **3.6.1** I<sup>2</sup>C

I<sup>2</sup>C is an acronym for Inter Integrated Circuit bus. The bus physically consists of 2 active wires and a ground connection. The I<sup>2</sup>C bus was developed by Philips Semiconductor in the early 1980's to maximize hardware efficiency and circuit simplicity. See Figure 2 below. The I<sup>2</sup>C interface is simply a master/slave type interface. Simplicity in the I<sup>2</sup>C system is primarily due to the bidirectional two wire design, a serial data line (SDA) and serial clock line (SCL). Bi-directional communication is possible through the use of wire (the lines are either passive high or active-low). The I<sup>2</sup>C BUS protocol also allows collision detection, clock synchronization and hand-shaking for multi-master systems. The clock is always generated by the master, but the slave may hold it low to generate a wait state. In most systems the microcontroller is the master and the external peripheral devices are slaves.

Figure 3.6.1.1: I2C Block Diagram

The active wires, SDA (Serial Data line) and SCL (Serial CLock line), are both bidirectional.The key advantage of this interface is that the SDA and SCL lines are the only two lines required for full duplexed communication between multiple devices and the interface runs at a fairly low speed (100kHz to 400kHz). With I<sup>2</sup>C, each component on the bus has a unique address. Chips can act as a receiver and/or transmitter depending on their functionality.

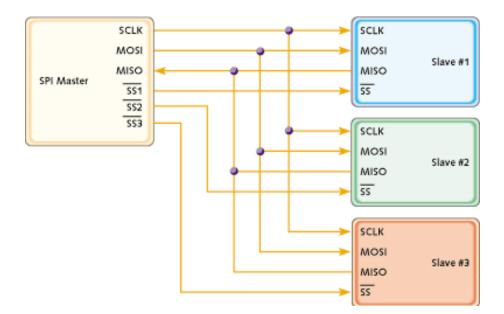

### 3.6.2 SPI

SPI (Serial Peripheral Interface) is a serial bus standard established by Motorola. Devices communicate using a master/slave relationship, in which the master initiates the data frame. Unlike the I<sup>2</sup>C interface SPI has a lack of built-in device addressing so it requires more hardware resources than I<sup>2</sup>C when there is more than one slave. SPI tends to be much simpler when only a single master slave relationship exists. Unlike I<sup>2</sup>C SPI uses four signals and hence four wires. These signals are the following:

- Serial Clock (SCLK)

- MOSI/SIMO (Master Output, Slave Input )

- MISO/SOMI (Master Input, Slave Output)

- (ÇSS) slave select

As shown in the figure below, the SCLK line is the clock line, the clock is generated by the master and drives the communication in both directions, and this line is an input to all slaves. The MOSI line is the master data output, slave data input, and it carries data from the master to the slave. The MISO line is the master data input, slave data output, and it carries data from the slave to the slave. Finally the SS or sometimes known as the CS line is the slave select or chip select line, it is toggled to select a slave to communicate.

Figure 3.6.2.1 Master to slave communication

Having four wires, while not completely undesirable, does have its drawbacks in the area of space requirement. Since size is probably our most limiting requirement we decided to look for other solutions that have the least amount of wires for the desired affect. While wire size is not the only limiting factor, it is of course one, that cannot be overlooked.

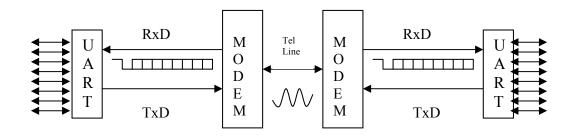

#### 3.6.3 UART(universal asynchronous receiver/transmitter)

This protocol (see Figure 3.6.3.1 below) is either a synchronous USART or asynchronous serial transmission (UART). In synchronous mode it is required that the sender and receiver share a clock with one another, or that the sender provide some other timing signal to the receiver for the next bit of the data. The downside of this synchronous communication is that it can require extra wiring or circuits to share the clock signal between the sender and receiver. In most forms of serial synchronous communication, if there is no data available at the time of transmit, blank characters must be sent so that data is always being transmitted. This is where synchronous communication is usually more efficient because only data bits are transmitted between sender and receiver.

Figure 3.6.3.1 UART to Modem (PENDING PERMISSION FROM ACTEL)

In asynchronous mode the sender and receiver must agree on timing parameters in advance. To do this extra bits must be added to each word which are then used to synchronize the sending and receiving units. When a word is given to the UART for Asynchronous transmissions, a start bit is added to the beginning of each word that is to be transmitted. This start bit is used to alert the receiver that a word of data is about to be sent, and to force the clock in the receiver into synchronization with the clock in the transmitter. These two clocks must be accurate enough to not have the frequency drift by more than 10% during the transmission of the remaining bits in the word. After the Start Bit, the individual bits of the word of data are sent, with the least significant bit (LSB) being sent first. Each bit in the transmission is transmitted for exactly the same amount of time as all of the other bits, and the receiver "looks" at the wire at approximately halfway through the period assigned to each bit to determine if the bit is a 1 or a 0. After the entire data word has been sent the transmitter may add a parity bit that the transmitter generates. The parity it can be used by the receiver to perform error checking. Then a stop bit is sent by the transmitter.

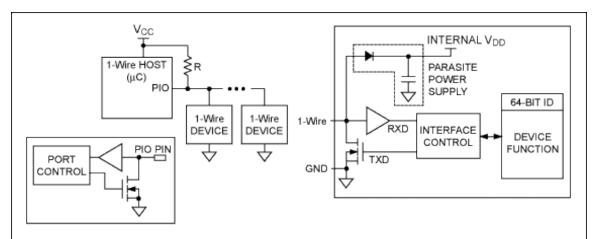

#### 3.6.4 1-Wire

The Maxim 1-Wire interface is a simple communication and device power delivery scheme that multiplexes both device signaling and power on an interface consisting of a single contact and ground return. The basis of 1-Wire technology is a serial protocol using a single data line plus ground reference for communication. 1-Wire is the only voltage-based digital system that works with two contacts, data and ground, for half-duplex bidirectional communication. A typical 1-Wire configuration will contain a single master and one or more slave devices sharing a common 1-Wire line. Communication is half-duplex and always controlled by the master.

Benefits of the 1-wire interface are the following:

- Single Contact Sufficient for Control and Operation

- Unique ID Factory-Lasered in Each Device

- Power Derived from Signal Bus ("Parasitically Powered")

- Multi-drop Capable: Supports Multiple Devices on Single Line

- Exceptional ESD Performance

Figure 3.6.4.1 Internal 1-Wire (PERMISSION PENDING FROM MAXIM)

A 1-Wire master initiates the communication with one or more 1-Wire slave devices on the 1-Wire bus. Each 1-Wire slave device has a unique, unalterable, factory-programmed, 64-bit identification, which serves as it's device address. An 8-bit family code, which is a subset of the 64-bit ID, identifies the device type and functionality. 1-Wire slave devices operate in two different modes:

Parasitic Mode:

• The slave device operates directly off off the power from the bus. Normal

They draw off of a voltage input ranging from 2.8V-5.25V

# 3.7 Power Architecture

#### 3.7.1 Linear Voltage Regulator

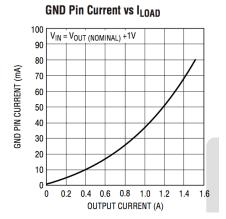

Linear regulator is another type of power supply, but this type usually handles lower voltages because it generates heat and can only step-down voltage. A linear regulator uses either a bipolar transistor or MOSFET, to convert the voltage. The bipolar transistor or MOSFET generates the heat because they effectively act as resistors. It is only 35 to 65 percent efficient. However, they do not create significant noise. Linear regulators have a time delay in which to respond to the change in load current. There are three different types of linear regulators. They are the low dropout regulator (LDO), standard regulator, and quasi LDO regulator. One of the main differences between them is the drop out voltage. The higher the dropout voltage the more power the regulator dissipates, and this creates a heat issue. The standard regulator has the largest dropout voltage making it the least efficient. However, the LDO regulator has the lowest dropout voltage, which makes it the most efficient. The second main factor is the ground current. The ground current is supplied by the source, but is not used on the load. The current is unused and, therefore, 'wasted'. In this case, the standard regulator is more efficient because it has the lowest ground current.

#### 3.7.2 DC-DC Converter

The switching power supply is one type of power supply. The power supply is usually used for higher voltages when considering low heat dissipation. The uniqueness of the power supply is that it used a transformer to step-down or step-up the voltage. It is quite efficient ranging from 65 to 95 percent. The signal is then converted to a DC signal to output. However, a great disadvantage is the RFI noise that it causes because of the high frequency switching in the transformer. Topology is an important consideration when using this type of power supply. Generally, if the switching power supply needs to handle over 40 volts there is a specific topology that must used to safety precaution. Considerations in topology also include, multiple outputs, voltage stress, and current stress. The PCB layout is also fundamental consideration in the design of the board. Traces can behave as inductors and resistors. If a trace is long and there are continuous changes in current, high voltages can be created. Also, the width of the traces must be considered. If the traces are too narrow, a high voltage drop can occur because current cannot flow as readily creating the affect of an antenna and, thus, introducing unnecessary noise.

The objective of the design is to process a raw input power into a conditioned output power. In the process, a device has to be utilized so that the flow of energy between the source and the load has very little resistance. A century ago, a resistive element would have been used in order to get a desired voltage. Consequently, the energy dissipated across the resistor would have been the squared of the current flowing through the resistor times its resistance, thus resulting in a very inefficient system. With the development of semiconductors, a new industry, power electronics, has emerged in which power transfer between a source and a load with a conditioned output power is possible. Power electronics takes advantage of passive and active components to make power transfer between two points as efficient as possible.

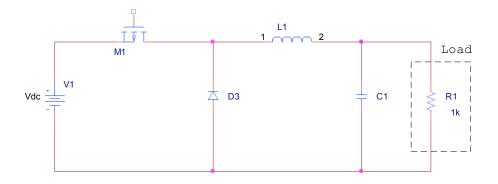

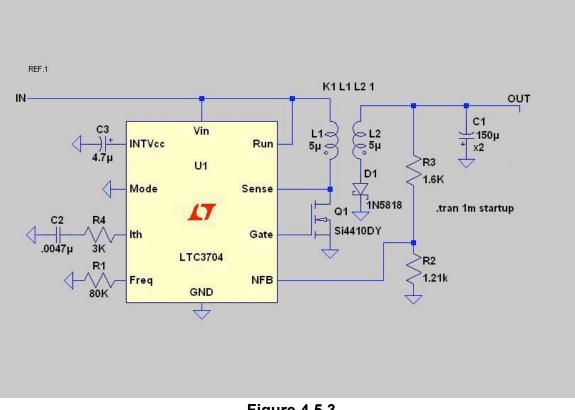

A DC/DC converter is a system that takes an input voltage and outputs either a higher voltage, same voltage or lower voltage to the load. When the output voltage is higher than the input voltage, the DC/DC converter is called a boost converter and when the output voltage is lower than the input voltage the converter is called a buck converter. For this design, an input power of +32V has to be processed into six different low voltages; therefore, the buck converter will be the focus of this section. A simplified version of a buck converter is shown below in figure 3.7.2.1

Figure 3.7.2.1 Simplified schematic of a buck converter

As seen in the figure above, the buck converter consists of the following elements:

- A dc input voltage source Vdc. This is the incoming raw power to the network that has to be conditioned.

- A MOSFET which acts as a controlled switch. The MOSFET is controlled by a driver circuitry.

- A diode set up to provide a path for the current when the MOSFET is opened.

- A filter inductor L and a filter capacitor C. Under the assumption that the inductor current is always positive and never zero, the converter is called the 'continuous conduction mode.'

It can be seen from the circuit above that when the switch is on or the MOSFET is commanded to the on state, the diode D is reverse-biased. When the switch is off, the diode conducts to provide a path for the current in the inductor. Consequently, when the switch is on and current is flowing through the inductor, a positive voltage results across the inductor, VL = Vg-Vo. This voltage causes a linear increase in the inductor current. When the switch is turned off, the current keeps flowing through the inductor because of the energy stored in the magnetic field, and as mentioned before this current flows through the diode until the switch is turned again. By controlling the duty cycle of the on and off states, the output voltage can be controlled with the following equation,  $Vo = D^*Vin$

The equations for the relationships among input voltage, output voltage, duty cycle, and other voltages in the circuit can be derived by solving two circuits which account for the switch being on and off. These equations are available in the literature along with its derivations.

The DC/DC umodule family is a new family created by Linear Technology. The umodule regulator is a complete system integrated in one substrate. The system contains the MOSFET and its controller inside the package. In this family, Linear Technology has incorporated previous designs into one package where efficiency is improved.

The micro-module family falls under the category of High Efficiency dc/dc converters. No doubt efficiency is one of the most important aspects of the application requirements for the power supply; however, there is a requirement that is more important than efficiency and that is the radiated and conductive noise introduced by the module. It is well known that dc/dc converters introduce conductive noise due to the high frequency switching inside the modules and radiated noise is created by the magnetic fields of the inductor used in the circuit. Since the power supply will power a transmitter, the noise requirements are extremely tight. Any noise introduced by the power supply leads to catastrophic effects in the system.

The ultra-low noise devices in the micro-module family have been designed at Linear Technology so that radiated and conducted EMI caused by the device is minimized. In order to achieve reduction in EMI, low pass filters have been incorporated in the modules thus reducing high frequencies that may cause interference with adjacent circuitry. The module has also been designed so that common mode rejection is optimized within the package. The ultra-low noise modules also allow the use of external clocks to drive the converter. This allows the designer to choose spread frequency oscillators. By spreading the frequency, the energy concentrated at the switching frequency can then be spread within a plus or minus 10 percent margin. This is achieved by allowing the clock frequency vary within a margin from the center frequency.

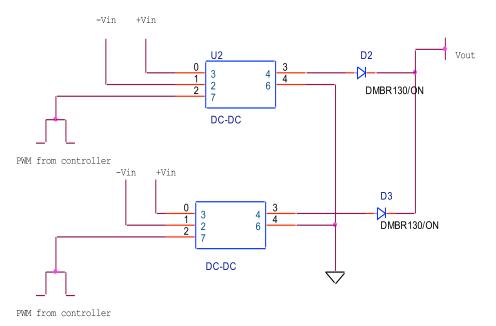

#### 3.7.2.1 Paralleling dc/dc converters

The power supply for the transmitter requires a pulsed current of 11 Amps with a variable frequency that ranges in between 10-100 kHz. In order to obtain efficiencies higher than 90% dc to dc converters have to be implemented. In recent years, with the explosion of laptop computers and portable electronics such as cell-phones a new industry has emerged in low power electronics. This sector contains integrated circuits (ICs) that perform buck and boost topologies leaving the designer with the option of choosing bulky output capacitors, inductors and resistors to meet the design requirements. Typically most small sized dc-dc converter modules only provide a current of 8Amps or less with output voltages of 3.5V. Because of this, paralleling the output of the dc-dc converter is desired in order to boost up the current. However; it is well known that when two sources are paralleled, they must have the same magnitude, phase, and frequency so that there is no potential difference between the two sources. In this application, making sure that the two sources have the same frequency or phase is not a concern since the output of the sources is DC. Thus in order to protect the dc to dc modules; they must have the same magnitude. An easy way to protect the chips in case there is a potential difference between the two sources is to place a diode on the output of the positive lead of each dc-dc converter IC as shown below in Figure 3.7.2.1.1.

Figure 3.7.2.1.1 Simple way of protecting dc/dc modules in parallel mode.

Although the solution presented above works for many small signal applications that is not the case for the high power source to be designed because of the heat created by the diode losses. As stated previously, the current drawn by the load will be a pulsed with a frequency that ranges from 10 kHz to 100 kHz with a peak of 11 amps at 50% duty cycle or less. Therefore, if diodes are placed at the outputs of the dc-dc package, the conduction losses attributed by the diodes will be close to 9 watts plus the switching losses. Because of this, using diodes to protect the chips is not the best solution. Another way to solve this issue is to find a dc to dc package that offers the option of paralleling the outputs.

#### 3.7.2.2 Ripple attenuation

The 6XMIT or the highest power supply of the system is used to drive the transmitter which draws a pulsed current with a peak of 11A and with a duty cycle less than 50 percent. The requirement for the voltage supplied to the load must have a low-ripple-voltage no greater than 1mV. As a result, choosing the right components becomes a critical part of the design. The  $\mu$ Module dc/dc converters family by Linear Technology offers the ability to design a power supply with a specific output voltage ripple and the equations are as follows:

The ripple percentage is typically set to 20% to 40% of the maximum inductor current. As seen in the equation,

*Vripple* = [*Vout* (*Vin* - *Vout*)] / [8 \* L \* *Cout* \* *Vin* \* *f*^2],

the output ripple voltage depends on several variables. The frequency of the device can be set anywhere between 200 kHz-400 kHz. This can be set up in two different ways; one way is to provide a clock signal to the device by connecting it to the INTVcc pin or by applying a voltage that ranges from 0.5 V - 2V to the PLLFLTR Pin, where 0.5V equals 200 kHz and 2V equals 400 kHz. The range in between the two frequencies is linear. The disadvantage of the latter option is that the efficiency of the dc/dc module decreases because power dissipates across the MOSFET in charge of setting up the frequency inside the module. Once the frequency of the dc/dc converter is chosen, the selection of the inductor follows next. The inductance is first found by using the formula above, once the inductor value is known then the proprieties of the inductor have to be considered. An inductor with a low DC resistance is preferred so that the I^2R losses are minimized. Also the inductor must be able to handle the peak inductor current without saturation. To minimize radiated noise, a toroid, pot core or shielded bobbing inductor is preferred.

The input voltage, output voltage and load current have already been assigned. Vin equals 32V, Vout equals 6V and the load current is 11 A. The only variable left out in order to solve for Vripple is the output capacitors. The bulk output capacitors are chosen such as their equivalent series resistance or ESR is as low as possible to meet the output voltage ripple and transient requirements. The most common capacitors used to meet low ripple specs are the low ESR tantalum capacitor, the low ESR polymer capacitor or the ceramic capacitor. In addition, placing the output capacitors in paralleled is optimal due to the fact that these adds more capacitance and lowers the ESR value, the lower the ESR the better. The table below, Table 3.7.2.2.1, provided by Linear Technology shows a matrix of different output voltages and output capacitors to minimize the voltage droop and overshoots at a current transient.

| V <sub>IN</sub><br>(V) | V <sub>out</sub><br>(V) | R <sub>sense</sub><br>(0.5W Rating) | Inductor<br>(µH) | C <sub>in</sub><br>(Ceramic) | C <sub>IN</sub><br>(BULK) | C <sub>out1</sub><br>(Ceramic) | C <sub>OUT2</sub><br>(BULK) | I <sub>out(max)</sub> *<br>(A) |

|------------------------|-------------------------|-------------------------------------|------------------|------------------------------|---------------------------|--------------------------------|-----------------------------|--------------------------------|

| 12                     | 5                       | 2 × 18mΩ 0.5W                       | 2.2              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 12                             |

| 20                     | 5                       | 2 × 18mΩ 0.5W                       | 2.5              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 12                             |

| 24                     | 5                       | 2 × 18mΩ 0.5W                       | 2.5              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 12                             |

| 32                     | 5                       | 2 × 20mΩ 0.5W                       | 3.3              | 2 × 10µF 50V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 10                             |

| 36                     | 5                       | 2 × 20mΩ 0.5W                       | 3.3              | 2 × 10µF 50V                 | 150µF 50V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 10                             |

| 5                      | 8                       | 2 × 16mW 0.5W                       | 1.5              | None                         | 150µF 35V                 | 4 × 22µF 25V                   | 2 × 180µF 16V               | 7                              |

| 12                     | 8                       | 2 × 18mΩ 0.5W                       | 2.2              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 12                             |

| 20                     | 8                       | 2 × 20mW 0.5W                       | 3.3              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 11                             |

| 24                     | 8                       | 2 × 20mΩ 0.5W                       | 3.3              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 11                             |

| 32                     | 8                       | 2 × 20mΩ 0.5W                       | 4.7              | 2 × 10µF 50V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 10                             |

| 36                     | 8                       | $2 \times 22 m\Omega 0.5 W$         | 4.7              | 2 × 10µF 50V                 | 150µF 50V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 10                             |

| 5                      | 10                      | 2 × 16mW 0.5W                       | 2.2              | None                         | 150µF 35V                 | 4 × 22µF 25V                   | 2 × 180µF 16V               | 6                              |

| 15                     | 10                      | 2 × 18mW 0.5W                       | 2.2              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 12                             |

| 20                     | 10                      | 2 × 20mW 0.5W                       | 3.3              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 11                             |

| 24                     | 10                      | 2 × 18mΩ 0.5W                       | 3.3              | 2 × 10µF 25V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 11                             |

| 32                     | 10                      | $2 \times 22 m\Omega 0.5 W$         | 4.7              | 2 × 10µF 50V                 | 150µF 35V                 | 2 × 22µF 25V                   | 2 × 180µF 16V               | 10                             |

# Table 3.7.2.2.1

#### Typical components for different power requirements where f = 400 kHz. (Permission pending from Linear Technology)

#### 3.7.2.3 LTM4607 µModule

The LTM 4607 falls under the category of High Efficiency dc/dc converters of the  $\mu$ Module family. No doubt efficiency is one of the most important aspects of the application requirements for the power supply; however, there is a requirement that is more important than efficiency and that is the radiated and conductive noise introduced by the module. It is well known that dc/dc converters introduce conductive noise due to the high frequency switching inside the modules and radiated noise is created by the magnetic fields of the inductor used in the circuit. Since the power supply will power a transmitter, the noise requirements are extremely tight. Any noise introduced by the power supply leads to catastrophic effects in the system. Therefore, if the LTM4607 ends up being the component selected, an evaluation board has to be acquired in order to learn more about the noise that this module introduces.

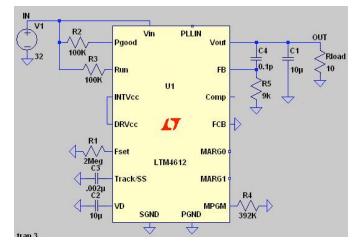

#### 3.7.2.4 LTM4612 uModule

The LTM4612 belongs to the family of 'ultra-low noise' DC/DC converters. It operates with a wide range of input voltages from 5V to 36V and can provide output voltages from 3.3V to 15V set by a single resistor. The maximum continuous current that the module can provide is 5A and the maximum peak

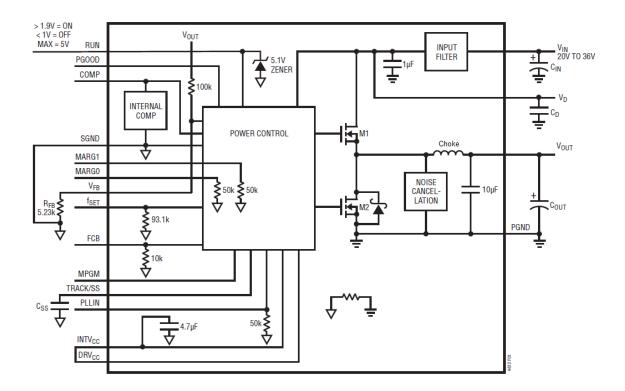

current is 7A. The only components that the designer has to choose are bulk input and output capacitors to finish the design. The output capacitor is chosen to satisfy several requirements. Since capacitors are not ideal, parasitic components have to be taken into account. In general, a capacitor contains an equivalent series resistance or ESR and an equivalent series inductance also known as ESL. The ESR of a capacitor plays a role in the ripple of the output voltage. By referring to the right side of Figure 3.7.2.4.1 below, one can see that the choke will have a ripple current introduced by the switching element.

#### Figure 3.7.2.4.1 Simplified schematic of the LTM4612 module (Permission pending from Linear Technology)

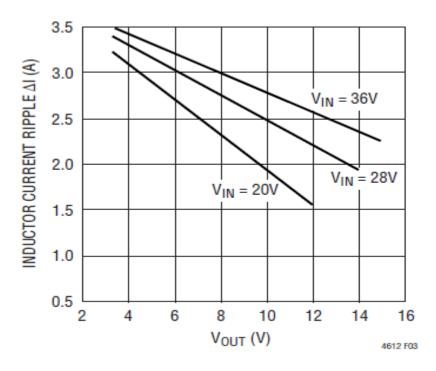

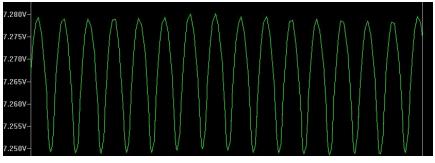

When the switching element turns on, the choke stores energy in its magnetic field. When the switch turns off the choke, it will create a voltage that will try to keep the current flowing as long as there is energy in the magnetic field, according to Lenz's law. This phenomenon creates a high frequency current ripple in the choke where the high frequency is introduced by the switching element. In the Figure 3.7.2.4.2 below, the ripple caused the inductor in the LTM4612 module is shown with respect to the output voltage. In addition, the high ripple current will follow the path with the least resistance which is provided by the output capacitor at high frequencies thereby generating a ripple on the capacitor has to be chosen so that it is as small as possible. Modern low ESR

electrolytic capacitors are now designed for DC/DC applications, and the ESR values are provided by the manufacturers. As far as the ESL is concerned, it can generally be neglected for switching frequencies below 500 kHz.

To be precise, there are two ripples that are introduced by the output capacitor and its equivalent series resistance. They are not in phase because the ripple generated by the ESR is proportional to I2-I1. The ripple due to the output capacitor is proportional to the integral of that current. However, for a worst-case comparison one can make the assumption that they are in phase, hence when they are not in phase the ripple is less.

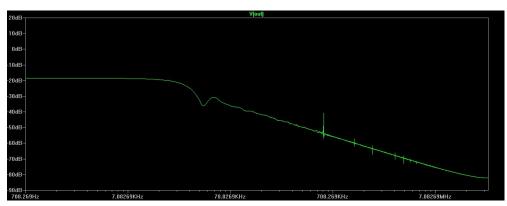

The LTM4612 employs a high switching frequency and an adaptive on-time current mode architecture that enables a very fast transient response to line and load changes without sacrificing stability. It also has an onboard input filter and noise cancellation circuits that achieve low noise coupling which help on reducing the EMI; this is shown in 3.5.2.4. Furthermore, the DC/DC module can be synchronized with an external clock for reducing undesirable frequency and allows poly-phase operation for high load currents. Usually, a spread spectrum oscillator is used as the clock. The frequency of the oscillator is set to a fixed value with the ability to vary within a certain margin, usually plus or minus 10%. By spreading the spectrum, the energy associated with the driver for the switching element is essentially spread within frequencies close to the center

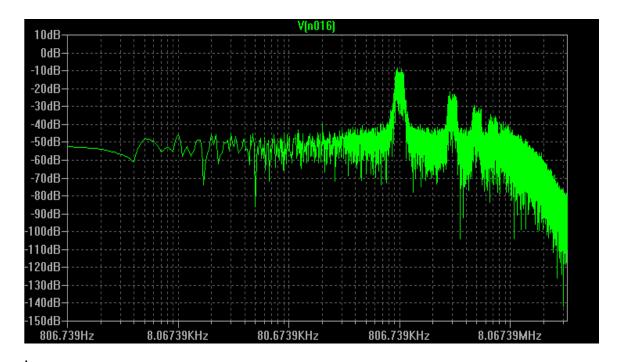

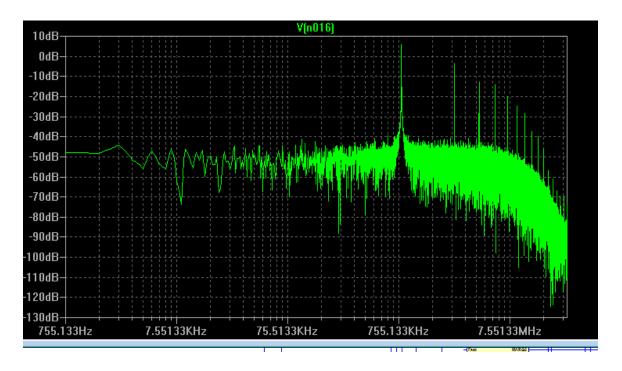

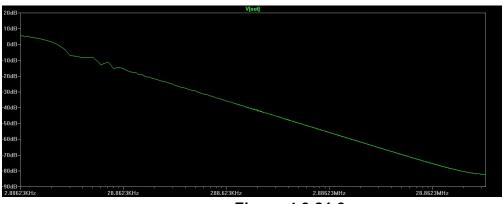

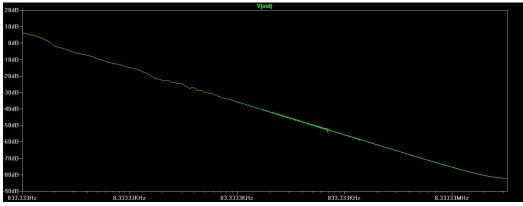

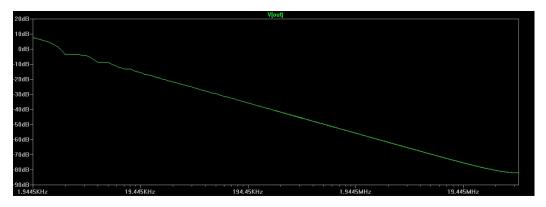

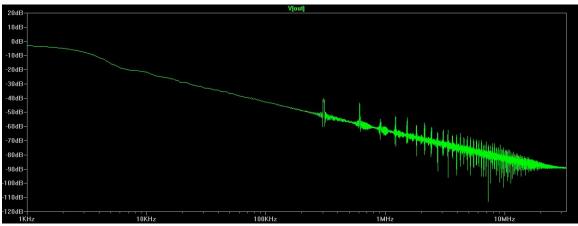

frequency. If the spreading of the spectrum technique is not utilized, all the energy coming from the driver for the switching element is concentrated on the center frequency. Figure 3.5.2.6 and figure 3.5.2.7 below show simulated results where the difference between spreading the spectrum and not spreading the spectrum is clearly seen.

In general, poly-phase operation is desired when dc/dc converters have to output more than the rated current. The LTM4612, just like the LTM4606 gives the designer the option of paralleling the modules for high load currents. Furthermore, the LTM4612 allows the paralleled modules to have very good current sharing because it is a current mode controlled device. The current mode controller limits the cycle by cycle inductor current during transients and steady state operation. The controller also provides a foldback current limiter that limits the current in the event of an overload condition. Additionally, if the output voltage falls by more than 50 percent, then the maximum output current is progressively lowered to about one sixth of its full current limit value. The output voltage on the LTM4612 is set by using the equation below.

Vout = 0.6V [(100k/N) + (Rfb)] / [Rfb]

Figure 3.7.2.4.3 Frequency spectrum of the clock signal for the LTM4612 utilizing the spread spectrum technique.

Figure 3.7.2.4.4. Spectrum of clock when the spreading spectrum technique is not used

The figures above clearly show that more energy is concentrated at the switching frequency when the spreading spectrum technique is not implemented. One drawback that could result from having a lot of energy concentrated at one point is EMI. Thus, in order to prevent EMI, a device that spreads the spectrum should be considered in the design phase.

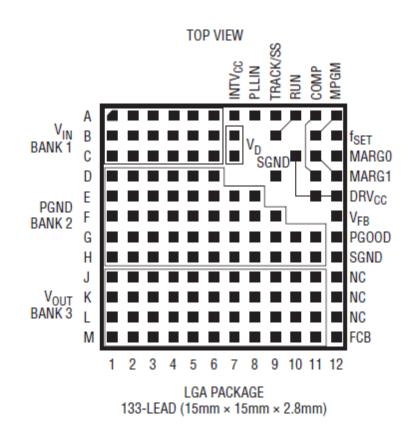

#### 3.7.2.5 LTM4612 Pins

Knowing the pins of the device will expedite both the simulation and design process. As a result, the purpose of this section is to describe the different pins and its functions. All the pins are shown in Figure 3.7.2.5.1 below. Directly below are the pin functions.

VIN: The source is connected across this pin and GND. It is recommended the placement of decoupling capacitance between this pin and GND.

PGND: Power ground pins for input and output returns. It is important to note here that the LTM4612 does not provide isolation; therefore, an internal slow blow fuse should be added in the circuit to protect the unit from catastrophic failure.

Vout: The load is connected across this pin and PGND. It is recommended to place decoupling capacitance across this pin and PGND. It should be connected as close to the pins as possible.

Vd (pins B7, C7): Top FET drain pins. Adding more capacitors between this pin and PGND will reduce the input ripple to the module.

DRVcc(Pins C10, E11, E12): Usually these pins are connected to INTVcc for powering the internal MOSFET drivers. An internal low dropout regulator produces an internal 5V supply that powers the control circuitry and DRVcc, equation 3 calculates the power dissipated by the regulator. The power dissipated with the 32V input voltage is 0.54W. Therefore, this pin should be biased with an external voltage no greater than 6V and 50mA to improve the efficiency of the unit. By doing this, the losses will be 20mA\*5V which equals 0.1W as opposed to 0.54W.

*Ploss* = 20*mA* \* (*Vin* - 5*V*)..... equation 3

INTVcc(Pin A7): This pin is for additional decoupling of the 5V internal regulator.

Figure 3.7.2.5.1 LTM4612 Pin configuration. Linear Technology LTM4612 Datasheet.

PLLIN (Pin A8): This pin gives the designer the option of using external clock synchronization to the phase detector. The LTM4612 has a phase-locked loop

comprised of an internal voltage controlled oscillator and a phase detector. This allows the internal top MOSFET turn-on to be locked to the rising edge of the external clock. The frequency range is +- 30% around the set operating frequency. A pulse detection circuit is used to detect a clock on the PLLIN pin to turn on the phase-locked loop.

FCB: This pin forces continuous mode operation when connected to PGND or discontinuous mode operation when connected to INTVcc.

Track/SS (pin A9): One of the requirements on this design is power sequencing. By placing a capacitor across the Track pin and PGND the ramp rate can controlled. A soft start capacitor can be used for soft start turn on as a standalone regulator. In addition, output voltage tracking can be programmed externally using this pin. The output can be tracked up and down with another regulator. The master regulator's output is divided down with an external resistor divider that is the same as the slave regulator's feedback divider.

MPGM (Pins A12, B11): Programmable Margining Input. A resistor from these pins to ground sets a current that is equal to 1.18V/R. This current multiplied by 10k will equal a value in millivolts that is a percentage of the 0.6V reference voltage. When paralleling two modules, the MPGM pin requires an individual resistor.

RUN (Pins A10, B9): Run Control Pins. A voltage above 1.9V will turn on the module, and below 1V will turn off the module. A programmable UVLO function can be accomplished with a resistor from VIN to this pin that is has a 5.1V zener to ground. Maximum pin voltage is 5V. The run pin will make the down power sequencing easier because the only thing that the FPGA has to do is send a low signal to the pin in order to shut off the module.

PGOOD (Pin G12): Output Voltage Power Good Indicator. Open-drain logic output is pulled to ground when the output voltage is not within +- 10% of the regulation point. This occurs after a 25µs power bad mask timer expires.

SGND (Pins D9, H12): Signal Ground Pins. These pins connect to PGND at output capacitor point.

Comp pin: The comp pin is the external compensation pin. Although the module has already been internally compensated for most output voltages, this pin provides the designer more options for optimizing the control loop.

FSET (Pin B12): Frequency Set Internally to 850 kHz at 12V Output. An external resistor can be placed from this pin to ground to increase frequency. This pin can be decoupled with a 1000pF capacitor.

VFB (Pin F12): The Negative Input of the Error Amplifier. Internally, this pin is connected to VOUT with a 100k precision resistor. Different output voltages can be programmed with an additional resistor between the VFB and SGND pins.

#### 3.7.2.6 LTM4612 Summary

The LTM4612 is a standalone non-isolated DC/DC power module. It is able to deliver up to 5A of continuous current and a maximum peak current of 7 A. This is accomplished with the help of external input and output capacitors. The input capacitors reduced the incoming ripple from the source. In this application, input capacitors will not be a major concern because the source provided to the power supply has a low ripple of 100uV. The module also provides precisely regulated output voltage which is programmable by a single resistor, Rfb. As mentioned previously, the LTM4612 has an integrated constant on-time current mode regulator with FETs that have ultralow Rds on, thereby improving the efficiency at high loads. The typical switching frequency of the module is 850 kHz at full load. The internal feedback loop compensation gives the LTM4612 sufficient stability margins and good transient performance under a wide range of operating conditions. The LTM4612 also belongs to the family of ultra-low noise switching power modules. It provides internal filters and noise cancelling circuits that achieve low noise coupling.

Current mode control provides cycle by cycle current limiting. In case an overcurrent occurs, the LTM4612 provides protection circuitry. Internal overvoltage and undervoltage comparators pull the open drain PGOOD output low if the output feedback voltage is within a +- 10% margin. If an output overvoltage exists, the internal FET M1 is turned off and the FET M2 is held on until the overvoltage is cleared. Figure 3.7.2.4.1 shows the location of M1 and M2 Pulling the RUN pin below 1V forces the controller into its shutdown state by turning off both M1 and M2. The RUN pin will facilitate the power sequencing algorithm set by the FPGA.

To make the LTM4612 more efficient, the DRVcc should be connected to an external 5V external bias supply. By doing this, efficiency improvement will occur due to the reduced power loss in the internal linear regulator. Since the input voltage to the module is relatively high, biasing the DRVcc should be considered. If the DRVcc is not biased with an external source, then pins INTVcc and DRVcc have to be connected. This will trigger the internal 5V linear regulator that is in charge of powering the internal gate drivers.

Overall, the LTM4612 provides all the characteristics needed for the design of the high power module mainly because of its ultralow noise characteristics as well as its capability of accepting high input voltages. Furthermore, the ability of connect as many modules as desired makes this device the perfect choice for the high power supply. Its current mode controller and protections are also a great feature to have because it reduces the need of extra circuitry in the PCB. All

these features plus being a module designed for low output voltage ripple makes the LTM4612 a great choice.

#### 3.8 Positive to Negative Voltage Converter

As the name implies, this device takes a positive input and outputs a negative voltage. A positive to negative voltage converter can be a buck-boost switching power supply. A buck-boost converter creates a negative voltage by canceling out the oscillations produced in the process. A negative impedance is created in result, thus getting a negative voltage.

# 3.9 Ripple Attenuator

A ripple attenuator can be used when a device outputs ripple voltage higher than tolerances in the design allow. The device takes the AC noise of the DC signal out. The noise of the signal must be known to select the proper attenuator. The specifications are given by specifying the noise of a certain frequency range. The ripple attenuator must be rated for a specific frequency range.

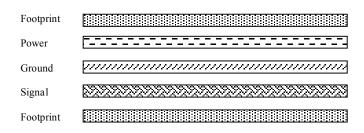

# 3.10 PCB Layout and Topology

The PCB layout is the design of the physical circuit board. There are methods for mounting parts on the board, and there are methods for routing the wire to interconnect every part in the circuit. Often, the board consists for several layers of different material. Top and bottom layers have the footprints of the parts. The footprint consists of the actual solder points for a part. The layers in between will function as the ground plane, power plane, or signal layer. The layers must be in proper order in order to avoid unwanted short circuits or open circuits. The diagram below, Figure 3.10.1, does not in any way reflect the proper layer stack-up. It just demonstrates the layers needed in a PCB layout.

Figure 3.10.1 PCB Layout

It is imperative to consider the amount of current running through wire traces. The wire traces will have to be a certain width corresponding with the amount of current. The width and length of the traces are crucial. Depending on the amount of current flowing through the trace will determine the width. The length should be as short as possible to eliminate losses. Higher current such as 10 amps would require a width of about 500 mils. For lower current such as 100mA would require a width of about 1 mil. Often, 1 layer will be dedicated to high power signals. To avoid crosstalk, traces must not run too close together. Layer to layer signals should be perpendicular, they must not run parallel to each other either to avoid EMI problems. The diagram below, Figure 3.10.2, shows how the traces must be laid out from layer to layer.

Figure 3.10.2 Perpendicular traces

Thermal conditions must also be considered. Certain parts may need to be laid out in a specific area of the board. When installing and soldering a part, high heat on another part nearby may be harmful. Through-hole and surface mounted parts are a large consideration in topology. The through-hole parts produce more heat and take more space. However, the surface mounted parts are more expensive.

# 3.11 Filtering

Capacitors have a fundamental function in the design of a circuit. They will filter the signal for a desire input or output. For example, the input signal to a linear regulator from a switching power supply would, normally, be a ramp function. However, there must be a constant signal. The capacitors would produce this desired function with the correct capacitance values. Capacitors will provide instant power when the switch is closed. Depending on the application this may be desirable. Turbo Caps from TTI are a new solution to saving valuable space on the printed wiring board (PWB). These capacitors can be vertically stacked. These ceramic capacitors are ideal for filtering both input and output of switching power supplies. They can handle high current at high frequencies and high power. Also, they can handle operating temperatures from -55 degrees Celsius to +85 degrees Celsius. Of course, this type of capacitor can handle high frequencies, but, often, the capacitance is lost at RF frequencies. They do not handle AC signals either between of the constant switching. Capacitors can introduce unnecessary inductance to the circuit. At extreme high temperatures and extreme low temperatures, they can lose capacitance. Most sensitive type of capacitor is the electrolytic capacitor. Capacitors are also often used to eliminate ripple voltage on the power lines. The capacitor is also used to place between power and ground. These are referred to as decoupling capacitors. This is a fail proof way of isolating power from ground.

# 3.12 Analog to Digital Signals

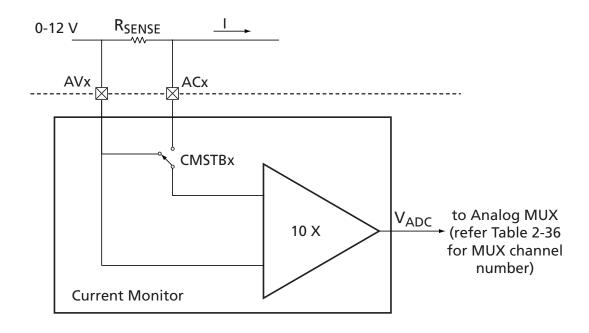

Voltage supervisor is an IC used to monitor the output of a device. Logic high will output if the set voltage is reached. If the device does not output the correct voltage a logic low will be send to the output. The input voltage is compared to the reference voltage usually implemented by using a voltage divider. The IC gives a simple method to monitor low voltages. Many times the output from the voltage supervisor can be sent to an FPGA.

Analog to digital converters (ADC) will take an actual analog signal and convert it to a digital signal where a device can process the signal, such as a FPGA or microcontroller. The FPGA or microcontroller is set or programmed by the engineer to translate the digital signals. One of the most important parameters of an ADC is choosing the resolution of its output. There is 2^N combinations, N being the bit amount. The higher the resolution the greater accuracy of the digital signal sent to the FPGA or microcontroller.

#### 3.13 RoHS Compliant

There is a continuing struggle with tin whiskers. The tin whisker phenomenon has been a problem since the 1940s where electrical equipment made with cadmium, tin or aluminum grow what looks like metal whiskers. This is serious threat to the equipment because it can create shorts between parts that are near each other. However, it had been found that if lead is mixed with any of the common metals used, cadmium, tin, and aluminum that this phenomenon can be prevented. This saves the electronics from potential failure and thus compromising people's safety also. There is a grave problem with this issue. As lead can be harmful to humans and the environment, countries around the world are working towards enforcing laws that will prevent the manufacturing of electronics with lead. The argument remains, though, that lead is also preventing potential accidents if the electrical equipment fail. The European Union has already passed legislation called the Restriction of Hazardous Substances, or RoHs restrictions. These are restrictions on the use of hazardous materials. This legislation will affect companies around the world because they will either have to not sell to EU or find alternative materials to manufacture their product without having to compromise the risk of tin whisker. Also, not all industries are required to abide by the regulations including military. However, there lies the risk of companies swaying away completely from lead products which the military needs to operate electronics for many years. In this project it is necessary to find parts that are still made with lead.

#### 3.14 Trade Studies

The high current signal requires more power and has less tolerance for ripple voltage than the low current signals. This signal can be treated differently in the design. Switching power supplies and pre-regulator modules (PRM) with voltage-

transformation module (VTM) handle high power signals. PRM/VTM take up physical space on the board.

The LTM4612 was compared and contrasted to the LTM 4606 and LTM8022. LTM 4606 and LTM 4612 were both considered for the switching power supply. They are rated for low EMI and low ripple voltage. However, the LTM 4612 and LTM 8022 met specifications for input and output voltage. EMI was strongest between 150MHz to 250 MHz for both the LTM 4606 and 4612. The screenshots capture the EMI results for both switching power supplies. The LTM 4612 exhibited the best results because there is minimal disturbance when compared to the reference screenshot. There is about a 5-db difference in noise, or the EMI noise in the LTM 4606 is about 3 times higher. The EMI was measured when power was off to use as a reference to compare the EMI when the part was on. The diagrams below, Figures 3.7.1-3.7.4 show the EMI present around the part when the part is on and off.

Figure 3.9.1 Reference. No power applied to LTM 4612.

Figure 3.9.3 Reference. No power applied to LTM 4606

Power applied to LTM 4606.

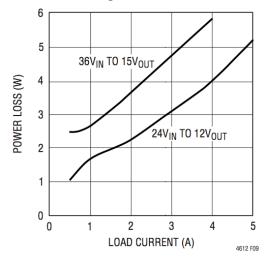

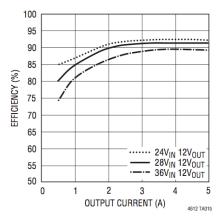

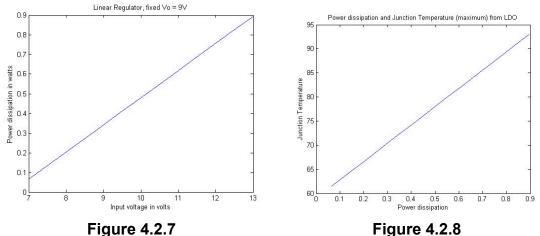

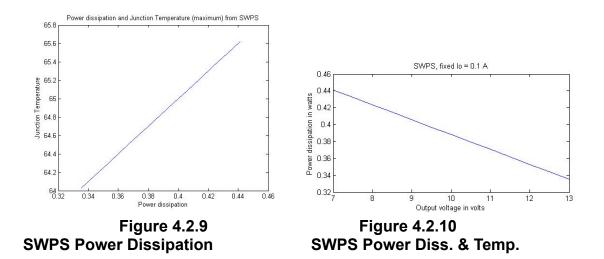

Both the LTM 4612 and LTM 8022 have maximum junction temperature of 125 degrees celsius. The junction to ambient temperature for LTM 8022 is 24 degrees celsius per 1 watt. However, the junction to ambient temperature for the LTM 4612 is 14.9 degrees per 1 watt. LTM 4612 has a better temperature rating for the amount of output power generated. Since there is no airflow the

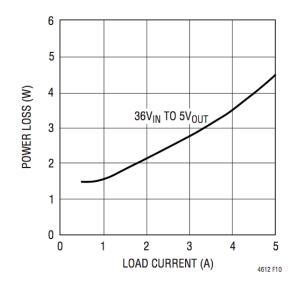

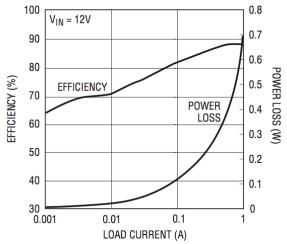

junction-to-ambient temperature is an imperative parameter to consider. The following figures display the estimated power loss for specific input and output voltages for the LTM 4612 and LTM 8022. The low current signal lines will not generate much power. Both have relatively low power output. Also, LTM 8022 could only handle a maximum of 1 amp. Therefore, junction-to-ambient power was a strong factor in choosing the LTM 4612 over the LTM 8022.

Figure 3.9.5 Linear Technology. LTM 4612 Datasheet. Power loss for 12Vout and 15Vout.

Figure 3.9.6. Linear Technology. LTM 4612 Datasheet. Power loss for 5Vout.

#### Efficiency and Power Loss

Figure 3.9.7 . Linear Technology. LTM 4612 Datasheet. Efficiency and Power Loss.

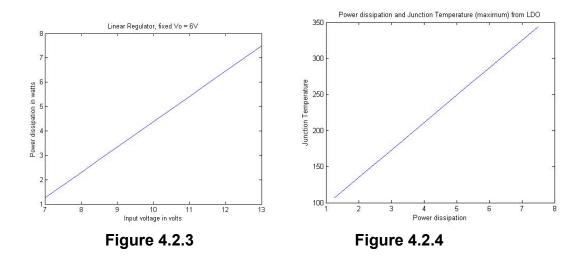

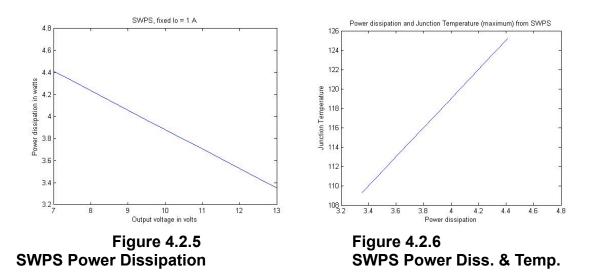

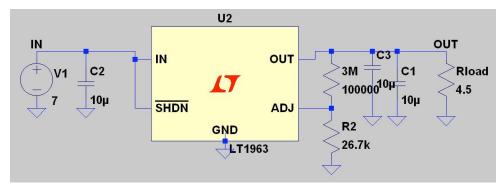

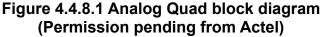

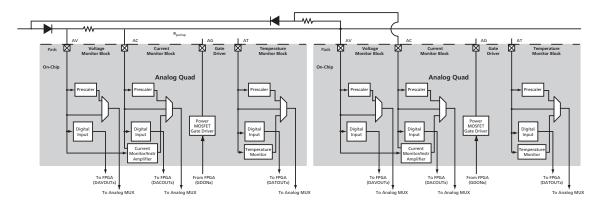

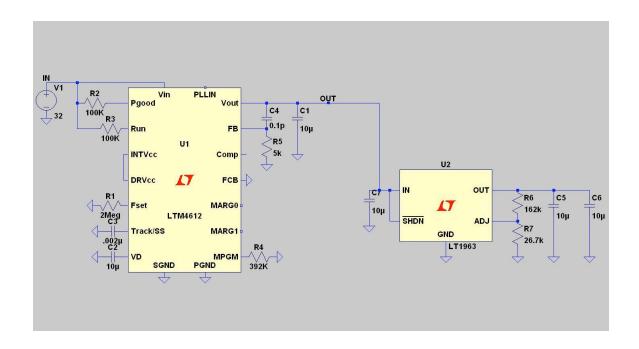

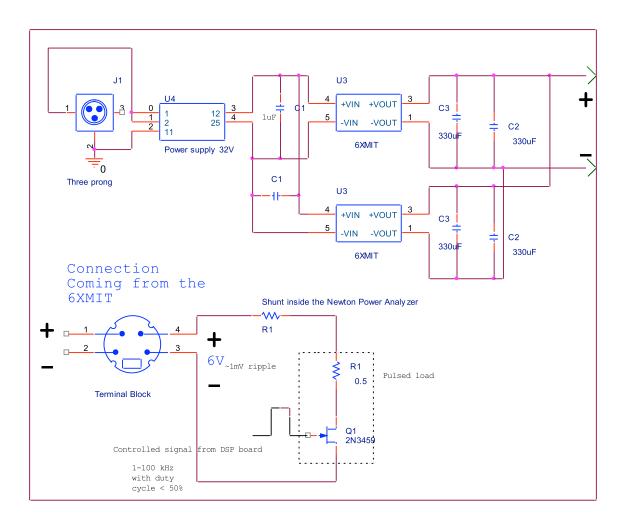

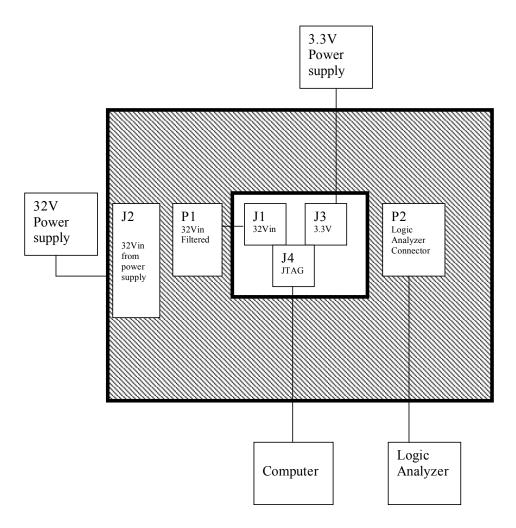

Many companies did not offer linear regulators that handle the temperature range called for by the customer, which is -55 degrees Celsius to +85 degrees Celsius. Another main issue was the output current. If the output current from the specifications was not met, then the potential of putting two linear regulators in parallel had to be considered. There are only specific parts that can be put in this configuration. The LTM1963 from Linear Technology was the only part that could be found to meet specifications.