## **CHAPTER 18**

# CIRCUITS FOR ARITHMETIC OPERATIONS

#### This chapter in the book includes:

Objectives Study Guide

- 18.1 Serial Adder with Accumulator

- 18.2 Design of a Parallel Multiplier

- 18.3 Design of a Binary Divider Programmed Exercises Problems

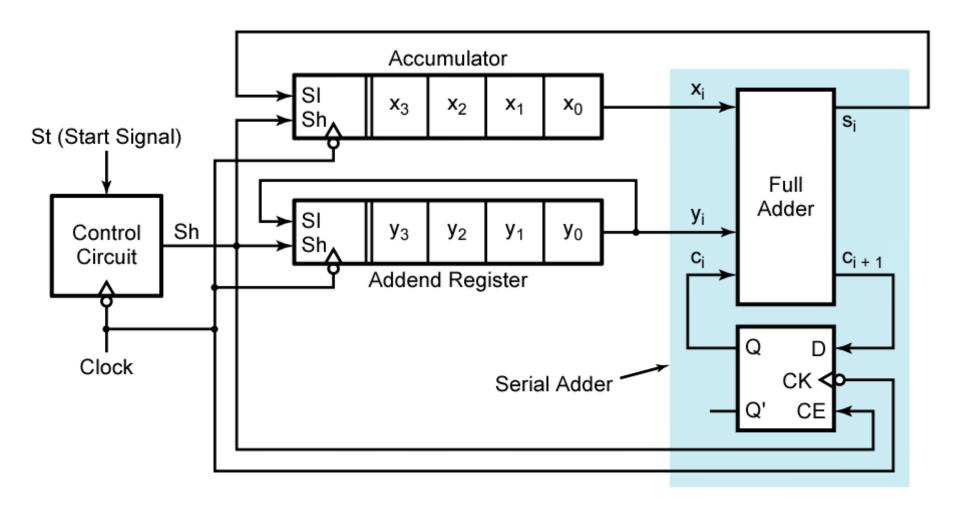

Figure 18-1: Block Diagram for Serial Adder with Accumulator

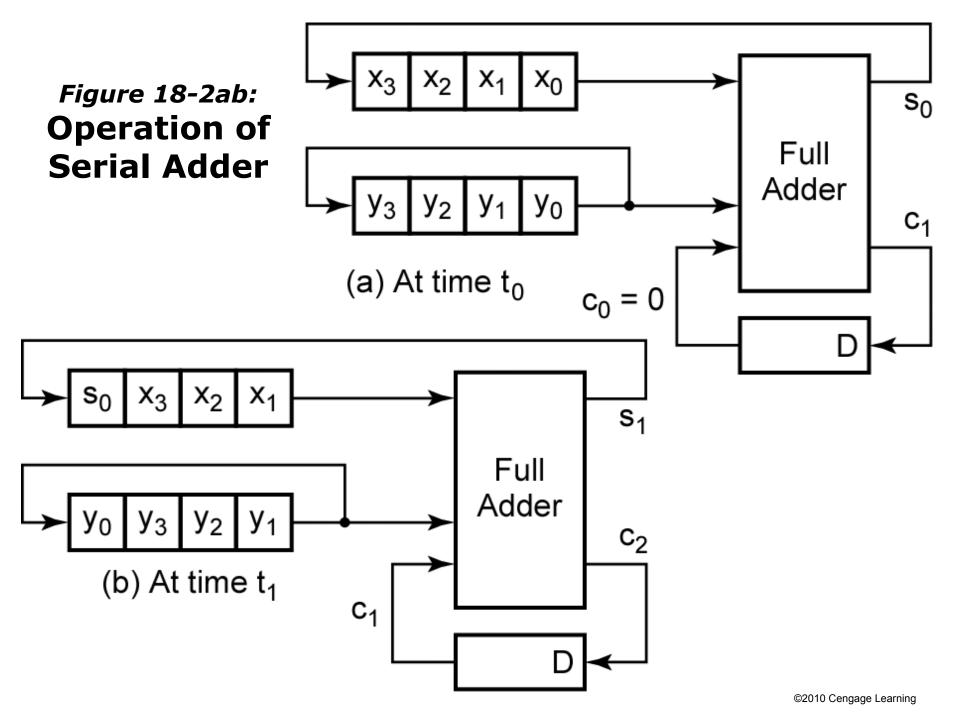

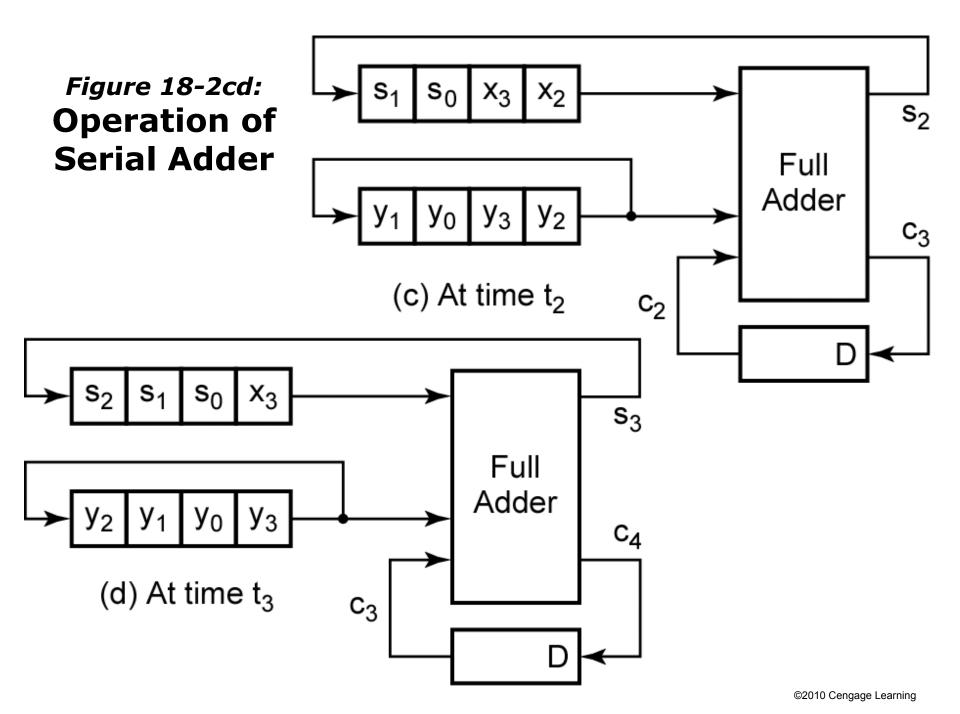

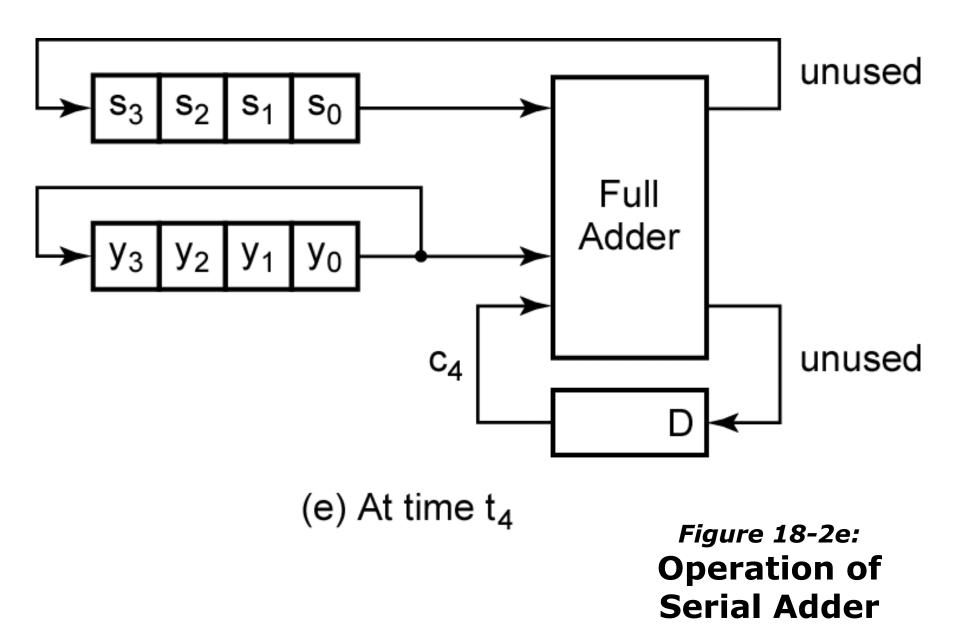

#### **Table 18-1 Operation of Serial Adder**

|                  | X    | Y    | $C_i$ | $S_i$ | $C_i^+$ |

|------------------|------|------|-------|-------|---------|

| $\overline{t_0}$ | 0101 | 0111 | 0     | 0     | 1       |

| $t_1$            | 0010 | 1011 | 1     | 0     | 1       |

| $t_2$            | 0001 | 1101 | 1     | 1     | 1       |

| $t_3$            | 1000 | 1110 | 1     | 1     | 0       |

| $t_4$            | 1100 | 0111 | 0     | (1)   | (0)     |

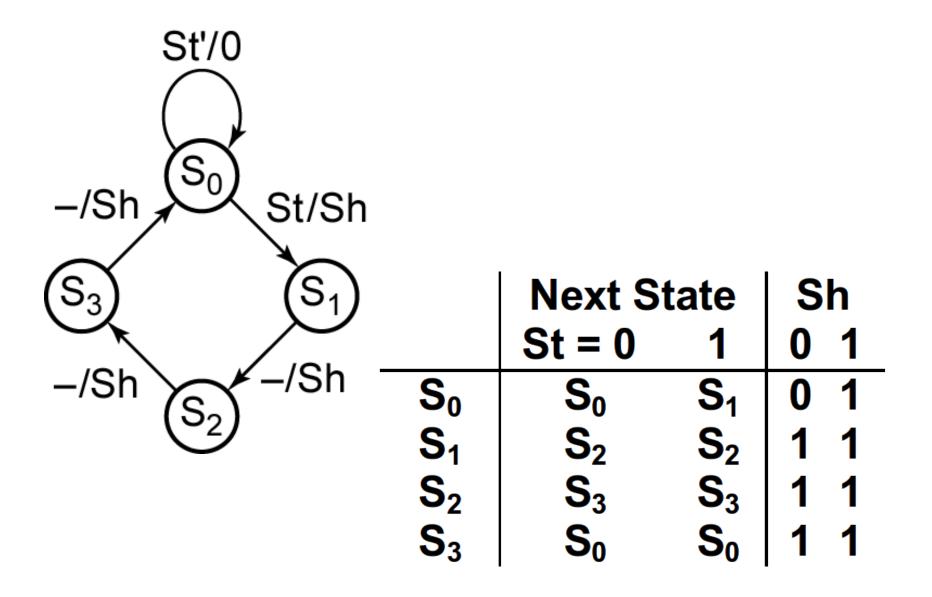

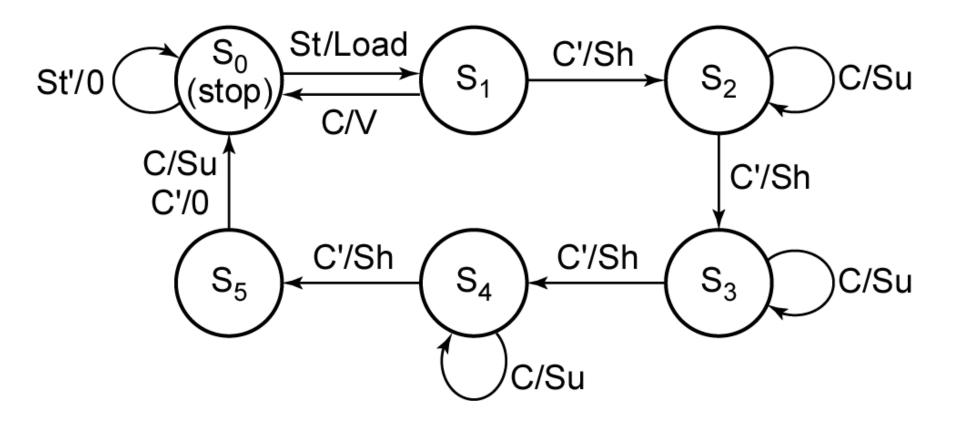

Figure 18-3: State Graph for Serial Adder Control

|                | AB | $A^{\dagger}B^{\dagger}$ |    |  |  |

|----------------|----|--------------------------|----|--|--|

|                |    | 0                        | 1  |  |  |

| S <sub>0</sub> | 00 | 00                       | 01 |  |  |

| $S_0$<br>$S_1$ | 01 | 10                       | 10 |  |  |

| $S_2$          | 10 | 11                       | 11 |  |  |

| $S_3$          | 11 | 00                       | 00 |  |  |

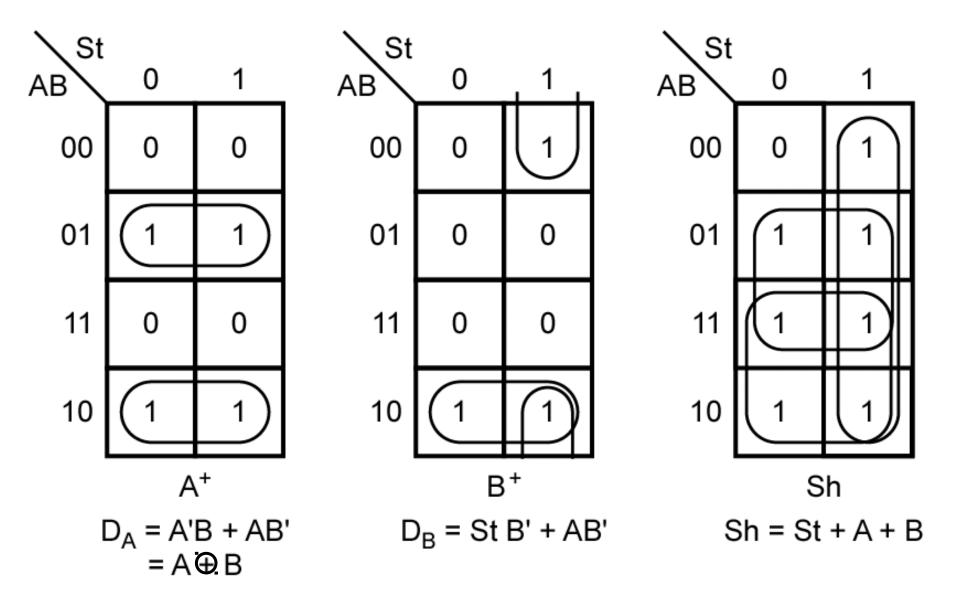

Figure 18-4a: Derivation of Control Circuit Equations

Figure 18-4b: Derivation of Control Circuit Equations

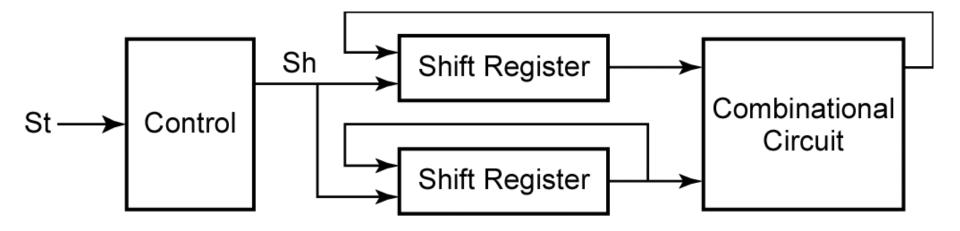

Figure 18-5: Typical Serial Processing Unit

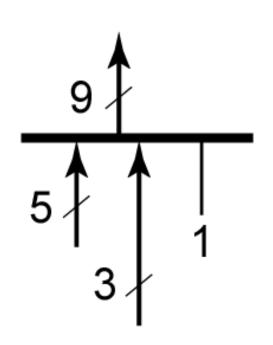

The output bits from the shift register are inputs to a combinational circuit.

The combinational circuit generates at least one output bit which is fed into the input of a shift register.

When the active clock edge occurs, this bit is stored in the first bit of the shift register at the same time the register bits are shifted to the right.

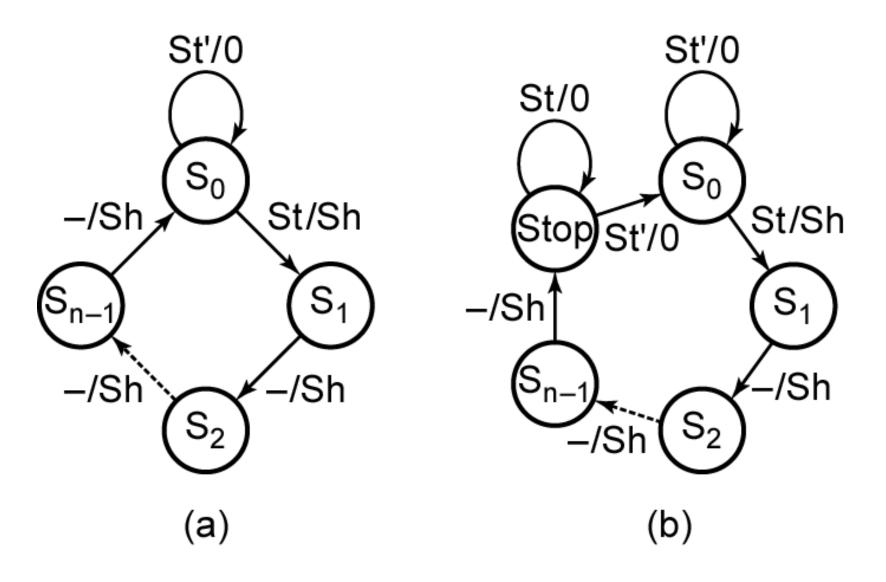

Figure 18-6: State Graphs for Serial Processing Unit

#### **Design of Parallel Multiplier**

Multiplication with partial products added in as soon as they are formed:

Multiplicand

$$\longrightarrow$$

1101 (13)

Multiplier  $\longrightarrow$  1011 (11)

Partial Products  $\longrightarrow$  1000111

Product  $\longrightarrow$  10001111 (143)

**Section 18.2 (p. 598)**

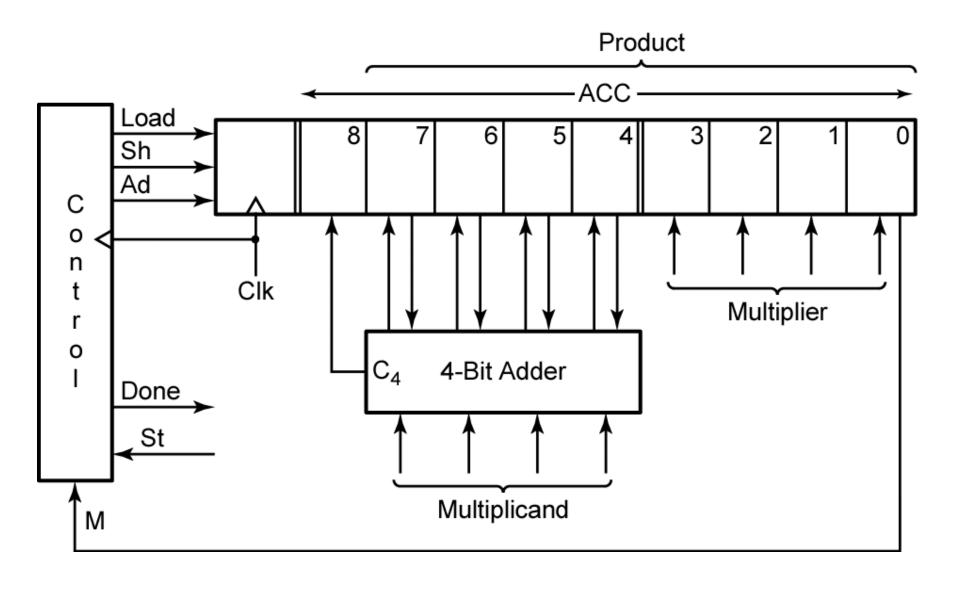

Figure 18-7: Block Diagram for Parallel Binary Multiplier

#### **Parallel Binary Multiplication**

initial contents of product register (add multiplicand because

$$M=1$$

) (after addition (add multiplicand because  $M=1$ ) (add multiplicand because  $M=1$ ) (add multiplicand because  $M=1$ ) (after shift (add multiplicand because  $M=1$ ) (after shift (add multiplicand because  $M=1$ ) (add multiplicand b

**Section 18.2 (p. 600)**

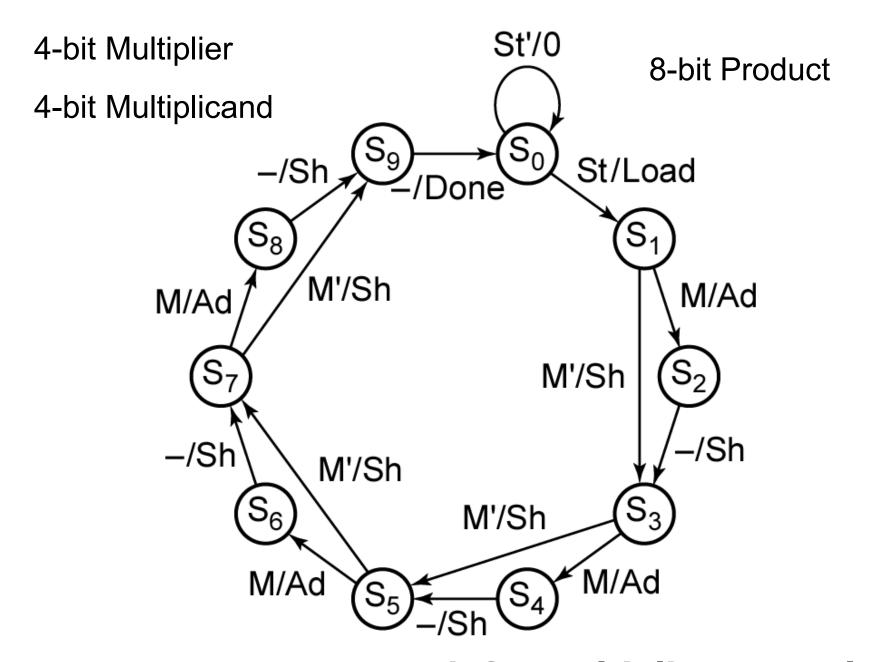

Figure 18-8: State Graph for Multiplier Control

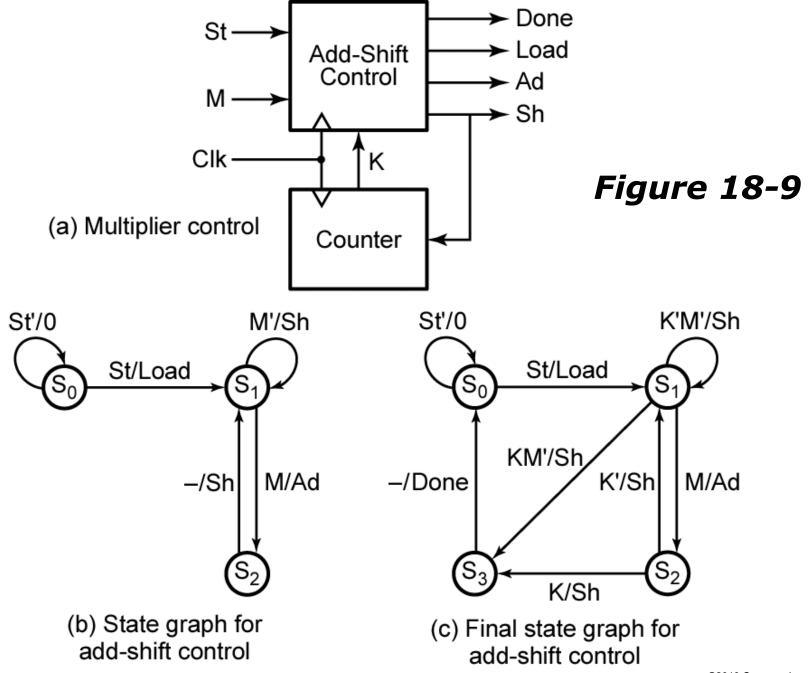

Table 18.2 Operation of a Multiplier Using a Counter

| Time                  | State          | Counter | Product<br>Register | St | M | K | Load | Ad | Sh | Done |

|-----------------------|----------------|---------|---------------------|----|---|---|------|----|----|------|

| $\overline{t_0}$      | S <sub>0</sub> | 00      | 00000000            | 0  | 0 | 0 | 0    | 0  | 0  | 0    |

| t <sub>1</sub>        | So             | 00      | 00000000            | 1  | 0 | 0 | 1    | 0  | 0  | 0    |

| $t_2$                 | $S_1$          | 00      | 000001011           | 0  | 1 | 0 | 0    | 1  | 0  | 0    |

| $t_3$                 | $S_2$          | 00      | 011011011           | 0  | 1 | 0 | 0    | 0  | 1  | 0    |

| $t_4$                 | $S_1$          | 01      | 001101101           | 0  | 1 | 0 | 0    | 1  | 0  | 0    |

| $t_5$                 | $S_2$          | 01      | 100111101           | 0  | 1 | 0 | 0    | 0  | 1  | 0    |

| $t_6$                 | $S_1$          | 10      | 010011110           | 0  | 0 | 0 | 0    | 0  | 1  | 0    |

| <b>t</b> <sub>7</sub> | $S_1$          | 11      | 001001111           | 0  | 1 | 1 | 0    | 1  | 0  | 0    |

| t <sub>8</sub>        | $S_2$          | 11      | 100011111           | 0  | 1 | 1 | 0    | 0  | 1  | 0    |

| t <sub>9</sub>        | $S_3$          | 00      | 010001111           | 0  | 1 | 0 | 0    | 0  | 0  | 1    |

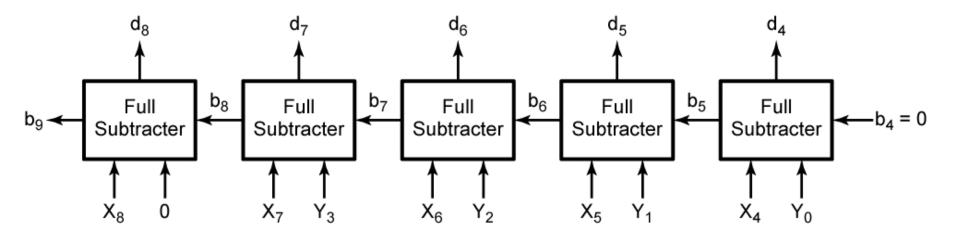

### **Design of Binary Divider**

Example of division process:

divisor

$$101$$

$10000111$  dividend  $1101$   $0111$   $0000$   $1111$   $0000$   $1111$   $0000$   $1111$  a remainder of 5)  $10000$   $0101$   $0000$   $0101$  remainder

**Section 18.3 (p. 602)**

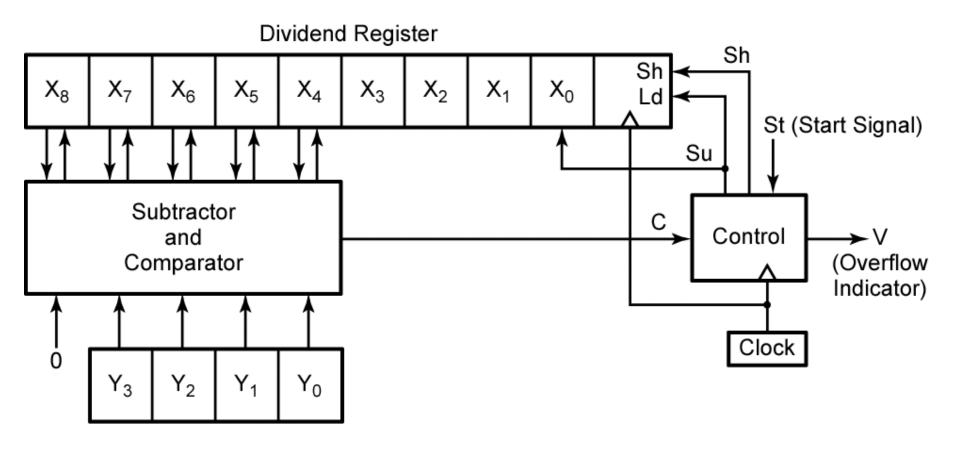

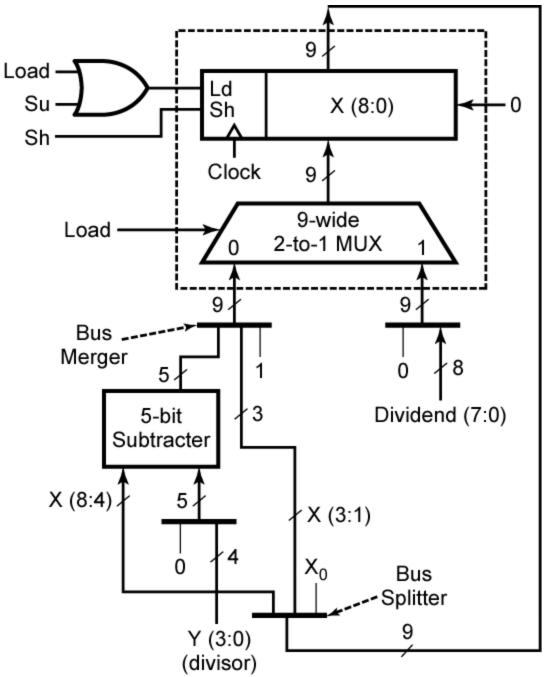

Figure 18-10: Block Diagram for Parallel Binary Divider

```

C = 0, Shift

C = 1, Subtract

Shift

C = 0, Shift

C = 1, Subtract

Shift

quotient

remainder

```

Figure 18-11: State Graph for Divider Control Circuit

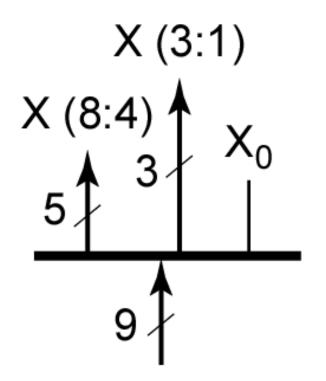

Bus Merger

**Bus Splitter**

**Section 18.3 (p. 606)**

Figure 18-12: Logic Diagram for 5-Bit Subtracter

Figure 18-13:

Block Diagram for Divider Using Bus Notation